針對同一線路上共享電源和數據,目前有多種標準,包括針對數據線供電(PoDL)的IEEE 802.3bu,以及針對以太網供電(PoE)的IEEE 802.3af,采用帶有專用電源接口控制器。這些定義的標準通過檢測、連接檢查、分類和開/關故障監測,提供了受控的安全電源連接。在安全供電情況下,功率水平范圍為幾瓦至幾十瓦。

與適用于廣泛應用的標準化PoE/PoDL規范相反,術語"工程電源(EP)"是指定制的數據線供電設計,通常用于單個應用。例如,針對電機控制編碼器應用,Hiperface DSL規范1將電源和數據耦合至同一線路。工程電源還可用于一些現代傳感器系統中。

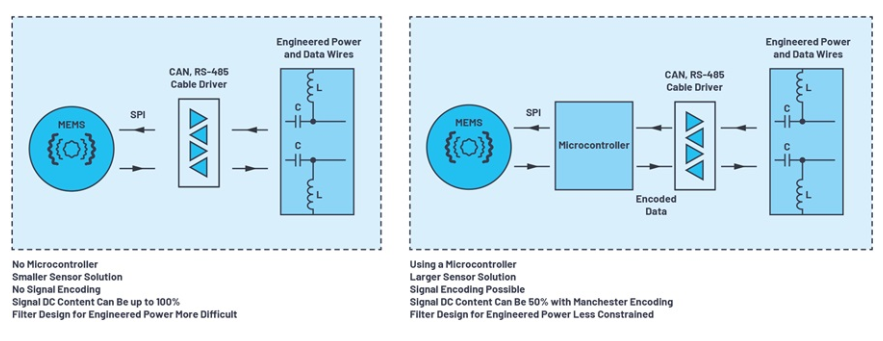

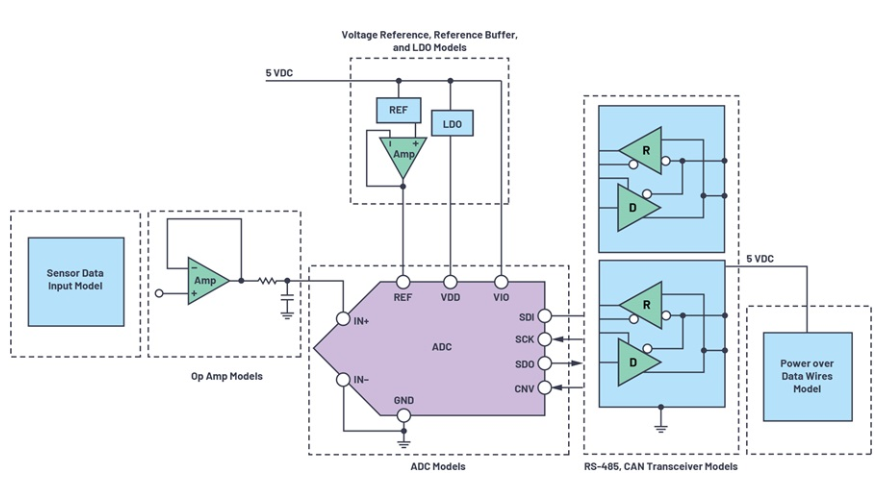

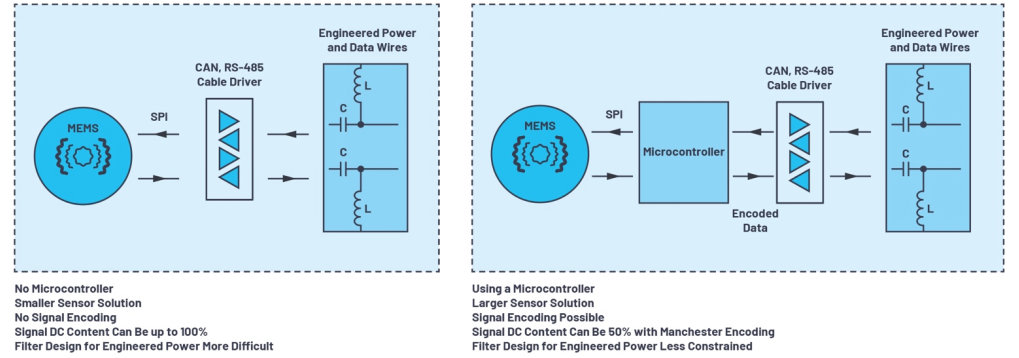

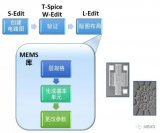

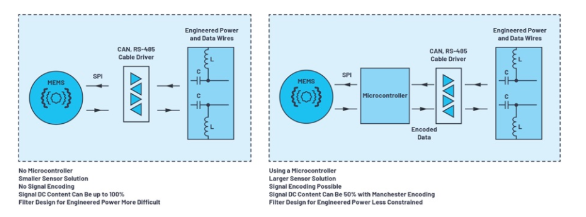

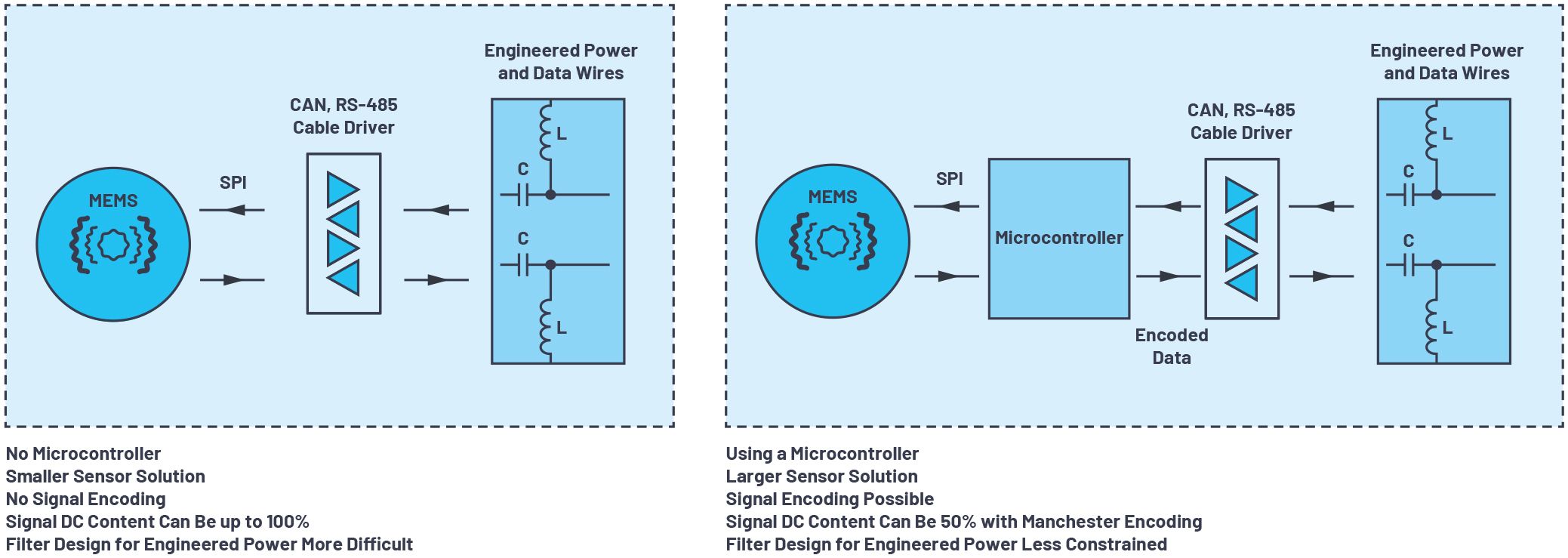

一般的共享電源和數據接口經過編碼,可減少信號直流成分,從而在發送交流信號成分時簡化系統設計。但是,許多數字輸出傳感器接口(例如,SPI和I2C)尚未經過編碼,具有可變的信號直流成分,因此不是共享數據和電源設計的自然之選。對SPI或I2C進行編碼需要額外的微控制器,這會增加解決方案的成本和尺寸,如圖1所示。為了免去編碼和額外增加微控制器的麻煩,設計人員必須嘗試采用多快好省的辦法,這就需要仔細設計和模擬工程電源電路。工程電源電路由電感、電容和保護電路組成,一起構成了一個濾波器。

圖1. MEMS傳感器的潛在工程電源解決方案,在傳感器解決方案尺寸和設計復雜性方面進行了權衡。

工程電源背景

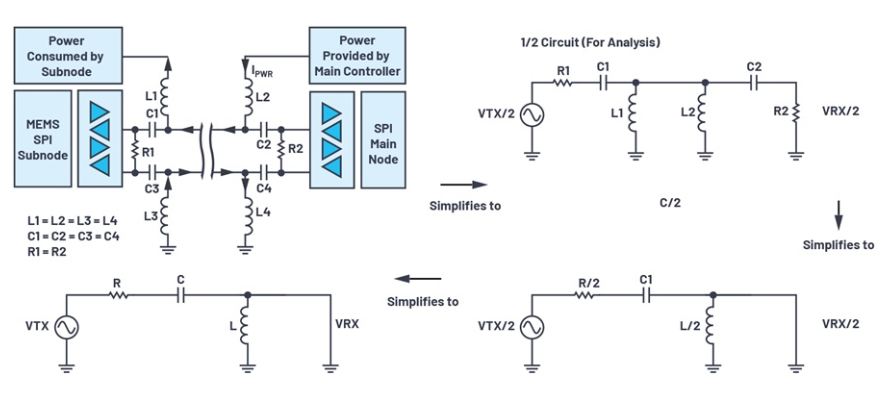

功率和數據通過電感電容網絡分布在一對電線上。高頻數據通過串聯電容與數據線路耦合,同時保護通信收發器免受直流母線電壓影響。主控制器上的電源通過電感器連接到數據線路,然后使用電纜遠端的子節點傳感器節點上的電感器進行濾波。

電感電容網絡將產生高通濾波器,因此耦合解決方案必須添加到不需要直流數據成分的數據線上。但是,有些接口未在物理層進行編碼以去除直流成分,例如,SPI。在這種情況下,系統設計人員需考慮最壞情況的直流成分場景,即數據幀中發送的所有位均為邏輯高電平(100% 直流成分)。所選的電感還將具有指定的自諧振頻率(SRF),超過該頻率時,電感值會下降,寄生電容會增加。這樣,工程電源電路將同時充當低通和高通濾波器(帶通)。基于模擬的建模可大大幫助系統設計人員了解該限制。

長距離移植SPI時,電纜和元件會影響系統時鐘和數據同步。可能的最大SPI時鐘基于系統傳輸延遲設置,包括電纜傳輸延遲,以及主節點和子節點元件傳輸延遲。

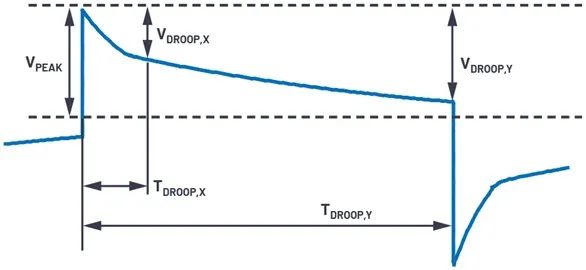

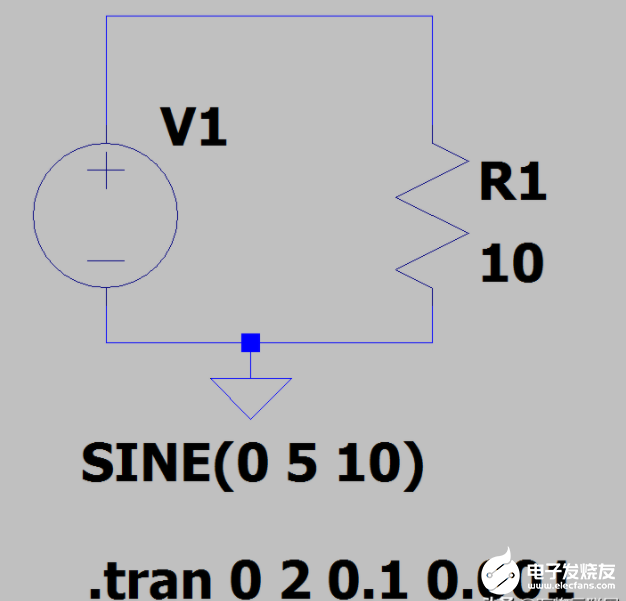

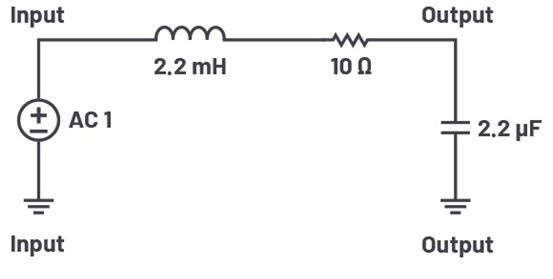

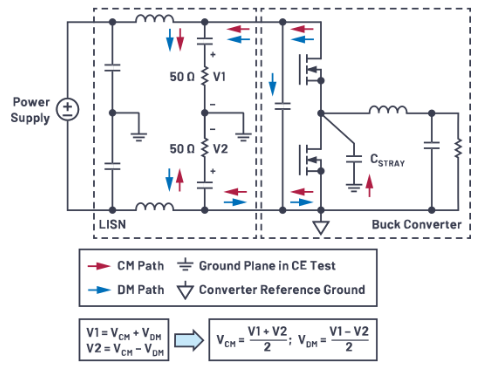

圖2所示為簡化的工程電源電路,可用于進行濾波或下降電壓和下降時間分析。受數據線供電網絡電感的影響,通信總線電壓會下降,如圖3所示。電壓下降分析很重要,因為當電壓下降超過峰值電壓的99%時,網絡中會出現位錯誤。可將系統設計為符合特定的電壓下降和時間下降規范。例如,1000BASE-T以太網假設500 ns內的電壓下降為27%,如圖3所示。

圖2. 工程電源,用于分析的簡化電路。

圖3. 電壓下降和下降時間。

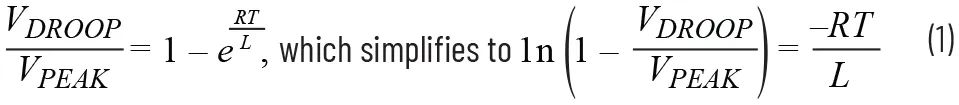

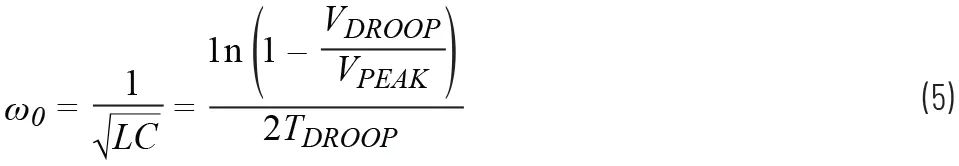

等式1至等式6提供電感值和電容值,以獲得目標電壓下降值和下降時間。假設在電壓下降期間,隔直電容間的電壓變化可忽略不計,則得出以下表達式,以求取串聯LR電路的電壓下降值:

基于目標下降、下降時間和電阻,該等式提供了求取電感的表達式:

通過以下等式求出串聯RLC電路的阻尼比:

假設臨界阻尼系統的ζ = 1,則給出了用于求取C的表達式:

代入上述求C和L的表達式,得出電路高通濾波器的截止頻率:

對于臨界阻尼系統:

為什么使用LTspice來進行工程電源模擬?

使用LTspice進行工程電源模擬有幾個令人信服的原因,包括:

真實電感模型,包括可使模擬與真實性能更緊密相關的器件寄生效應。LTspice庫中具有數以千計的電感模型,由眾多知名制造商(Würth、Murata、Coilcraft和Bourns)提供。

提供適用于ADI物理層通信收發器的LTspice模型以支持多種接口標準(CAN、RS-485),而其他半導體制造商通常不提供。

靈活的LTspice波形查看器可用于對數據線供電設計進行快速的數值評估。

與普通SPICE模擬器相比,借助LTspice的增強功能,模擬功耗器件(例如,LDO穩壓器和開關穩壓器)的速度非常快,用戶僅需幾分鐘即可查看大部分開關穩壓器的波形。

現成LTspice演示電路減少了原理圖采集時間。

有1000多種ADI功率器件模型、200多種運算放大器模型和ADC模型以及電阻、電容、晶體管和MOSFET模型,可供您用于完成剩余的設計部分。

使用LTspice進行下降分析

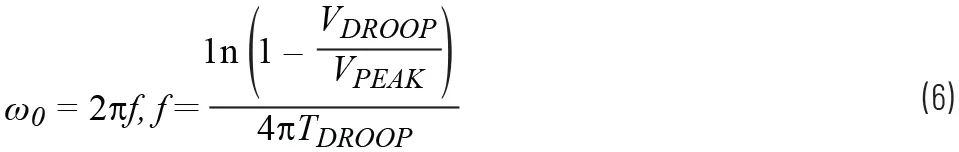

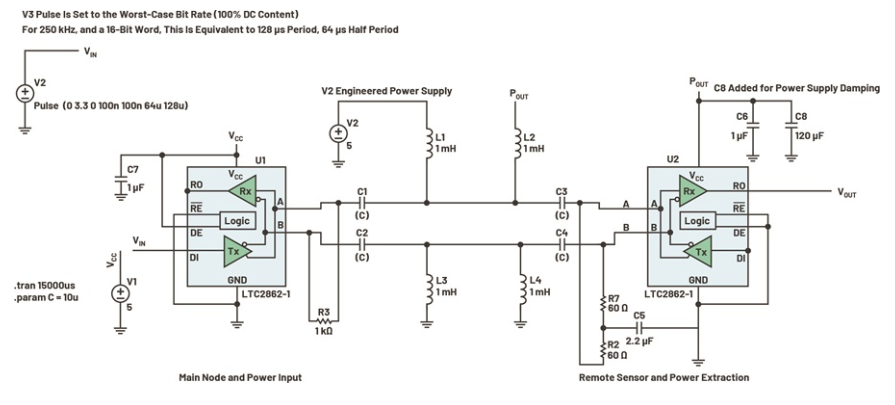

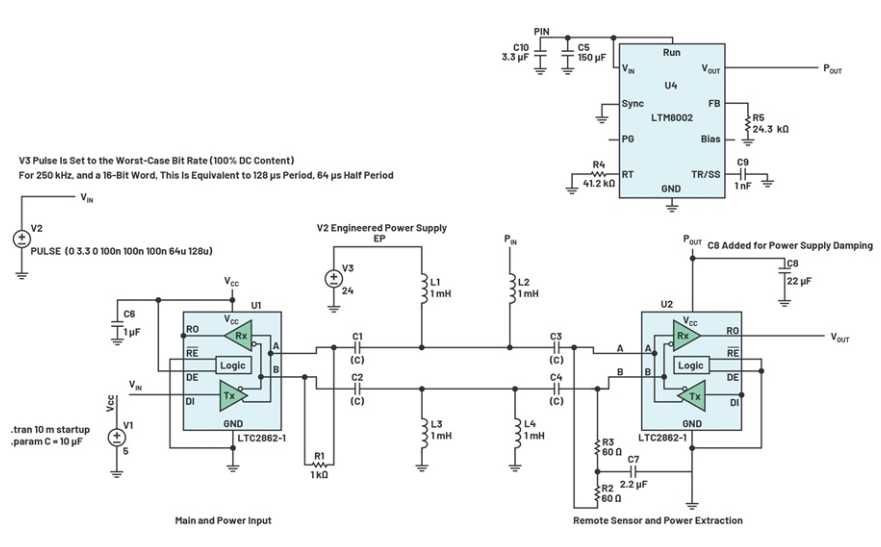

圖4提供了簡化的數據線供電模擬電路。該電路使用 LTC2862 RS-485收發器LTspice宏模型和1 mH電感(Würth 74477830)。LTspice中的真實電感模型包括可使模擬與真實設計性能更緊密相關的器件寄生效應。隔直電容值為10 μF。一般來說,使用較大的電感值和電容值可降低通信網絡上的數據速率性能。模擬測試用例的數據速率為250 kHz,這大致相當于通過RS-485接口移植時鐘同步SPI時100米的電纜通信2。模擬中使用的輸入電壓波形對應于最差情況的直流成分,其中包含16位字和所有邏輯高電平位。模擬結果如圖5和圖6所示。輸入電壓波形(VIN)與遠程受電器件的輸出相匹配(無通信錯誤)。圖6所示為用于進行下降分析的總線電壓差分波形(電壓A到電壓B)的放大圖。從L2電感中提取的遠程傳感器節點電壓提供5 V±1 mV的電源軌。

圖4. 使用LTC2862 (RS-485)和1 mH Würth電感74477830的工程電源LTspice模擬電路。

圖5. RS-485總線差分電壓V(A,B)以及下降點X和Y的模擬結果。

圖6. 點X和Y的下降分析。

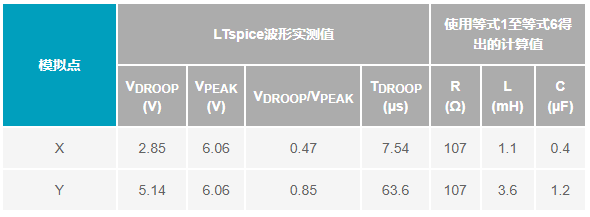

使用圖5和圖6的LTspice波形測量 VDROOP、 VPEAK和 TDROOP。然后,使用等式2和等式4計算L值和C值。如表1所示,計算出的L值為1 mH至3 mH,但該值可能因測量波形的位置而有所不同。在X點進行的測量最準確,產生了約為1 mH的正確電感值。高通濾波器頻率(等式6)就是下降時間和電壓的函數,對于點X,1位(半個時鐘周期)的頻率約等于250 kHz/32,與圖5所示的輸入波形(V3)相匹配。

運行圖4所示的模擬時,值得注意的是,建議使用C8電容來降低傳感器上的電壓過沖(功率提取節點上的VPOUT)。添加C8以后,過沖最大值為47 mV,并且在1.6 ms內建立至所需5 VDC的1 mV以內。在不使用C8電容的情況下進行模擬導致系統欠阻尼,過沖值為600 mV,并且與5 VDC目標存在100 mV的永久電壓振蕩。

C值為0.4 μF至1 μF,如表1所示。C值小于10 μF隔直電容值,因為電路包含額外的串聯電容(1 μF、100 μF),且可能出現過阻尼,這與等式1至等式6的計算相矛盾。

表1. 下降分析:使用VDROOP/VPEAK和TDROOP測定電路電感和電容

使用LTspice模擬更復雜的供電電路

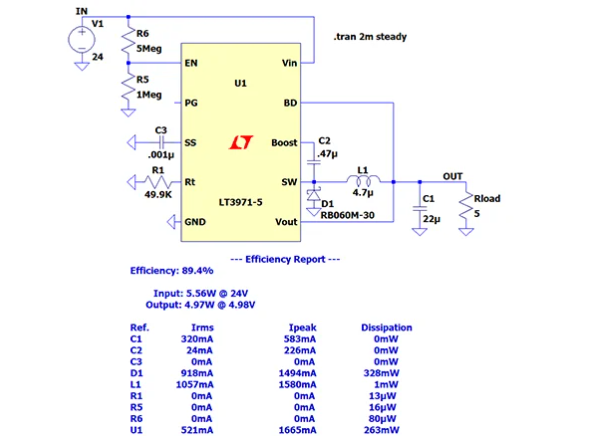

在傳感器節點添加LDO穩壓器或DC-DC轉換器可實現在標準工業電壓軌(例如,12 VDC和24 VDC)上從主節點供電。LDO穩壓器或DC-DC開關穩壓器的選擇取決于應用要求。如果應用使用12 VDC電壓軌,則LDO穩壓器可能適合用來實現超低噪聲性能,并且在傳感器子節點產生可接受的功耗。對于24 VDC電壓軌,建議使用效率更高的DC-DC開關穩壓器來降低功耗。ADI的低噪聲Silent Switcher架構確保可實現更高的能效和低噪聲。

24 VDC廣泛用于鐵路、工業自動化、航空航天和防務應用中。適用于鐵路用電子裝置的EN 50155標準5規定了24 VDC的標稱輸入電壓,但標稱輸入變化為0.7 VIN至1.25 VIN,規定的擴展范圍為0.6 ×VIN至1.4 × VIN。因此,應用中使用的DC-DC器件需要14.4 VDC至33.6 VDC的較寬輸入范圍。

LTM8002?Silent Switcher μModule穩壓器采用6.25 mm × 6.25 mm BGA封裝和3.4 VDC至40 VDC的較寬輸入范圍,非常適用于鐵路車輛監控中所用的空間受限振動傳感器。

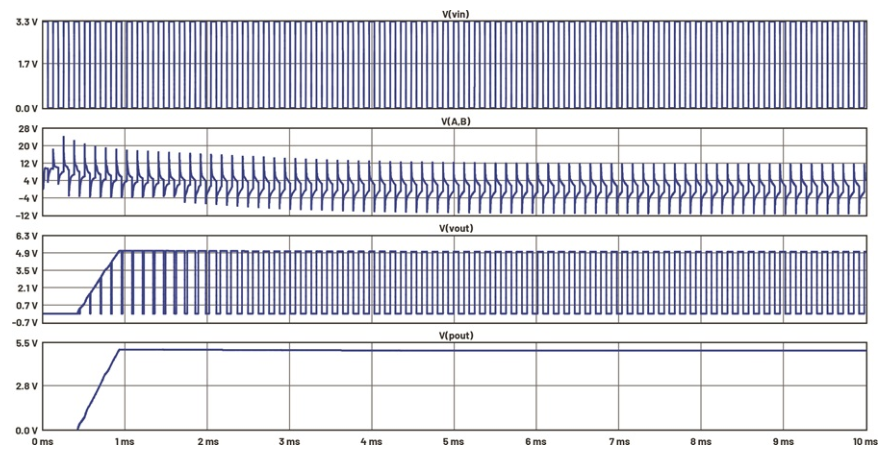

圖7復制了圖4的原理圖,增加了LTM8002,從主節點輸送至子節點傳感器的電源為24 VDC。模擬顯示在LTM8002上達到所需5 VDC±1%的輸出電壓需要1ms的斜坡時間。建議設計人員在上電時實施2 ms至3 ms時間延遲,然后再啟動主節點和子節點之間的通信。這將確保在傳感器節點輸出端獲得有效數據。

圖7. 在傳感器子節點(LTM8002)使用ADI的低噪聲Silent Switcher器件可為電源軌設計提供更大的靈活性。

圖8. 在VPOUT上達到所需5 VDC的斜坡時間為1 ms,2 ms至3 ms后在VOUT上獲得有效數據。

完整的MEMS信號鏈模擬

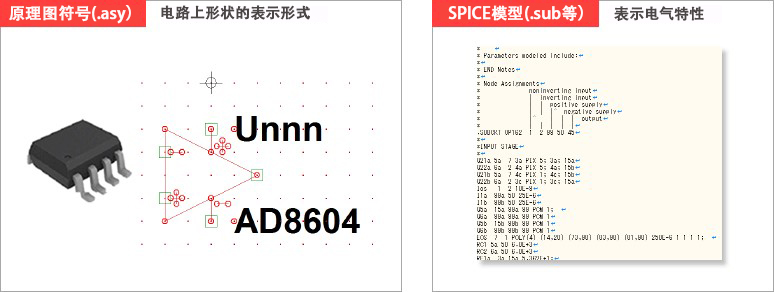

ADI公司提供很多設計筆記,可幫助設計人員完成MEMS信號鏈設計,并使用LTspice進行模擬(參見圖9)。雖然很多MEMS均為數字輸出,但也有很多高性能傳感器具有模擬輸出。模擬運算放大器和ADC信號鏈可在完成硬件設計構建之前提供有價值的見解。

圖9. 使用LTspice的完整傳感器信號鏈模擬(簡圖—未顯示所有連接和無源器件)。

如要分析低通濾波、放大器和ADC輸入對傳感器數據的影響,設計人員可參考 Gabino Alonso和Kris Lokere提供的LTspice基準電路。可提供AD4002 和 AD4003 18位SAR ADC以及16位 LTC2311-16的模擬模型。關于使用LTspice開發定制的模數轉換器模型,Erick Cook提供了有用的實踐指南。

有200多種運算放大器模型可供選擇,包括 ADA4807 和 ADA4805 系列。可提供基準電壓宏模型(例如,ADR4525 和LTC6655-5 ),以 及 ADA4807-1 基準電壓緩沖器。

Simon Bramble在他的一篇關于狀態監控系統的文章中介紹了如何使用LTspice來分析振動數據的頻譜。Simon的文章提供了關于格式化和分析捕獲的傳感器數據的有用提示。

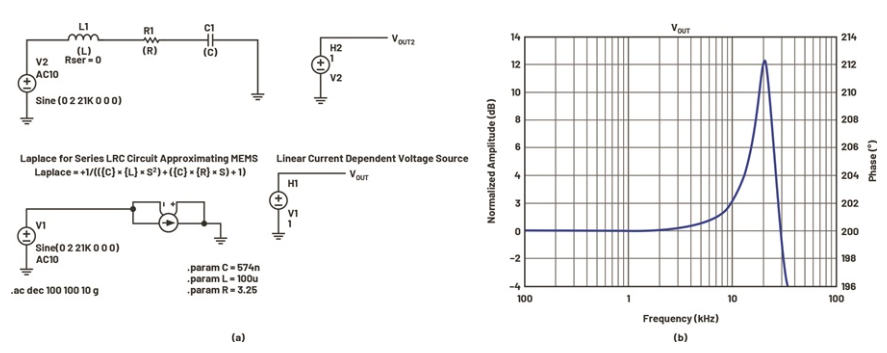

圖10所示為ADXL1002 低噪聲、±50 g MEMS加速度計頻率響應的LTspice模型示例。以LTspice拉普拉斯格式使用串聯LRC電路與MEMS頻率響應很接近。模擬模型與數據表典型性能保持較好的一致性,諧振頻率為21 kHz,在11 kHz時為3 dB。對于交流分析,最好在LTspice中使用Laplace電路,但對于瞬態分析,應使用分立式RLC器件以獲得優質模擬性能。

圖10. (a) MEMS頻率響應的Laplace模型,(b)圖顯示諧振頻率為21 kHz,在11 kHz時為3 dB。

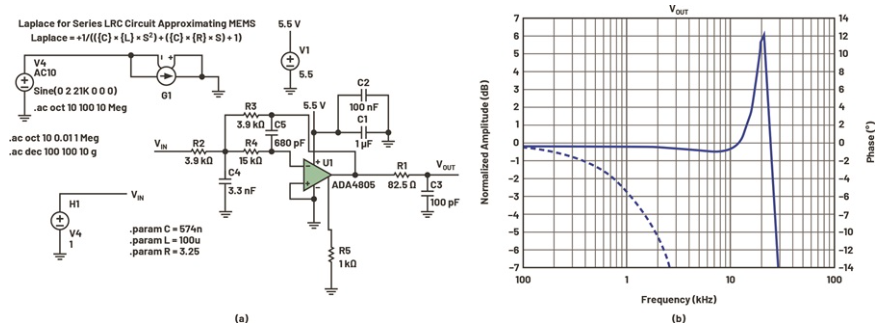

對于模擬輸出加速度計(例如,ADXL1002),帶寬的定義為對直流(或低頻)加速度的響應降至–3 dB時的信號頻率。圖11復制了圖10的MEMS頻率響應模型,但還包括運算放大器的濾波器電路。使用該濾波器電路,可在3 dB內測量更多的MEMS頻率響應。該圖顯示,在17 kHz時運算放大器的VOUT為3 dB,而未濾波MEMS的輸出在11 kHz時為3 dB。

圖11. (a) MEMS頻率響應和濾波器模型,以及(b)推高至17 kHz的3 dB點(與11 kHz下的圖10b相比)。

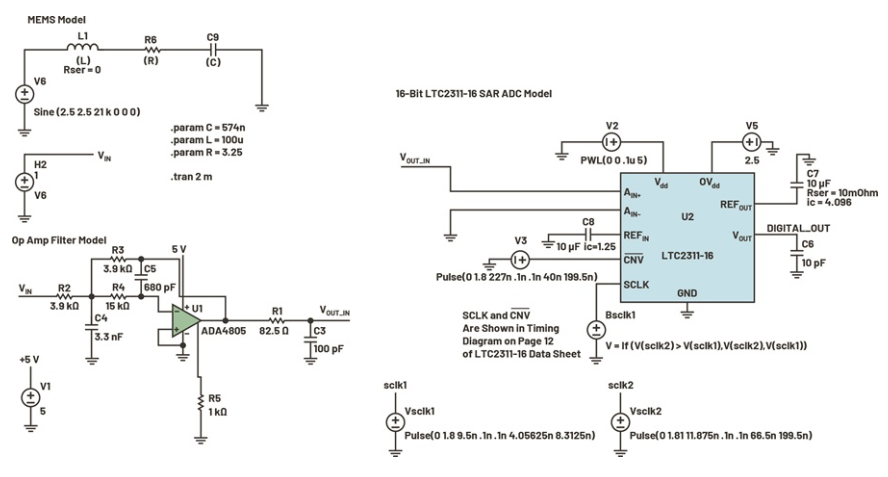

圖12包括MEMS輸入模型(圖10中的分立式RLC)、運算放大器濾波和16位LTC2311-16 SAR ADC模型。可使用模塊化方法構建和模擬完整的信號鏈,將有線接口和工程電源作為獨立的模塊添加。

圖12. MEMS輸入模型(圖10中的分立式RLC)、運算放大器濾波和16位LTC2311-16 SAR ADC模型。

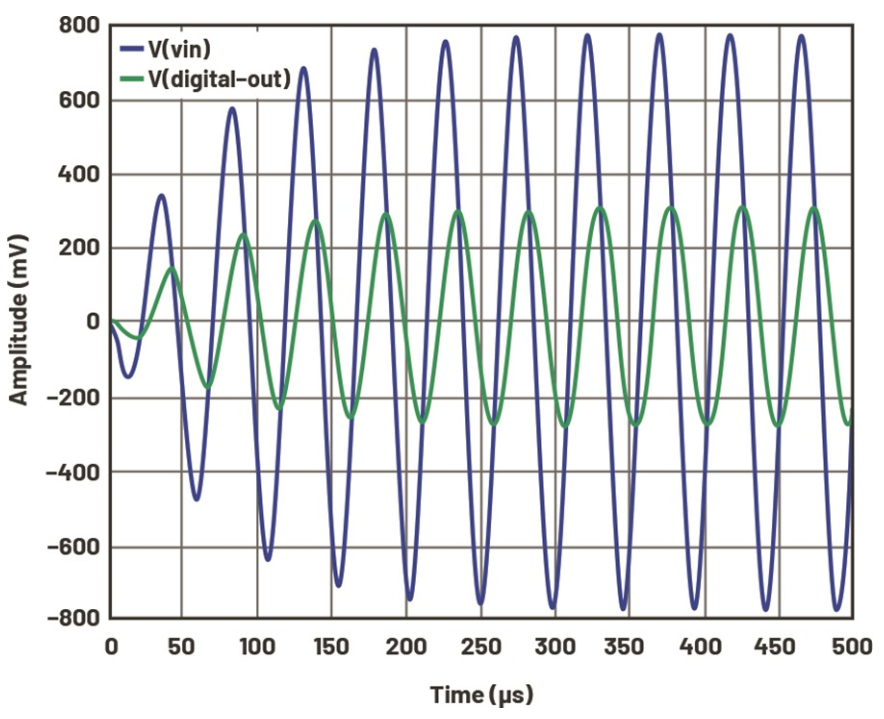

對于瞬態模擬,可探測LTC2311-16 DIGITAL_OUT節點,以查看對應于MEMS電壓輸入(VIN)的數字輸出。可修改LTC2311-16 LTspice模型,以減少串行時鐘和CNV接口時序,并且可將數字輸出基準OVDD更改為1.71 V至2.5 V范圍內的任何值。一些RS-485收發器(例如,LTC2865)包括一個邏輯接口引腳VL,該引腳可在1.8 V或2.5 V下運行,從而為ADC數字輸出數據的有線流傳輸提供完美匹配。然后可使用LTC2865 VCC引腳,在3.3 V或5.0 V下單獨為RS-485接口供電,以提供電壓更高的電纜驅動。

圖13. MEMS模型的輸入電壓(VIN)和濾波后的數字化輸出電壓(DIGITAL_OUT)。

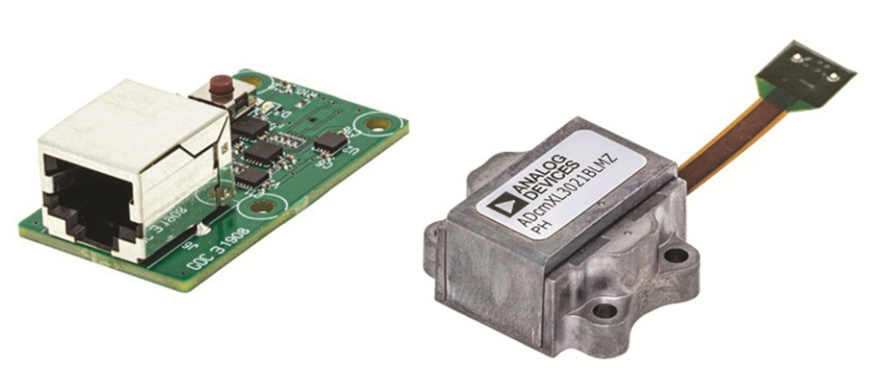

參考MEMS和工程電源評估平臺

ADI的有線狀態監控平臺為 ADcmXL3021 三軸振動傳感器提供工業有線鏈接解決方案。硬件信號鏈由ADcmXL3021加速度計組成,SPI和中斷輸出與接口PCB相連,通過數米長的電纜將發送至RS-485物理層的SPI轉化發送至遠程主控制器板。SPI到RS-485物理層的轉換可以使用隔離或非隔離的接口PCB實現,其中包括iCoupler隔離(ADuM5401/ADuM110N0)和RS-485/RS-422收發器(ADM4168E/ADM3066E)。該解決方案通過一根標準電纜(工程電源)將電能和數據結合在一起,從而降低了遠程MEMS傳感器節點的電纜和連接器成本。專用軟件GUI可以簡單配置ADcmXL3021器件,并在長電纜上捕捉振動數據。GUI軟件將數據可視化顯示為原始時間域或FFT波形。

圖14. 數據線供電的有線振動監控。

結論

現代MEMS傳感器解決方案的體積小、集成度高,并且放置在振動源附近,用于測量振動頻率。頻率隨時間的變化表明振動源(電機、發電機等)存在問題。頻率測量對于CbM而言至關重要。使用工程電源解決方案可節省MEMS傳感器的連接器數量和電纜成本。LTspice是強大的免費模擬工具,可用于模擬工程電源設計。數千個功率器件模型(包括LTM8002 Silent Switcher器件)可用于完成剩余的設計部分。使用提供的ADC、運算放大器和MEMS模型,可實現完整的MEMS信號鏈模擬。

審核編輯:黃飛

?

電子發燒友App

電子發燒友App

評論