為減小導(dǎo)通損耗及反向恢復(fù)損耗,同步整流需要精確的時(shí)間控制電路,雖然已有幾種方法來(lái)產(chǎn)生控制信號(hào),我們現(xiàn)在采用一種從反饋系統(tǒng)來(lái)有源控制的柵驅(qū)動(dòng)信號(hào)的定時(shí)系統(tǒng)。其關(guān)鍵優(yōu)點(diǎn)在于該電路將根據(jù)元件狀態(tài)的變化來(lái)特別調(diào)節(jié)同步整流MOSFET中的不可控的電容。時(shí)間的延遲及溫度變化對(duì)MOSFET閾值的影響都可以根據(jù)反饋環(huán)來(lái)校正。

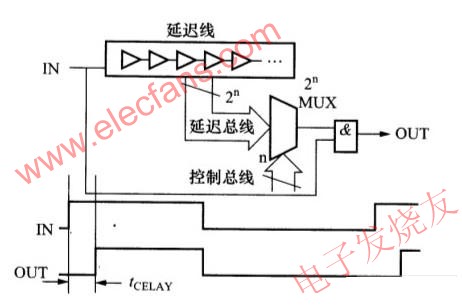

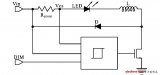

為控制柵軀動(dòng)的時(shí)間,在圖1中使用了可調(diào)延遲的電路,該延時(shí)電路包含三個(gè)主要元件,一個(gè)延遲線,一個(gè)乘法器及一個(gè)邏輯與門(mén)電路。到延遲線的輸入信號(hào)是相對(duì)每個(gè)延遲元件都延遲幾個(gè)納秒的信號(hào)。為了產(chǎn)生控制導(dǎo)通的延遲,乘法器選擇了使輸出信號(hào)延遲的元件,最后與門(mén)確定延遲加到驅(qū)動(dòng)導(dǎo)通的上升沿。從IN到OUT的延遲控制由數(shù)字控制總線來(lái)執(zhí)行,數(shù)字總線加到乘法器的地址輸入上。相反地,如果控制總線設(shè)置全部為0,則從IN到OUT的延遲就為0,即沒(méi)有延遲。幾種不同的延遲時(shí)間可以設(shè)定,給出幾種開(kāi)啟延遲時(shí)間,關(guān)閉延遲時(shí)間,或?qū)ΨQ的開(kāi)啟及關(guān)斷延遲。注意看圖1中是一個(gè)電壓檢測(cè)電路及數(shù)字控制器,為執(zhí)行不同的延時(shí)設(shè)置,會(huì)用不同的電壓檢測(cè)電路及數(shù)字控制器。

圖1 可調(diào)延遲電路

A、控制驅(qū)動(dòng)VR的執(zhí)行方案

控制驅(qū)動(dòng)電路的設(shè)計(jì)從回流的MOSFET VR開(kāi)始。隨著其源漏電壓降到零,它將立即被關(guān)斷。一種實(shí)現(xiàn)它的簡(jiǎn)單方法就是用比較器檢測(cè)VR的源漏電壓過(guò)零時(shí)間,用這種方法的問(wèn)題在于通過(guò)比較器,邏輯電路及柵驅(qū)動(dòng)的延遲會(huì)產(chǎn)生出來(lái),這要給予考慮。即使非常快的電路,延遲總量也會(huì)有50ns或更多。此期間體二極管會(huì)導(dǎo)通,并增加大的導(dǎo)通損耗,從檢測(cè)降落的源漏電壓到MOSFET導(dǎo)通時(shí),一個(gè)邏輯回應(yīng)的固有時(shí)間延遲可以用從最后一個(gè)開(kāi)關(guān)周期得到的信息處理,去預(yù)置下一次的MOSFET的導(dǎo)通。在此預(yù)期方法中,MOSFET的柵壓開(kāi)始在其源漏電壓降落之前就增加。此期間讓柵壓提前動(dòng)作,在源漏電壓降下時(shí)其即導(dǎo)通,而體二極管決不會(huì)導(dǎo)通。

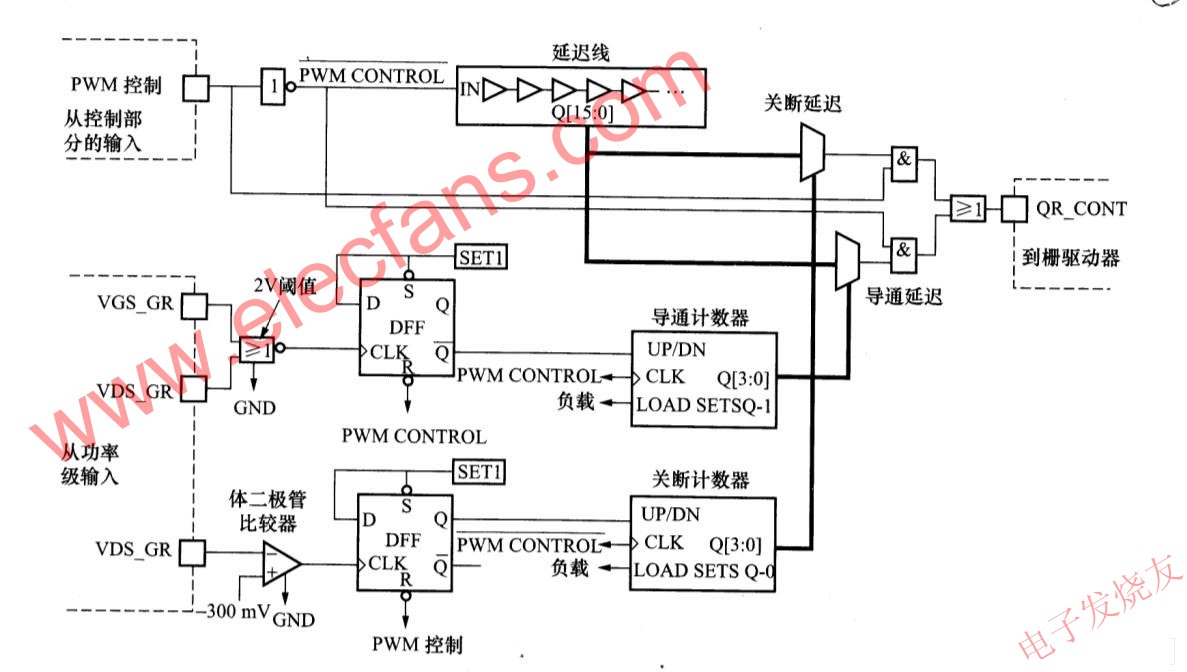

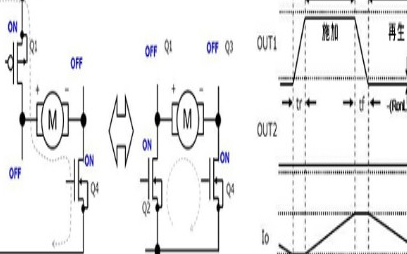

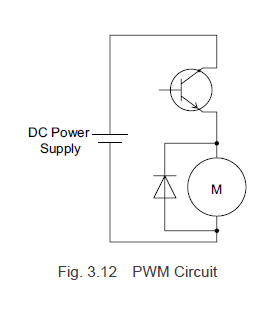

圖2展示出控制電路可實(shí)現(xiàn)VR的導(dǎo)通及關(guān)斷。它使用了兩個(gè)乘法器,兩個(gè)記數(shù)器,一個(gè)延遲線及控制MOSFET導(dǎo)通及延遲的膠合邏輯,因此消除了體二極管的導(dǎo)通。電路的描述從MOSFET的開(kāi)啟延遲開(kāi)始。PWM控制信號(hào)驅(qū)動(dòng)初級(jí)側(cè)MOSFET Q1,同時(shí)加到延遲線。當(dāng)電源第一次啟動(dòng),則LOAD輸入到記數(shù)器為高電平,它設(shè)置了開(kāi)啟延遲的計(jì)數(shù)器為全部是1(高電平),而設(shè)置了關(guān)斷延遲計(jì)數(shù)器全部為零(低電平),隨著計(jì)數(shù)器開(kāi)始記數(shù),從控制電路的輸出到柵驅(qū)動(dòng)的結(jié)果之間為最大的導(dǎo)通延遲及最小的關(guān)斷延遲。

圖2 VR的控制電路

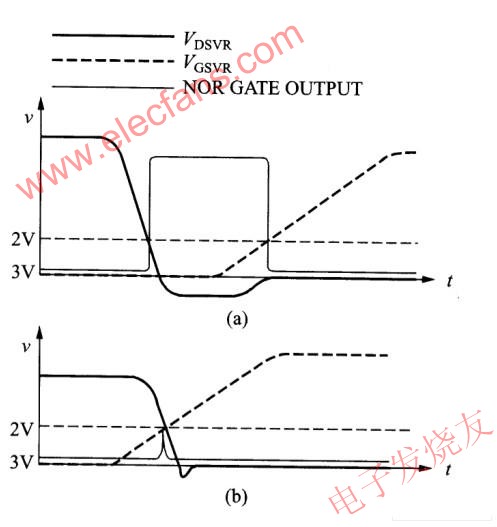

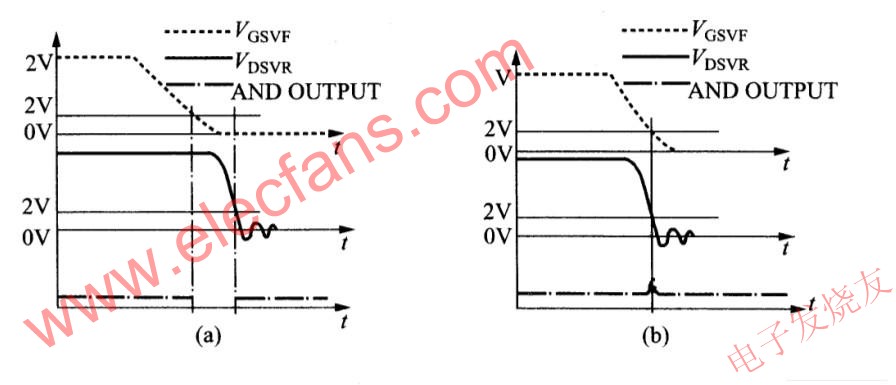

隨著延遲設(shè)置了這些數(shù)值,VR體二極管將會(huì)導(dǎo)通,反饋環(huán)路也將開(kāi)始調(diào)節(jié)延遲,使之實(shí)現(xiàn)最小的體二極管導(dǎo)通,圖3(a)和(b)展示出VR在導(dǎo)通期間的柵源和漏源電壓,圖3(a)展示在VR導(dǎo)通時(shí)延遲太長(zhǎng)的電路,而圖3(b)展示出最佳延遲時(shí)間。

圖3 VR的開(kāi)啟波形

調(diào)節(jié)關(guān)斷延遲,用一個(gè)或門(mén)在一個(gè)大約2V輸入閾值,來(lái)檢測(cè)VR的柵源電壓和漏源電壓兩者是否都為低電平時(shí)的狀態(tài),從或門(mén)出來(lái)的高電平指示控制器,告之延遲時(shí)間太長(zhǎng),控制器就會(huì)在下一個(gè)開(kāi)關(guān)周期減少延遲。

或門(mén)輸出被鎖存、倒相并送至開(kāi)啟延遲計(jì)數(shù)器的UP/DOWN輸入端,該信號(hào)告訴計(jì)數(shù)器向上記數(shù)或向下記數(shù)。如果或門(mén)輸出為高電平,則記數(shù)器向下記數(shù),減少延遲時(shí)間。而或門(mén)為低電平輸出時(shí),計(jì)數(shù)器向上記數(shù),則增加延遲時(shí)間。計(jì)數(shù)器并有效地保持該延遲信息給下一個(gè)工作周期。反饋環(huán)會(huì)調(diào)節(jié)開(kāi)啟延遲使之縮短,直到或門(mén)沒(méi)有更長(zhǎng)的輸出脈沖,當(dāng)計(jì)數(shù)器工作在恒定負(fù)載和線路電壓時(shí),對(duì)下一個(gè)周期的開(kāi)啟延遲將稍微有些加長(zhǎng),或門(mén)將給出高輸出脈沖,延遲將會(huì)縮短,在這種方式中,電路會(huì)在兩個(gè)延遲時(shí)間之間抖動(dòng),一個(gè)長(zhǎng)一些,另一個(gè)就會(huì)接近最佳狀態(tài)。

關(guān)斷控制器工作在與開(kāi)啟控制器非常相似的管理方式。不同之處在于電壓檢測(cè)電路及計(jì)數(shù)器的記數(shù)方向。當(dāng)體二極管導(dǎo)通時(shí),用一高速比較器檢測(cè)。為了更加精確,一個(gè)比較器用于檢測(cè)體二極管導(dǎo)通,去替代或門(mén),在開(kāi)啟的期間,電流正從整流MOSFET向回流MOSFET換向,電流的DI/DT非常高,VR的源漏電壓上通常可看到其震鈴。如果用一個(gè)比較器檢測(cè)體二極管在VR導(dǎo)通期間的體二極管狀態(tài),由于源漏電壓的振鈴,可能會(huì)出現(xiàn)誤觸發(fā)。在VR關(guān)斷期間,通過(guò)VR MOSFET器件的電流是恒定的。該電流或者通過(guò)其通道或者通過(guò)其體二極管。在關(guān)斷時(shí),僅有非常小的振鈴,比較器用來(lái)改善精度,比較器的閾值必須比先前的MOSFET通道導(dǎo)通時(shí)的誤觸發(fā)值更負(fù)向一點(diǎn)。

在通道導(dǎo)通期間,源漏電壓大約等于I LOAD*.RDS(ON),并規(guī)定了噪聲。比較器閾值設(shè)置在大約-300mV。比較器比較VR的源漏電壓與此設(shè)置閾值,從比較器出來(lái)的高電平指示給控制器,系體二極管在導(dǎo)通,延遲時(shí)間需要增加,這與開(kāi)啟局面精確對(duì)應(yīng)。因?yàn)殛P(guān)斷延遲記數(shù)設(shè)置在起始時(shí)全部為0。圖4(a)和(b)示出VR關(guān)斷波形及比較器的輸出。

圖4 VR的關(guān)斷波形

(a)非最佳延遲( b)最佳延遲

圖4(a)示出當(dāng)延遲設(shè)置太短時(shí)電路的工作狀態(tài)。圖4(b)示出最佳延遲狀態(tài)。由于在VR導(dǎo)通中,關(guān)斷延遲在某一值處處于抖動(dòng)狀態(tài),這就是太長(zhǎng)以及最佳值的兩個(gè)狀態(tài)。

問(wèn)題出現(xiàn):開(kāi)啟延遲及關(guān)斷延遲可否設(shè)置的短些,這是否會(huì)造成交叉導(dǎo)通,問(wèn)題在于仔細(xì)地研究比較器的特性,及延遲線的每個(gè)元件的延遲,比較器僅能響應(yīng)差分輸入電壓,此電壓僅在轉(zhuǎn)換間隔結(jié)點(diǎn)上有足夠的時(shí)間總量才會(huì)存在。假定比較器可以檢測(cè)出體二極管導(dǎo)通用5ns時(shí)間。在下一個(gè)周期內(nèi),延遲即可調(diào)節(jié),用延遲線上一位數(shù)碼去減少體二極管的導(dǎo)通。當(dāng)然,比較器也不會(huì)去響應(yīng)下一個(gè)周期體二極管的導(dǎo)通,因?yàn)樗谘舆t線的每個(gè)元件上大約減少5ns的延遲時(shí)間。關(guān)鍵防止交叉導(dǎo)通的措施是設(shè)置的每個(gè)元件的延遲要比比較器可檢測(cè)的最小脈寬要少。

B、 控制驅(qū)動(dòng)QF的執(zhí)行

正向整流的QF的控制和回流元件VR很不一樣。一個(gè)主要的區(qū)別是:其目標(biāo)是在變壓器復(fù)位后即將QF開(kāi)啟,它獨(dú)立于PWM控制信號(hào)的上升沿和下降沿,它不同于回流的MOSFET。此處,目標(biāo)只不過(guò)是調(diào)節(jié)PWM控制器信號(hào)的上升沿及下降沿的時(shí)間,以減少VR體二極管的導(dǎo)通時(shí)間,并使之最小化。

了解該目標(biāo)是在變壓器復(fù)位后要將QF導(dǎo)通,一個(gè)好的起始點(diǎn)就是圖5所示出的使QF導(dǎo)通所需的電路。

圖5 VR的控制電路

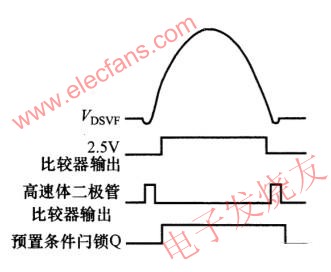

首先,一個(gè)高速體二極管比較器用于檢測(cè)QF開(kāi)始導(dǎo)通時(shí)的體二極管,它在變壓器復(fù)位時(shí)間間隔結(jié)束時(shí)發(fā)信號(hào),偏巧如圖6所示,這個(gè)比較器還將檢測(cè)出的初級(jí)側(cè)MOSFET Q1關(guān)斷后令其體二極管正好導(dǎo)通。

使用該比較器僅單獨(dú)為開(kāi)啟QF,并確保在Q1進(jìn)入關(guān)斷的時(shí)間。這樣變壓器將絕不容許復(fù)位。為防止這一點(diǎn),用一個(gè)低速比較器檢測(cè)QF的源漏電壓升至2.5V。當(dāng)QF源漏電壓升過(guò)2.5V時(shí),設(shè)置了一個(gè)預(yù)置鎖存調(diào)節(jié),它將使高速體二極管比較器能輸出工作。在QF源漏電壓降過(guò)-300mV的體二極管比較器閾值,QF就立刻導(dǎo)通,并設(shè)置QF的控制鎖存。在高速比較器輸出變成高電平。預(yù)置鎖存即刻復(fù)位,開(kāi)啟電路在下次導(dǎo)通事件中就處在恰當(dāng)狀態(tài)。從體二極管比較器檢測(cè)出體二極管的導(dǎo)通固有延遲期間,到QF導(dǎo)通的通道,體二極管傳導(dǎo)變壓器的磁化電流。雖然在此間隔內(nèi),在QF體二極管有導(dǎo)通損耗,但與之相比,這已是QF遇到的最小的損耗。如果QF在此糟糕的時(shí)間間隔還保持關(guān)斷的話。為完全消除這個(gè)損耗,用一個(gè)相同的預(yù)先控制的方案,用來(lái)開(kāi)啟VR,雖然這在理論上是可以的,但實(shí)際上會(huì)相當(dāng)困難,因?yàn)榇颂帥](méi)有PWM控制信號(hào)的脈沖沿存在,此時(shí)系變壓器完全復(fù)位的狀態(tài)。

圖6 VR預(yù)鎖存波形

一個(gè)輸出起始設(shè)置在零的計(jì)數(shù)器控制著關(guān)斷電路。采用將計(jì)數(shù)器輸出全部設(shè)置為0,也即在PWM控制信號(hào)的下降沿及QF的柵源電壓之間實(shí)際上為零延時(shí),結(jié)果QF的柵源電壓,VR的漏源電壓以及與門(mén)輸出的三個(gè)波形示于圖7(a)。

圖7 VF的關(guān)斷波形

(a)非最佳延遲(b)最佳延遲

VF關(guān)斷電路中的與門(mén)更多的作用如VR開(kāi)啟控制電路中的或門(mén),給一個(gè)命令到計(jì)數(shù)器,以直接令計(jì)數(shù)器向上或向下記數(shù)。在VF的關(guān)斷電路的情況,一個(gè)高電平從與門(mén)直達(dá)計(jì)數(shù)器以便在下個(gè)周期中向上記數(shù)。當(dāng)計(jì)數(shù)器為下個(gè)周期增加一個(gè)記數(shù)值,則PWM控制器的下降沿與VF的柵源電壓之間的延遲就會(huì)增加,從與門(mén)的輸出脈沖就會(huì)變窄,這個(gè)反饋影響將持續(xù)到VF的柵源電壓和VR的漏源電壓能夠同步。當(dāng)延遲最佳化時(shí),波形示于圖7(b)。

如在VR控制執(zhí)行電路中所描述,電路將會(huì)在兩個(gè)延遲值之間抖動(dòng),一個(gè)是最佳值,而另一個(gè)比最佳值略長(zhǎng)一些。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論