摘要:首先從理論上分析了影響ADC信噪比的因素,然后以此為依據(jù),從電路設(shè)計和器件選擇兩方出發(fā),采用模/數(shù)轉(zhuǎn)換器AD6644AST-65進(jìn)行高速高分辨率ADC電路設(shè)計,并給出電路實測結(jié)果。

在雷達(dá)、導(dǎo)航等軍事領(lǐng)域中,由于信號帶寬寬(有時可能高于10MHz),要求ADC的采樣率高于30MSPS,分辨率大于10位。目前高速高分辨率ADC器件在采樣率高于10MSPS時,量化位數(shù)可達(dá)14位,但實際分辨率受器件自身誤差和電路噪聲的影響很大。在數(shù)字通信、數(shù)字儀表、軟件無線電等領(lǐng)域中應(yīng)用的高速ADC電路,在輸入信號低于1MHz時,實際分辨率可達(dá)10位,但隨輸入信號頻率的增加下降很快,不能滿足軍事領(lǐng)域的使用要求。

針對這一問題,本文主要研究在不采用過采樣、數(shù)字濾波和增益自動控制等技術(shù)條件下,如何提高高速高分辨率ADC電路的實際分辨率,使其最大限度地接近ADC器件自身的實際分辨率,即最大限度地提高ADC電路的信噪比。為此,本文首先從理論上分析了影響ADC信噪比的因素;然后從電路設(shè)計和器件選擇兩方面出發(fā),設(shè)計了高速高分辨率ADC電路。經(jīng)實測表明,當(dāng)輸入信號頻率為0.96MHz時,該電路的實際分辨率為11.36位;當(dāng)輸入信號頻率為14.71MHz日寸,該電路的實際分辨率為10.88位。

1 影響ADC信噪比因素的理論分析

ADC的實際分辨率是用有效位數(shù)ENOB標(biāo)稱的。不考慮過采樣,當(dāng)滿量程單頻理想正弦波輸入時,實際分辨率可用下式表示:

ENOB=[SINA0(dB)-1.76]/6.02 (1)

式中,SINAD表示ADC的信噪失真比,指ADC滿量程單頻理想正弦波輸入信號的有效值與ADC輸出信號的奈奎斯特帶寬內(nèi)的全部其它頻率分量(包括諧波分量,但不包括直流允量)的總有效值之比。

ADC的信噪比SNR,指ADC滿量程單頻理想正弦波輸入信號的有效值與ADC輸出信號的奈奎斯特帶寬內(nèi)的全部其它頻率分量(不包括直流分量和諧波分量)總有效值之比。

由此可知,當(dāng)ADC的總諧波失真THD一定時,有效位數(shù)ENOB取決于SNR;ADC的SNR越高,其有效位數(shù)ENOB就越高。下面就來分析影響ADC信噪比SNR的因素。

理想ADC的噪聲由其固有的量化誤差(也稱為量化噪聲,如圖1所示)產(chǎn)生。但實際使用的ADC是非理想器件,它的實際轉(zhuǎn)換曲線與理想轉(zhuǎn)換曲線之間存在偏差,表現(xiàn)為多種誤差,如零點(diǎn)誤差、滿度誤差、增益誤差、積分非線性誤差I(lǐng)NL、微分非線性誤差DNL等。其中,零點(diǎn)誤差、滿度誤差、增益誤差是恒定誤差,只影響ADC的絕對精度,不影響ADC的SNR。INL指的是在校準(zhǔn)上述恒定誤差的基礎(chǔ)上,ADC實際轉(zhuǎn)換曲線與理想轉(zhuǎn)換曲線的最大偏差。而DNL指的是ADC實際量化間隔與理想量化間隔的最大偏差,改變ADC的量化誤差,能更直接地計算出ADC實際轉(zhuǎn)換曲線與理想轉(zhuǎn)換曲線的偏差對ADC的SNR的影響。

非理想ADC,除了上述誤差外,還有各種噪聲,如熱噪聲、孔徑抖動。前者是由半導(dǎo)體器件內(nèi)部分子熱運(yùn)動產(chǎn)生的,后者是由ADC孔徑延時的不確定性造成的。而ADC的外圍電路同樣會帶來噪聲,如ADC輸入級電路的熱噪聲、電源/地線上的雜波、空間電磁波干擾、外接時鐘的不穩(wěn)定性(導(dǎo)致ADC各采樣時鐘沿出現(xiàn)時刻不確定,帶來孔徑抖動)等,可以把它們都等效為ADC的上述兩種內(nèi)部噪聲。

上述誤差和噪聲的存在,導(dǎo)致ADC的SNR下降。下面先給出理想ADC的SNR計算公式,然后具體分析微分非線性誤差DNL、孔徑抖動△tj和熱噪聲對ADC的SNR的影響。

1.1 理想ADC的SNR

理想ADC的量化誤差g(υ)與滿量程內(nèi)輸入信號的電壓V的關(guān)系如圖1所示。量化誤差為在[-q/2,q/2]內(nèi)均勻分布且峰-峰值等于q(q=1LSB,LSB表示理想ADC的最小量化間隔)的鋸齒波信號。

設(shè)N位ADC滿量程電壓為±1V,輸入信號為s(t)=sinωt,則輸入信號電壓有效值Vs=1/√2=2N/2√2×q,量化噪聲電壓有效值于是得ADC輸出信噪比為:

SNR=6.02N+1.76(dB) (2)

1.2 微分非線性誤差DNL

非理想ADC的量化間隔是非等寬的,這將導(dǎo)致ADC器件不能完全正確地把模擬信號轉(zhuǎn)化成相應(yīng)的二進(jìn)制碼,從而造成SNR的下降;且ADC每個量化的二進(jìn)制碼所對應(yīng)的量化間隔都不同,為便于分析,用ε(LSB)= εq表示實際量化間隔與理想量化間隔誤差的有效值,并近似認(rèn)為由于DNL的影響,在無失碼條件(DNL<1LSB)下,量化誤差均勻分布在[-上q+εq/2,q+εq/2]和[-q-εq/2,q-εq/2]內(nèi)。如圖1 中實線所示(虛線偽理想ADC量化誤差)。這樣,在考慮了DNL之后的ADC量化噪聲電壓Vq_DNL為:

1.3 孔徑抖動△tj

孔徑時間又稱孔徑延遲時間,是指對ADC發(fā)出采樣命令(采樣時鐘邊沿)時刻與實際開始采樣時刻之間的時間間隔。相鄰兩次采樣的孔徑時間的偏差稱為孔徑抖動,記作△tj。孔徑抖動造成了信號的非均勻采樣,引起了誤差,設(shè)ADC滿量程電壓為±1V輸入信號為s(t)=sinωt,孔徑抖動有效值為σ△tj,則由孔徑抖動帶來的誤差電壓為:

![]()

1.4熱噪聲

這里將ADC電路中微分非線性誤差DNL、孔徑抖動△tj外的其它噪聲都等效為ADC輸入端的熱噪聲電壓Vtn,設(shè)其有效值為σtn。

1.5非理想ADC的SNR

一般情況下,量化噪聲、微分非線性誤差DNL、孔徑抖動△tj和熱噪聲彼此相互獨(dú)立,綜合芍慮這四個因素的影響,可得到ADC的SNR計算公式如下:

式中,N--ADC的量化位數(shù)

ε--ADC的實際量化間隔與理想量化間隔誤差的有效值,單位LSB

fin--ADC輸入信號頻率,單位Hz

σ△tj--ADC的孑L徑抖動有效值,單位s

σtn--等效到ADC輸入端的熱噪聲的有效值單位LSB

對于高分辨率ADC器件,其固有量化誤差、微分非線性誤差DNL和器件熱噪聲均較小。當(dāng)fin較高時,ADC電路的SNR主要取決于孔徑抖動,此時有

2 基于AD6644AST一65的高速高分辨率ADC電路設(shè)計實例

電路設(shè)計目標(biāo):有效位數(shù)ENOB≥10.50bit、采樣率為40MSPS、輸入信號頻率小于15MHz,輸入信號幅度為-ldBFs。該指標(biāo)能滿足數(shù)字儀表、高速數(shù)據(jù)采集卡、軟件無線電和雷達(dá)、導(dǎo)航等領(lǐng)域中數(shù)字波束形成的要求。

2.1電路設(shè)計與器件選擇

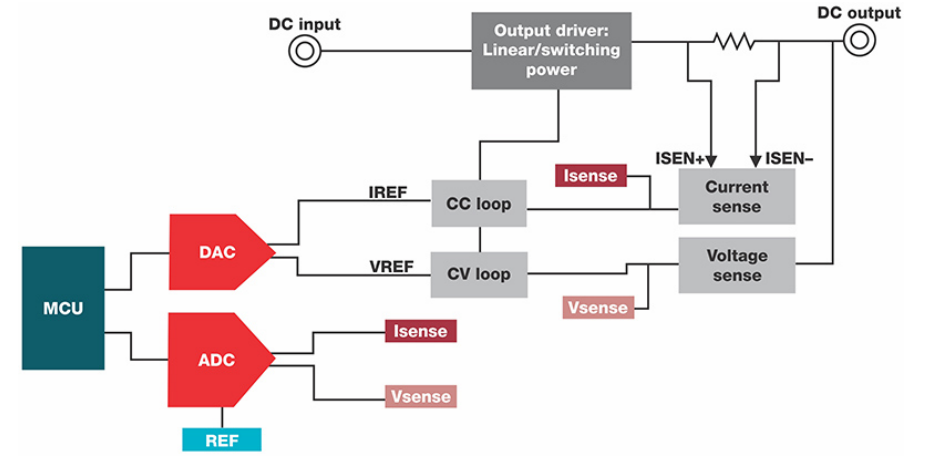

本電路主要由模/數(shù)轉(zhuǎn)換器ADC、輸入電路、輸出屯路、時鐘電路和電源電路組成,如圖2所示。

2.1.1時鐘電路

時鐘電路的設(shè)計主要包括AD6644AST-65采樣時鐘相位噪聲指標(biāo)的確定以及PECL差分時鐘的實現(xiàn)。

2.1.2 ADC輸入電路

ADC輸入電路多采用運(yùn)放直流耦合或變壓器交流耦合方式,為輸入信號提供增益、偏置和緩沖。

由于運(yùn)放為有源器件,除具有一定的諧波失真外,還存在主要集中在低頻段的1/f噪聲和較寬頻帶內(nèi)的白噪聲。這些噪聲和諧波失真都降低了運(yùn)放的信噪比SNR和有效位數(shù)ENOB。當(dāng)運(yùn)放的SNR不明顯優(yōu)于甚至低于ADC的SNR時,它帶來的噪聲是不容忽視的,對于高分辨率ADC電路,甚至是不能接受的。而作為無源器件的變壓器,一般認(rèn)為它的噪聲和諧波失真是微乎其微、可以忽略的。因此,本電路的輸入電路采用變壓器交流耦合方式,選用Mini-Circuits公司的變壓器T4-6T。

為進(jìn)行比較,同時也提供運(yùn)放直流耦合方式,采用ADI公司的低噪運(yùn)放AD8138。根據(jù)AD8138的關(guān)參數(shù),計算得到的AD8138輸出的總諧波失真和熱噪聲之和大于1LSB。該指標(biāo)可能導(dǎo)致無法滿足電路熱噪聲不大于1.50LSB的設(shè)計要求,并帶來更大的諧波失真。因此可預(yù)知,采用AD8138時,ADC電路的有效位數(shù)ENOB會比采用變壓器時的有效位數(shù)ENOB有所下降,甚至達(dá)不到設(shè)計要求。

2.1.3 ADC輸出電路

ADC的模擬輸入和數(shù)據(jù)輸出之間存在少量的寄生電容,ADC數(shù)據(jù)輸出線上的噪聲會通過這些寄生電容耦合到模擬輸入端,導(dǎo)致ADC的SNR和有效位數(shù)ENOB下降。為解決這一問題,可在ADC數(shù)據(jù)輸出端接一鎖存器。

為減小ADC電源的波動,應(yīng)盡量降低ADC輸出端的負(fù)載電容和輸出電流。在ADC數(shù)據(jù)輸出端接一鎖存器可避免將其直接連在數(shù)據(jù)總線上,有效限制了其輸出端的負(fù)載電容;在ADC每一個數(shù)據(jù)輸出端都串聯(lián)一個電阻,可限制其輸出電流。

本電路采用74LC574作為AD6644AST-65的輸出數(shù)據(jù)鎖存器,同時每一個數(shù)據(jù)輸出端都串聯(lián)一個100Ω的電阻。

2.1.4 電源、地和去耦電路

AD6644AST-65的電源抑制比PSRR≈±lmV/V,當(dāng)外接電源的紋波為峰-峰值100mV時,等效于在AD6644AST-65輸入端產(chǎn)生100μV(0.77LSB)大小的噪聲,這相對于設(shè)計指標(biāo)而言是不能接受的。為減小外接電源對電路的影響,本電路采用Linear公司的低壓差LDO線性穩(wěn)壓器LTl086-5和LTlll7-3.3(兩個芯片的PSRR均大于60dB) 對外接穩(wěn)壓電源進(jìn)行穩(wěn)壓,為AD6644AST-65等模擬電路提供5V電源和3.3V電源。

時鐘、ADC的輸出信號以及后級數(shù)字電路的數(shù)字信號的跳變都會引起電源電流的急劇變化,由于印刷電路板的電源線和地線上存在分布電阻、電容和電感,當(dāng)有變化的電流經(jīng)過時,其上的壓降也隨之變化;頻率較高時,就表現(xiàn)為電地間的高頻雜波。為降低這類雜波干擾,本電路采取以下措施:

· 時鐘電路的5V電源,由VCC_5VA串聯(lián)一磁珠FB得到;

· AD6644AST-65后級數(shù)字電路的3.3V電源,由VCC_3.3VA串聯(lián)一磁珠FB得到;

· 模擬地和數(shù)字地分開布線,并在一點(diǎn)用磁珠FB相連;

· ADC的所有電源管腳都就近對地接去耦電容。

圖3

磁珠對MHz級以上的信號有較好的吸收作用,能有效降低時鐘電源、數(shù)字電源對AD6644AST-65模擬電源的影響,以及數(shù)字地對模擬地的影響。

去耦對于高速高分辨率ADC電路尤為重要。為此,本電路采用0.01μF的NPO材料(屬低損耗、超穩(wěn)定的電容材料,電氣特性基本上不隨溫度、電壓、時間的變化而變化,自諧振頻率較高,適用于高頻場合)自0 1206封裝的貼片電容和0.1μF的X7R材料(屬穩(wěn)定性電容材料,電氣特性隨溫度、電壓、時間變化不明顯,適用于中、低頻場合)的0805封裝的貼片電容并聯(lián),有效地濾除電地間較寬頻帶的雜波。

2.1.5電路板的布局布線

ADC界于模擬電路和數(shù)字電路之間,且通常被劃歸為模擬電路。為減小數(shù)字電路的干擾,應(yīng)將模擬電路和數(shù)字電路分開布局;為減小信號線上的分布電阻、電容和電感,應(yīng)盡量縮短導(dǎo)線長度和增大導(dǎo)線之間的距離;為減小電源線和地線的阻抗,應(yīng)盡量增大電源線和地線的寬度,或采用電源平面、地平面。本電路在設(shè)計印刷電路板時,都遵循了以上原則。

2.2電路測試結(jié)果

采用信號發(fā)生器HP8640B產(chǎn)生0~15MHz的單頻正弦信號,經(jīng)相應(yīng)帶通濾波器濾波(各次諧波均小于-90dBc)后作為本電路的輸入信號,濾波后信號在AD6644AST-65輸入端幅度為-ldBFs。

AD6644AST-65輸出數(shù)字信號經(jīng)74LC574鎖存后,存儲于邏輯分析儀HPl6702A中。HPl6702A狀態(tài)分析時鐘取自AD6644AST-65的DRY管腳,該信號頻率和AD6644AST-65采樣時鐘頻率一致,為40MHz。

通過對邏輯分析儀HPl6702A每次存儲的數(shù)字信號進(jìn)行16384點(diǎn)FFT分析,可得到奈奎斯特帶寬內(nèi)總功率PΣ、輸入信號功率只以及總諧波失真與噪聲功率之和Pn+THD=PΣ-Ps。經(jīng)計算得到電路的有效位數(shù)ENOB=[SINAD(dB)-1.76]/6.02=[Ps (dB)-Pn+THD (dB)-1.76]/6.02。

圖3(a)、(b)、(c)為在三種不同測試條件下,AD6644AST-65輸出數(shù)字信號的FFT分析頻譜圖和有效位數(shù)ENOB。

圖3(c)表明,當(dāng)fin=0.96MHz、AD6644AST-65輸入端采用運(yùn)放AD8138直流耦合時,電路熱噪聲和諧波失真明顯增加,電路的有效位數(shù)ENOB約為10.74bit,比圖3(a)的ENOB小0.6bit左右。由此可見,有源器件對高速高分辨率ADC電路性能的影響是很大的。

理論分析和實際電路的測試結(jié)果都說明,高速高分辨率ADC電路設(shè)計應(yīng)選用低噪器件;當(dāng)輸入信號頻率較高時,應(yīng)選用低相位抖動的時鐘源;在進(jìn)行電路扳布局布線時,應(yīng)注意電源噪聲的抑制和減小數(shù)字電路對模擬電路的影響。

相關(guān)閱讀

相關(guān)文章

路的實現(xiàn)相關(guān)文章

ADC信相關(guān)文章

ADC信相關(guān)下載

精品文章

更多>>推薦閱讀

每月人物

如何選用元器件實現(xiàn)精密直流電源的設(shè)計

電池測試、電化學(xué)阻抗譜和半導(dǎo)體測試等測試和測量應(yīng)用需要準(zhǔn)確的電流和電壓輸出直流電源。在環(huán)境溫度變化為±5°C時,設(shè)備的電流和電壓控制精度需要...

模擬大咖對話:國產(chǎn)替代之后的中國模擬芯出路何在?

(電子發(fā)燒友網(wǎng)報道 文/章鷹)9月中旬以來,電子時報報道,業(yè)內(nèi)人士透露,隨著交付周期延長到6個月以上,模擬芯片供應(yīng)商德州儀器(TI)和安森美均已...

每周排行

創(chuàng)新實用技術(shù)專題

資料下載

- 基于樹莓派的移動機(jī)器人實現(xiàn)

- 人臉識別開源分享(原理圖+PCB+源碼)

- 在STM32上移植的一個穩(wěn)定可靠的FIFO

- PCB設(shè)計與封裝指導(dǎo)白皮書合集

- GW PBM PN網(wǎng)關(guān)將Profibus DP從站設(shè)備集成入PROFINET網(wǎng)絡(luò)

- Gowin數(shù)字信號處理器(DSP)用戶指南

- Gowin FPGA產(chǎn)品編程配置手冊

- 鋼絲繩傳動5自由度機(jī)器人機(jī)構(gòu)設(shè)計

- 半橋PWM控制芯片EG1165用戶手冊

- 熱電偶溫度數(shù)字變化模塊A1S68TD用戶參考手冊

精品文章

- ·Maxim并購Trinamic,電機(jī)控制芯片企業(yè)的前景在哪?

- ·電流檢測電路設(shè)計方案匯總(六款模擬電路設(shè)計原理圖詳解)

- ·12V轉(zhuǎn)交流220V逆變器工作原理

- ·Nikon D600拆解:日本電子鬼才設(shè)計藝術(shù)

- ·溫度控制器電路圖大全(六款溫度控制器電路設(shè)計原理圖詳解)

- ·PLC編程入門九步法則 少一步都不行

- ·電源設(shè)計中最常見的四種濾波電路原理及特點(diǎn)解析

- ·矩形波發(fā)生器電路設(shè)計方案匯總(六款模擬電路設(shè)計原理圖詳解

- ·樓梯開關(guān)雙控電路圖大全(七款樓梯開關(guān)雙控電路設(shè)計原理圖詳

- ·(經(jīng)典)電子工程師的設(shè)計經(jīng)驗筆記

用戶評論

共 0 條評論