3D IC技術(shù)蓬勃發(fā)展的背后推動力來自消費市場采用越來越復雜的互連技術(shù)連接硅片和晶圓。這些晶圓包含線寬越來越窄的芯片。

為了按比例縮小半導體IC,需要在300mm的晶圓上生成更精細的線條。據(jù)市場研究機構(gòu)VLSI Research(圖1)預測,雖然目前大多數(shù)量產(chǎn)的IC是基于55nm或55nm以下的設(shè)計節(jié)點,但這些設(shè)計規(guī)則將縮小至38nm或更小,到2013年甚至會縮小到27nm。

這些尺寸縮小了的IC設(shè)計促進了人們對高密度、高成本效益的制造與封裝技術(shù)的需求,進而不斷挑戰(zhàn)IC制造商盡可能地減少越來越高的固定設(shè)備投資成本。

許多3D應用仍使用傳統(tǒng)的球柵陣列(BGA)、方形扁平無引線(QFN)、引線柵格陣列(LGA)和小外形晶體管(SOT)封裝。不過,更多應用正在轉(zhuǎn)向兩種主要技術(shù):扇出晶圓級芯片尺寸封裝(WLCSP)和嵌入式裸片封裝。

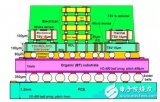

目前,扇出WLCSP主要用于采用BGA的多引腳數(shù)(超過120個引腳)應用。嵌入式裸片封裝技術(shù)適合用于引腳數(shù)較少的應用,這些應用將芯片和分立元件嵌入PCB基板,并采用微機電系統(tǒng)(MEMS)IC(圖2)。

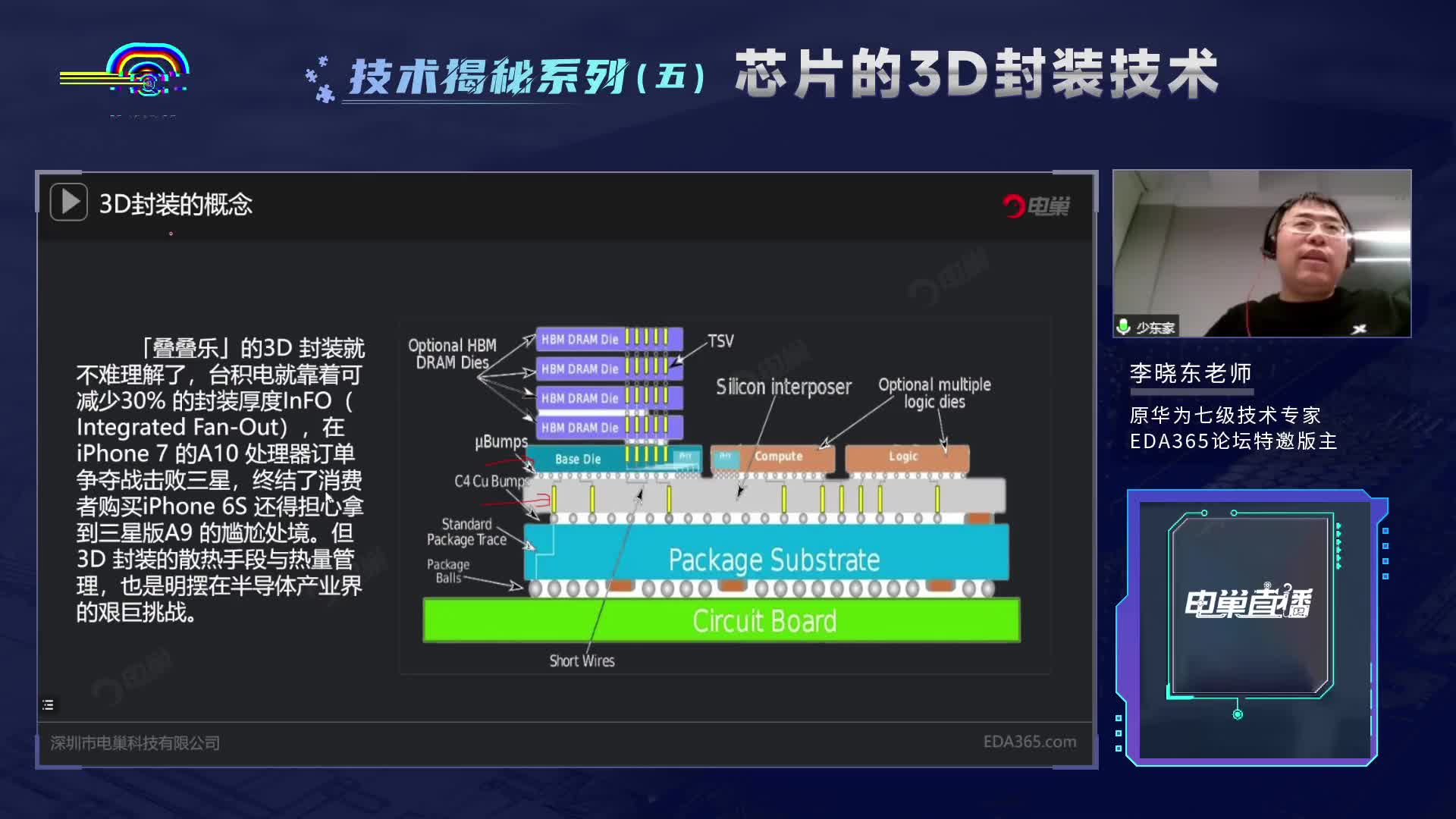

圖2:IC、MEMS器件和其它元件將采用了WLCSP和硅通孔(TSV)技術(shù)的無源器件組合在一起。

德州儀器(TI)的研究人員認為,WLCSP正在向標準化的封裝結(jié)構(gòu)發(fā)展。WLCSP可以包含WLCSP IC、MEMS IC和無源器件的組合,并且這些器件通過硅通孔(TSV)技術(shù)互連。TSV的底層可以是一個有源WLCSP器件、僅一個中介層或一個集成式無源中介層。頂層可以是一個IC、一個MEMS器件或一個分立器件(圖3)。

但不管是哪種封裝類型,隨著引腳數(shù)量和信號頻率的增加,預先規(guī)劃封裝選項的需求變得越來越重要。例如,帶有許多連接的引線鍵合封裝可能由于高感應系數(shù)而要求在芯片上提供更多的電源緩沖器。焊接凸點類型、焊盤以及焊球的放置也會極大地影響信號完整性。

TSV:言過其實還是事實?

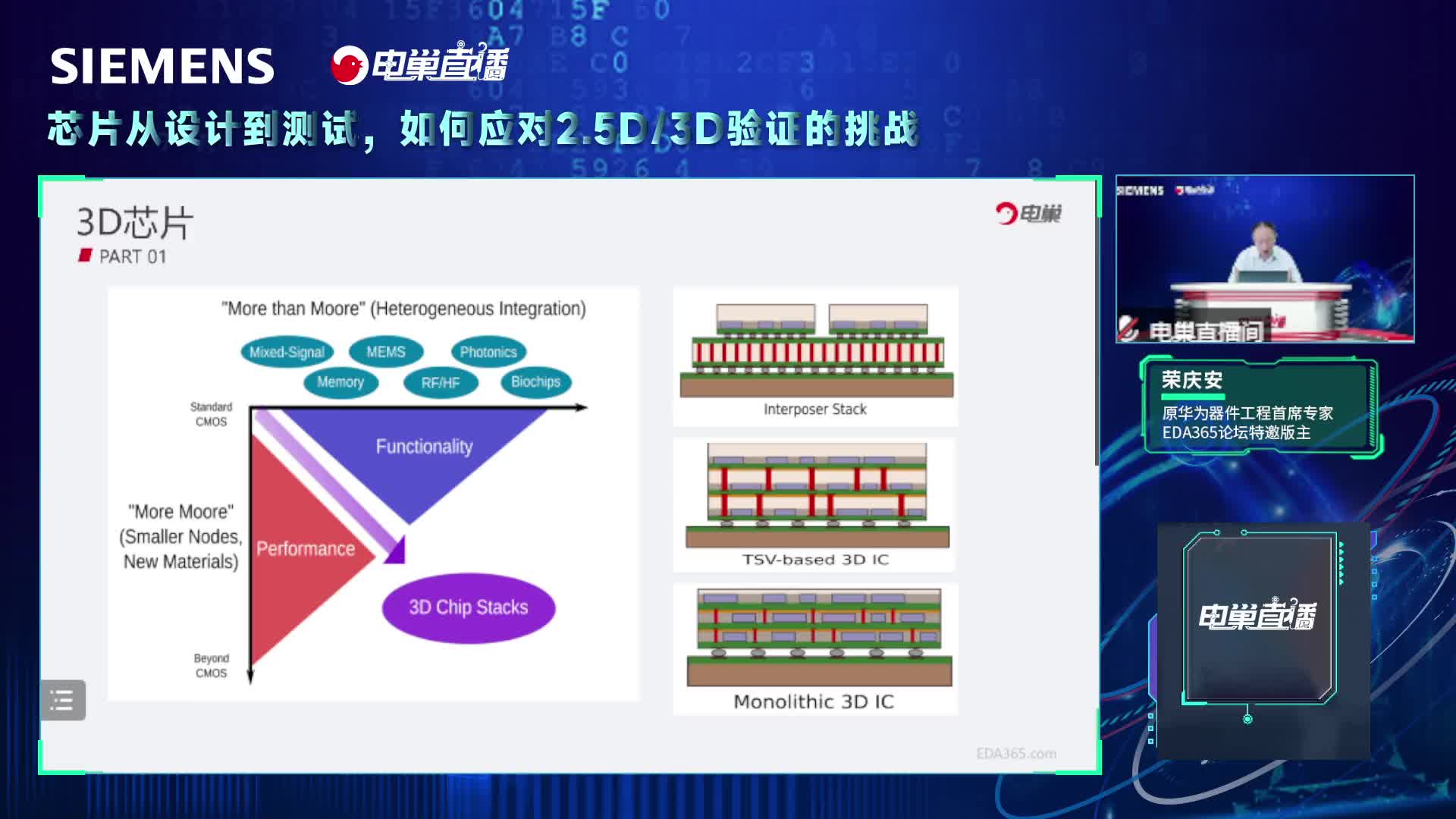

TSV技術(shù)本質(zhì)上并不是一種封裝技術(shù)方案,而只是一種重要的工具,它允許半導體裸片和晶圓以較高的密度互連在一起。基于這個原因,TSV在大型IC封裝領(lǐng)域中是一個重要的步驟。但TSV不是推動3D封裝技術(shù)進步的唯一方法。它們僅代表眾多材料、工藝和封裝開發(fā)的一個部分。

事實上,采用TSV互連的3D芯片還沒有為大批量生產(chǎn)作好準備。盡管取得了一些進步,但它們?nèi)灾饕抻糜贑MOS圖像傳感器、一些MEMS器件以及功率放大器。超過90%的IC芯片使用經(jīng)過驗證的引線鍵合方法進行封裝。

TI公司策略封裝研究和外協(xié)部門經(jīng)理Mario A.Bolanos在今年的ConFab會議上指出,在3D芯片中使用TSV面臨許多挑戰(zhàn)。這些挑戰(zhàn)包括:缺少電子設(shè)計自動化(EDA)工具,需要極具成本效益的制造設(shè)備和工藝,與熱問題、電遷移和熱機械可靠性相關(guān)的良率和可靠性數(shù)據(jù)不達標,以及復合良率損失及已知合格芯片(KDG)數(shù)據(jù)等。

與在750μm厚的硅晶圓上制造的傳統(tǒng)IC不同,3D IC要求晶圓非常薄,厚度通常約100μm甚至更薄。鑒于這種超薄晶圓的脆弱性,迫切需要極其專業(yè)的臨時鍵合和解鍵合設(shè)備,以確保晶圓結(jié)構(gòu)的完整性,特別是在蝕刻和鍍金工藝期間的高處理溫度和應力下。在鍵合完成后,晶圓要執(zhí)行一個TSV背面工藝,然后進行解鍵合步驟。這些典型步驟可產(chǎn)生更高的良率水平,從而支持更具成本效益的批量生產(chǎn)。

目前,在鍵合和工藝溫度及相關(guān)可靠性方面還缺少TSV標準。晶圓位置的TSV分配標準化也是如此。如果有足夠多的IC制造商來研究這些問題,那么在擴展TSV的互連作用方面還可以取得更大的進展。超過200℃至300℃的高工藝溫度對于TSV的經(jīng)濟實現(xiàn)來說是不可行的。

提供3D集成技術(shù)的知識產(chǎn)權(quán)(IP)的Ziptronix公司將直接邦定互連(DBI)技術(shù)授權(quán)給了Raytheon Vision Systems公司。據(jù)Ziptronix公司介紹,低溫氧化物邦定DBI技術(shù)是3D IC(圖4)的一種高成本效益解決方案。

但是,許多半導體IC專家認為半導體行業(yè)正處于選擇2D(平面)和3D設(shè)計的十字路口。考慮到制造、設(shè)計、工藝和掩膜成本,他們發(fā)現(xiàn)在從45nm設(shè)計節(jié)點轉(zhuǎn)向32nm和28nm設(shè)計時,成本會增加三倍至四倍。在蝕刻和化學蒸氣拋光以及處理應力效應問題等方面還需很多改進,這使得3D封裝挑戰(zhàn)愈加嚴峻。而這正是TSV技術(shù)的合適切入點。

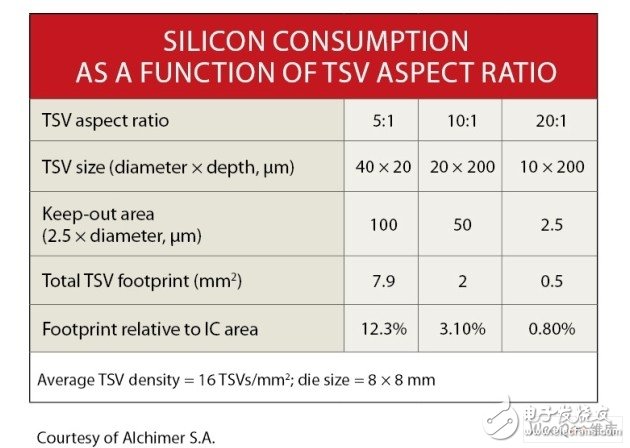

法國的Alchimer S.A.是一家提供用于半導體IC互連的納米沉積薄膜的廠商,該公司已經(jīng)驗證,與高寬比為5:1(見表)的TSV相比,高寬比為20:1的TSV可以為IC芯片制造商每300mm晶圓節(jié)省超過700美元。這是通過減少互連所需的裸片面積實現(xiàn)的。

Alchimer公司利用現(xiàn)有面向移動應用的3D堆棧對TSV的成本和空間消耗建模。這個堆棧包括一個低功耗微處理器、一個NAND存儲器芯片和一個65nm工藝節(jié)點上制造的DRAM芯片。芯片通過約1000個TSV互連,并對高寬比5:1、10:1和20:1下的處理器裸片進行了計算。

IBM、瑞士的école Polytechnique Fédérale de Lausanne(EPFL)和瑞士聯(lián)邦理工學院(ETH)正在借助微流體MEMS技術(shù)(圖5)聯(lián)合開發(fā)面向3D IC(使用TSV)的微冷卻技術(shù)。這項被稱為CMOSAIC的合作正在探討一種多核3D堆棧架構(gòu),其互連密度范圍為100到10000個連接/mm2。

圖5:未來的3D堆棧可能包含處理器、存儲器、邏輯和模擬及RF電路,所有這些都通過TVS互連。流體通過MEMS微通道實現(xiàn)冷卻。

IBM/瑞士團隊計劃用單相流體和兩相冷卻系統(tǒng)設(shè)計微通道。納米表面將在幾個毫米的芯片中用管道輸送包括水和環(huán)保的制冷劑在內(nèi)的冷卻液,從而達到吸引熱量和散熱的目的。一旦流體以蒸氣形式離開電路,冷凝器會使蒸氣回復液體狀態(tài),然后再泵回芯片用于冷卻。

引線鍵合和倒裝芯片

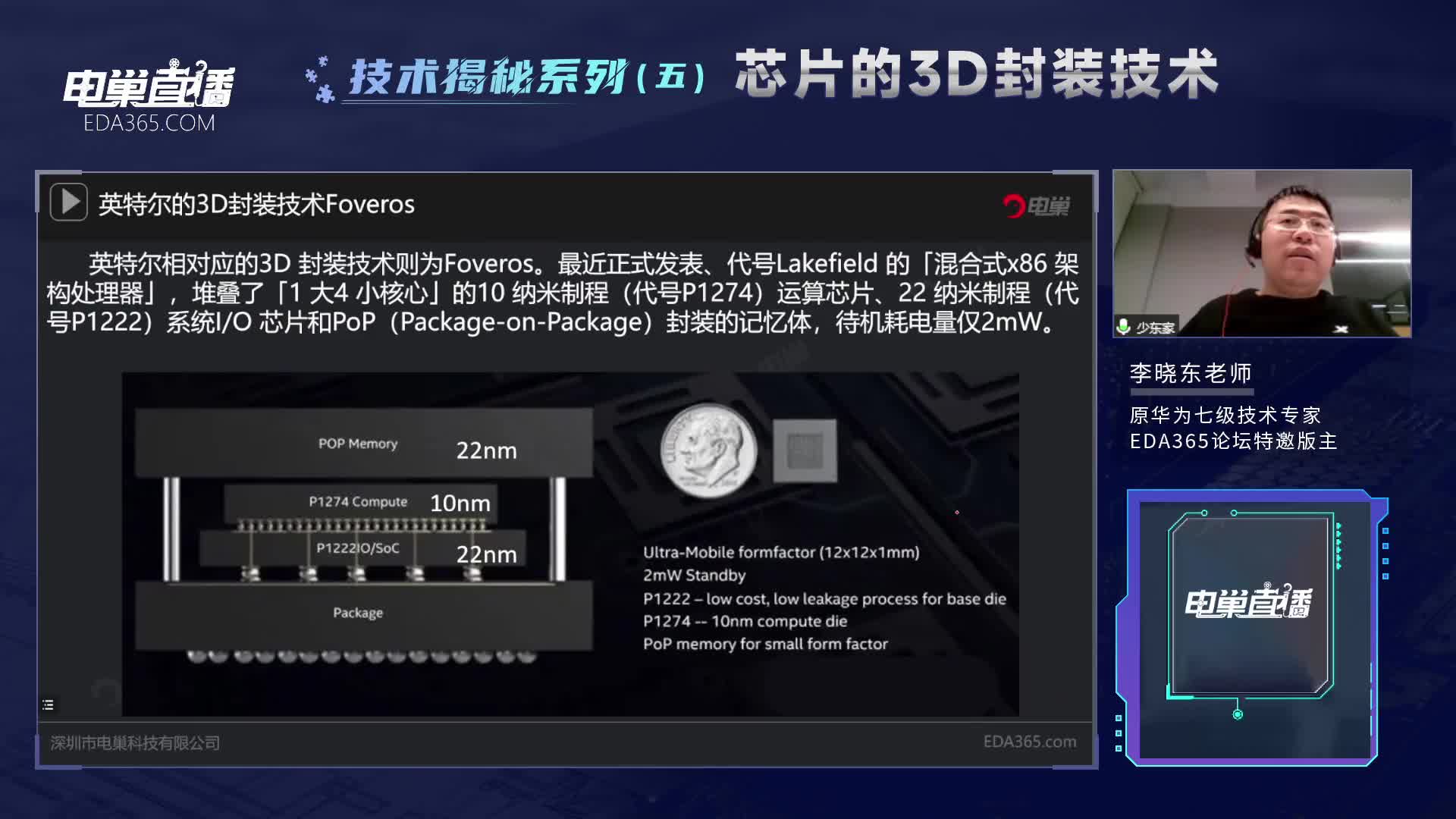

引線鍵合和倒裝芯片(flip-chip)互連技術(shù)當然不會坐以待斃。許多倒裝芯片晶圓凸點技術(shù)取得了很大的進步,包括使用共熔倒裝芯片泵、銅柱和無鉛焊接。最新的封裝發(fā)展包括使用封裝上封裝(PoP)方法、系統(tǒng)級封裝(SiP)、無引線(QFN)封裝以及它們的衍生技術(shù)。

3D結(jié)構(gòu)已經(jīng)享譽封裝領(lǐng)域多年。在帶有引線鍵合的堆疊式裸片結(jié)構(gòu)中使用BGA封裝已經(jīng)近十年了。例如在2003年,意法半導體展示了一款采用BGA的10片堆疊結(jié)構(gòu),這在當時是創(chuàng)了記錄的。

對于高密度和功能強的手持產(chǎn)品來說,像PoP概念這樣的3D方法一定會引起人們的特別關(guān)注。設(shè)計工程師必須仔細考慮兩個問題:熱循環(huán)和跌落測試可靠性。兩者都是封裝材料質(zhì)量和可靠性的函數(shù)。當PoP結(jié)構(gòu)的底層互連間距從0.5mm變?yōu)?.4mm、頂層互連間距從0.4mm變?yōu)?.5mm時,這將變得更加重要。

三星電子(Samsung Electronics)發(fā)布了一款0.6mm高、多裸片、8芯片的封裝,主要用于高密度存儲器應用。據(jù)該公司透露,這種封裝最初是為32GB存儲器設(shè)計的,厚度只有傳統(tǒng)8芯片存儲器棧的一半,能為高密度多媒體手機和其它移動設(shè)備提供厚度和重量均縮減40%的存儲器解決方案。

這種封裝的重要創(chuàng)新之處是使用了30nm NAND閃存芯片,每顆芯片的厚度只有15 μm。三星公司設(shè)計了一種超薄技術(shù)來克服傳統(tǒng)技術(shù)的局限性,即厚度在30μm以下時IC芯片抵抗外部壓力的限制。此外,這種新的封裝技術(shù)可以被應用于其它多芯片封裝(MCP),如SiP和PoP。

“這一封裝技術(shù)的發(fā)展為在目前的移動產(chǎn)品設(shè)計中整合更高密度和更多功能提供了最佳解決方案,從而使設(shè)計工程師能更自由地創(chuàng)造富有吸引力的設(shè)計,以滿足當今用戶對不同風格以及超薄喜好的需求。”三星公司封裝開發(fā)部門副總裁Tae Gyeong Chung表示。

市場發(fā)展也在影響QFN封裝領(lǐng)域。德國的Fraunhofer IZM公司開發(fā)出了一種聚合物內(nèi)埋置芯片(chip-in-polymer)工藝,將沖擊和震動保護嵌進芯片中,并使其互連距離縮短,從而增強芯片性能。這種工藝先使芯片變薄,然后將其粘附到很薄的基板上。

再用帶樹脂涂覆的銅全部覆蓋表面(樹脂層厚約80μm,銅表面厚5μm)。樹脂被固化,互連過孔通過激光鉆孔至連接焊盤,并用金屬電鍍。然后頂層上的再分配層被蝕刻掉銅。

這種工藝已經(jīng)在QFN等標準封裝的商業(yè)化生產(chǎn)中得到優(yōu)化,而無需專門的設(shè)備或其它延遲。采用聚合體嵌入式QFN(其本質(zhì)上是引線被芯片底面的焊盤取代的無引線方形封裝)是HERMES項目的一部分。

HERMES由Fraunhofer公司和另外10家歐洲工業(yè)和學術(shù)機構(gòu)組成,其目標是推進芯片和有源與無源器件的嵌入,以實現(xiàn)更多功能的集成和更高的密度。該技術(shù)基于PCB制造和裝配實踐的采用以及標準化的硅裸片,強調(diào)精細間距互連、大功率性能和高頻兼容性。

選擇QFN封裝是因為它在包含微控制器IC的小型超薄設(shè)備中比較常見。Fraunhofer的研究人員相信,QFN將接管由其它類型封裝控制的許多利基應用領(lǐng)域。嵌入式QFN包含一個厚度僅50μm左右的5x5mm大小芯片。封裝本身的尺寸是100x100mm。芯片上的84個I/O引腳之間的間距是100μm(封裝上為400μm)。

馬來西亞的Unisem Berhad公司也發(fā)布了一種高密度引線框(leadframe)技術(shù):引線框柵格陣列(LFGA),它能提供與BGA相當?shù)拿芏取T摴颈硎荆摷夹g(shù)為兩層FPGA封裝提供了高成本效益的替代方案。與QFN封裝相比,它有更短的引線鍵合長度。此外,它能在5.5mm2的面積中容納10x10mm、72引線的QFN封裝。

“這種封裝能提供更好的外形尺寸,同時具有更高的I/O密度和更好的熱性能與電氣性能。而且它更薄,最重要的是,能在前端裝配中提供高得多的良率。”封裝開發(fā)人員T.L.Li表示。

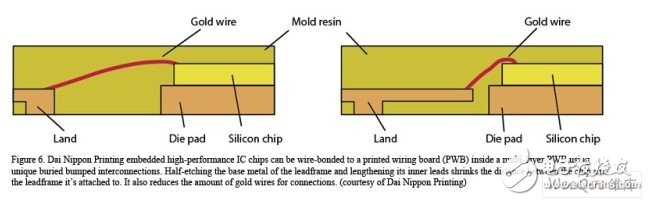

正在研究將芯片嵌入進各種介質(zhì)的其它公司還包括Dai Nippon Printing。該公司成功地將引線鍵合至印刷線路板(PWB)的高性能IC芯片嵌入多層PWB中,其成功之處在于獨特的埋入式凸出互連技術(shù)。PWB可在任意層間互連(通過孔連接),焊凸點則由通過絲網(wǎng)印刷術(shù)形成的高導電性錫膏生成。

對引線框的基礎(chǔ)金屬進行半蝕刻并使其內(nèi)部引線變長將大幅縮短芯片與其連接的引線框之間的距離,同時顯著減少用于連接的金線數(shù)量,最終降低制造成本(圖6)。PWB內(nèi)包含超過700個引腳的IC將在今年開始批量生產(chǎn)。有源和無源器件可以同時量產(chǎn)。

開發(fā)環(huán)氧助焊劑材料的工作還在進行,這種材料能改善傳統(tǒng)錫銀銅(SnAgCu)的熱循環(huán)和跌落試驗可靠性缺陷。開發(fā)這種材料將有助于提升采用PoP的3D IC技術(shù)。雖然PoP制造采用常用的錫鉛(SnPb)焊接合金(比SnAgCu材料更具優(yōu)勢),但仍需要一種無鉛化合物來處理面向消費電子產(chǎn)品的大型高密度3D PoP結(jié)構(gòu)。

Henkel公司最新開發(fā)的多核LF620是一種無鉛助焊劑,可用于大范圍的封裝應用。這種免清洗的無鹵化物、無鉛材料采用新的化學活性劑構(gòu)成。因此,它通過焊盤內(nèi)連接盡可能降低了CSP的空洞率,具有良好的接合性能,并在大量表面處理工藝下實現(xiàn)了卓越的可焊接性。

電子發(fā)燒友App

電子發(fā)燒友App

評論