封裝對于集成電路來講是最主要的工具,先進(jìn)的封裝方法可以顯著地幫助提高IC性能。了不起的是,這些技術(shù)中有許多已經(jīng)足夠成熟,而且已經(jīng)存在足夠長的時間,現(xiàn)在甚至連初創(chuàng)公司和大學(xué)都可以使用它們。

雖然這些技術(shù)中已經(jīng)被代工廠所采納,但最新最有前途的一項技術(shù)——chiplets,還不成熟。英特爾的Ramune Nagisetty表示,對于提高技術(shù)水平,目前最缺的是在先進(jìn)封裝中混合和匹配硅元件創(chuàng)造更標(biāo)準(zhǔn)化的接口。這樣做的目的可以降低在這個生態(tài)系統(tǒng)中發(fā)揮作用的障礙。

英特爾作為美國先進(jìn)半導(dǎo)體工藝技術(shù)的最后堡壘之一,他們認(rèn)為先進(jìn)的封裝技術(shù)將作為未來發(fā)展的關(guān)鍵技術(shù)之一。Nagisetty表示,英特爾對其每一個封裝載體都有一個技術(shù)路線圖,就像它一直對工藝技術(shù)有路線圖一樣。

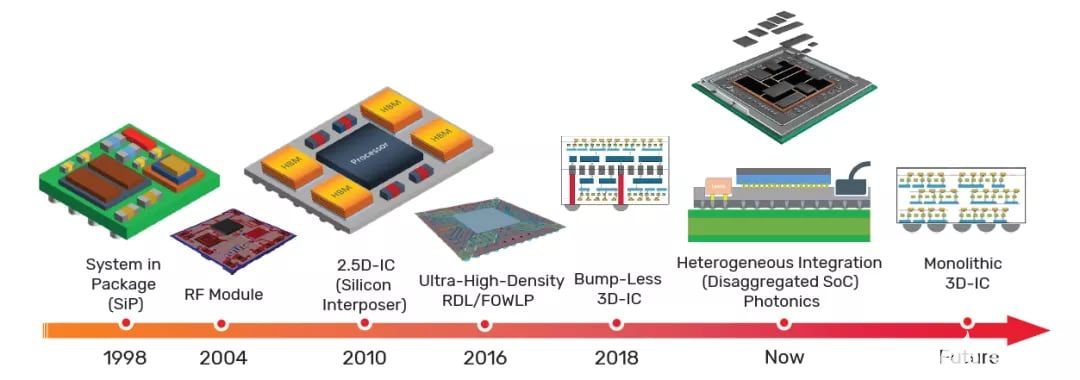

封裝一直是半導(dǎo)體行業(yè)沒有多大吸引人的領(lǐng)域,但大約15年前,它開始走向舞臺,封裝技術(shù)可能成為一個性能瓶頸,但只要稍加創(chuàng)新,不僅可以避免這個瓶頸,而且新的封裝方法可以提高IC性能。

英特爾這樣做已經(jīng)有一段時間了。據(jù)Nagisetty介紹,為了提供異構(gòu)芯片的高密度互連,英特爾在2008年提出了嵌入式多芯片互連橋接技術(shù)(EMIB)技術(shù)。

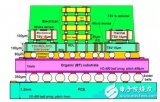

EMIB是2.5D技術(shù)的一個變種。2.5D封裝的常用方法是使用硅中介層,它是夾在兩片芯片之間的一層帶孔的硅。英特爾認(rèn)為中介層有些太大,所以它的EMIB使用了一個有多個路由層的橋接器。

Nagisetty:“新技術(shù)在開始使用之前需要一個臨界點,”轉(zhuǎn)折點是基于神經(jīng)網(wǎng)絡(luò)的人工智能架構(gòu)。 “這是很重要的一點——它顯示了神經(jīng)網(wǎng)絡(luò)的可行性,并且在封裝內(nèi)產(chǎn)生了加速器和高帶寬內(nèi)存——這為將內(nèi)存嵌入封裝內(nèi)奠定了根基。”

英特爾于2014年首度發(fā)表EMIB,表示該技術(shù)是2.5D封裝的低成本替代方案

如今在傳統(tǒng)半導(dǎo)體工藝微縮技術(shù)變得越來越復(fù)雜且昂貴的此刻,像EMIB這樣能實現(xiàn)高性能芯片組的低成本、高密度封裝技術(shù)日益重要。臺積電(TSMC)所開發(fā)的整合型扇出技術(shù)(InFO)也是其中一種方案,已被應(yīng)用于蘋果(Apple) iPhone的A系列處理器。

英特爾一直將EMIB幕后技術(shù)列為“秘方”,包括所采用的設(shè)備以及在芯片之間打造簡化橋接的方法;不過該公司打算將AIB變成一種任何封裝技術(shù)都能使用、連接“小芯片”的標(biāo)準(zhǔn)接口,以催生一個能支持自家產(chǎn)品的零件生態(tài)系統(tǒng)。

從歷史上看,半導(dǎo)體行業(yè)的總體發(fā)展將越來越多的功能集成到芯片上,但對于一些先進(jìn)集成電路設(shè)計來說,這或許是不可能的。

首先,一個公司不可能把一些應(yīng)用程序所需的所有電路放在一個巨大的模具上,從生產(chǎn)的角度來看,模具的尺寸是有限的。

Nagisetty指出:“推動這一趨勢的第二點是,重復(fù)使用的設(shè)計成本不斷上升,以及特定技術(shù)節(jié)點對IP可移植性的需求。”無論是針對移動設(shè)備還是高性能,邏輯技術(shù)正變得越來越專業(yè)化,在先進(jìn)集成電路設(shè)計中,幾乎不需要在相同的技術(shù)節(jié)點上實現(xiàn)SerDes。更重要的是,有可能將某一項技術(shù)(例如SerDes)定制為一個技術(shù)節(jié)點。

Nagisetty引用了Intel Stratix FPGA的例子:有一個Stratix FPGA菜單,在六個不同的技術(shù)節(jié)點上執(zhí)行,可從三個不同的工廠獲得。“我認(rèn)為Stratix是第一個達(dá)到每秒58千兆字節(jié)的產(chǎn)品。”“它使我們更具競爭力,并率先以高速SerDes進(jìn)入市場。”

使用高級封裝的第三個原因是獲得敏捷性和靈活性。“對于不同技術(shù),chiplets在混合和匹配的價值正變得越來越明顯。”

Nagisetty表示,英特爾的Kaby Lake G和Lakefield產(chǎn)品就是兩個很好的例子。

通過Kaby Lake G,我們將第三方IP整合到我們的封裝中,我們能夠為高性能手機(jī)游戲創(chuàng)造一個更小的形式。這里的第三方IP指的就是AMD的Radeon加速器。

這是利用先進(jìn)封裝提高最終使用性能的一個明顯例子。

Intel和AMD雖說是死對頭,但是去年雙方竟然意外合體,合作推出了Kaby Lake-G系列處理器,Kaby Lake G使用英特爾的EMIB 2.5D方法,而Lakefield則依靠die堆疊- 3D堆疊。英特爾稱其3D堆疊系統(tǒng)為Foveros。它使用Intel的CPU搭配AMD的Radeon顯卡及HBM2顯存,圖形性能非常亮眼。不過Kaby Lake-G的市場化不算成功,現(xiàn)在Intel決定停產(chǎn)這款A(yù)/I合作的處理器了。根據(jù)Intel發(fā)布的通知,Kaby Lake-G系列從10月7日開始退役,2020年1月31日為最后的訂單日,2020年7月31日為最后的出貨日,之后就完全停產(chǎn)了。

Lakefield是證明了先進(jìn)封裝可以帶來最小X-Y引腳。” 用戶可以從性能或外形上看到好處。

英特爾開發(fā)了一組豐富的封裝技術(shù),而且為了使事情更有簡單,它們可以混合匹配。例如,英特爾推出的“Co-EMIB”,這是EMIB和Foveros的結(jié)合。

2019年,英特爾推出了兩種更先進(jìn)的封裝變體,全向互聯(lián)(ODI),從架構(gòu)的角度來看,它是EMIB和Foveros的下一個演進(jìn)步驟,英特爾能夠?qū)⒍鄠€芯片堆疊在玻璃纖維基板的上方,相互之間的上方;以及基板的壓痕和空腔內(nèi)。ODI由類似EMIB的硅片組成,可以在兩個硅片之間實現(xiàn)高密度布線(如GPU和內(nèi)存堆棧,或SoC和核心邏輯);以及作為硅片凸點延伸到基板的銅極。它會帶來若干好處,包括通過穿硅通孔(tsv)向堆疊中的頂部管芯輸送功率。

英特爾、臺積電和其他公司正在研究一種被稱為銅-銅混合鍵合的方法,這是堆疊技術(shù)的另一種變體,這可能會帶來3D IC的創(chuàng)新,并可以將更多的DRAM芯片連接起來,這種組合被稱為DRAM cubes。

我們是否有明確的路徑來不斷改進(jìn)這些封裝技術(shù),就像連續(xù)的生產(chǎn)過程節(jié)點總是被繪制出來的那樣?

Nagisetty:“我們的每一個封裝載體都有一個技術(shù)路線圖,”“所以,我們有一個中介層,它可以降低溝道高度。Foveros將達(dá)到25微米。混合鍵合將從10微米開始,并逐漸降低。”

Kaby Lake G的例子激發(fā)了芯片設(shè)計者們的夢想,即混合和匹配來自不同供應(yīng)商的功能,而不僅僅是一個供應(yīng)商。這是chiplets的關(guān)鍵概念。

從商業(yè)角度來看,chiplets方法很有意義。芯片上高度集成的SoC成本可能非常高。此外,這種高度集成的半導(dǎo)體系統(tǒng)的復(fù)雜性使制造更具挑戰(zhàn)性;較高的復(fù)雜性與產(chǎn)量損失有直接關(guān)系。

美國國防高級研究計劃局(DARPA)正在支持一項計劃,以推動chiplets市場。DARPA對這項技術(shù)的看法是:

由于初始原型成本高和對替代材料集的要求等因素,最先進(jìn)的SoC的整體特性并不總是為國防部(DoD)或其他小體積應(yīng)用所接受。為了增強(qiáng)下一代產(chǎn)品的整體系統(tǒng)靈活性和減少設(shè)計時間,微電子綜合常用功能整合及微電子知識產(chǎn)權(quán)產(chǎn)品重新優(yōu)化利用計劃(簡稱CHIPS)尋求在IP重用中建立一個新的范例。

CHIPS 項目的主要目標(biāo),是開發(fā)出全新的技術(shù)框架,將如今電子產(chǎn)品中插滿芯片的電路板壓縮成為尺寸小得多的集成“微芯片零件組”。這種框架會將受知識產(chǎn)權(quán)保護(hù)的微電子模塊與其功能整合成“微芯片零件”。這些微芯片零件能夠?qū)崿F(xiàn)數(shù)據(jù)存儲、信號處理和數(shù)據(jù)處理等功能,并可以隨意相連,如拼圖一樣拼成“微芯片零件組”。

CHIPS項目有望催生更多新技術(shù)產(chǎn)品,如更小的集成電路板替代品,要求高速數(shù)據(jù)轉(zhuǎn)換和強(qiáng)大處理性能緊密結(jié)合的高帶寬射頻系統(tǒng),通過整合各種處理以及加速功能的 “微芯片零件”,還可以得到能夠從大量雜亂數(shù)據(jù)中過濾出可用數(shù)據(jù)指令的快速機(jī)器學(xué)習(xí)系統(tǒng)。

與更復(fù)雜的SoC相比,使用chiplets可以顯著降低成本。這張圖是AMD的Lisa Su在2017年IEDM會議上發(fā)表的一篇論文中展示的,并被開放計算項目復(fù)制。

美國芯片法案確實專門為高級封裝研究進(jìn)行了資助,但它沒有特別提到DARPA的芯片計劃。

Nagisetty介紹,英特爾當(dāng)然參與了DARPA的芯片計劃。“Stratix FPGA是這方面的核心。”

CHIPS成功的關(guān)鍵總體來說是chiplets技術(shù),它將創(chuàng)造更標(biāo)準(zhǔn)化的接口,這樣其他公司的芯片就可以連接起來。

英特爾的另一項發(fā)明——AIB接口總線技術(shù)

開發(fā)通用接口是一項艱巨的任務(wù),因為要考慮許多因素,并且并非所有應(yīng)用程序都必須以相同的方式權(quán)衡利弊。接口技術(shù)中要考慮的一些因素是成本,面積,每位能量,帶寬,等待時間,距離,可伸縮性以及在不同過程節(jié)點中實現(xiàn)的能力。幸運(yùn)的是,在DARPA的支持下,英特爾已經(jīng)使其高性能的高級接口總線(AIB)用于通過git-hub的開源框架公開免費(fèi)地連接小芯片。該接口可提供任何競爭解決方案中最高的帶寬和最低的每位功率,并實現(xiàn)接近單片的互連性能。英特爾多年來一直在生產(chǎn)帶有該接口的產(chǎn)品,目前在Stratix 10 FPGA系列上提供該產(chǎn)品,以將chiplets連接到FPGA架構(gòu)。隨著英特爾在業(yè)界的影響力以及正在采用的新興財團(tuán),AIB有望成為chiplets互連標(biāo)準(zhǔn)。

Nagisetty:“我相信它將發(fā)展成為一個生態(tài)系統(tǒng),創(chuàng)新將被開啟,它類似于開發(fā)電路板的方式——那里有像PCI Express這樣的東西——允許公司基于一個接口標(biāo)準(zhǔn)來構(gòu)建產(chǎn)品。”

早期,有很多的復(fù)雜性,以及商業(yè)模式需要解決,”她繼續(xù)說道,“但是我喜歡,人們可以參與這個生態(tài)系統(tǒng)。以前,屏障非常高。但現(xiàn)在,有一些初創(chuàng)企業(yè)和大學(xué)參與進(jìn)來。”

但Nagisetty表示,如果一個組織能夠?qū)τ赾hiplets技術(shù)的標(biāo)準(zhǔn)創(chuàng)建進(jìn)行指導(dǎo),那將會大有裨益。開放計算項目(OCP)是一個嘗試填補(bǔ)這一空白的組織,其中他們提議的ODSA項目旨在在小芯片之間創(chuàng)建一個開放的接口,以便可以將多個供應(yīng)商的同類最佳小芯片組合在一起以創(chuàng)建定制產(chǎn)品。

OCP首先注意到,數(shù)據(jù)中心將不得不處理不斷增加的新工作負(fù)載。目前,針對任何給定的新工作負(fù)載優(yōu)化硅系統(tǒng)的最佳解決方案是創(chuàng)建SoC。但是,這樣做是很昂貴的。為新興工作負(fù)載降低硅系統(tǒng)成本的一種方法是使用chiplets技術(shù)——這就是OCP參與chiplets的方式。

根據(jù)OCP的說法,不同的公司在開發(fā)chiplets技術(shù)時,至少在一定程度上依賴于內(nèi)部開發(fā)的設(shè)計工具,而且所有chiplets接口都是專有的。“ODSA試圖通過一個開放的生態(tài)系統(tǒng)市場,將chiplet和SIP技術(shù)的發(fā)展大眾化,從而面向更大的大眾市場。”

責(zé)任編輯:YYX

電子發(fā)燒友App

電子發(fā)燒友App

評論