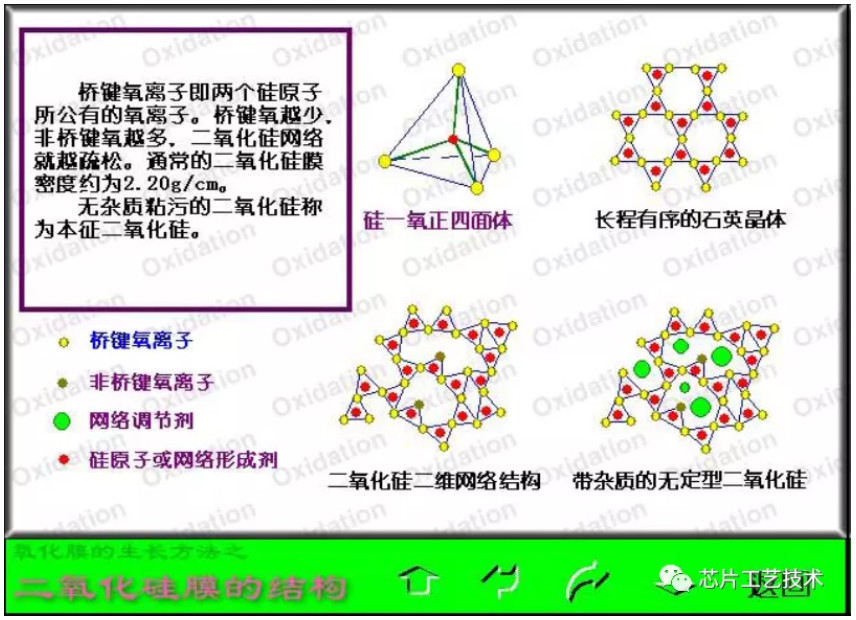

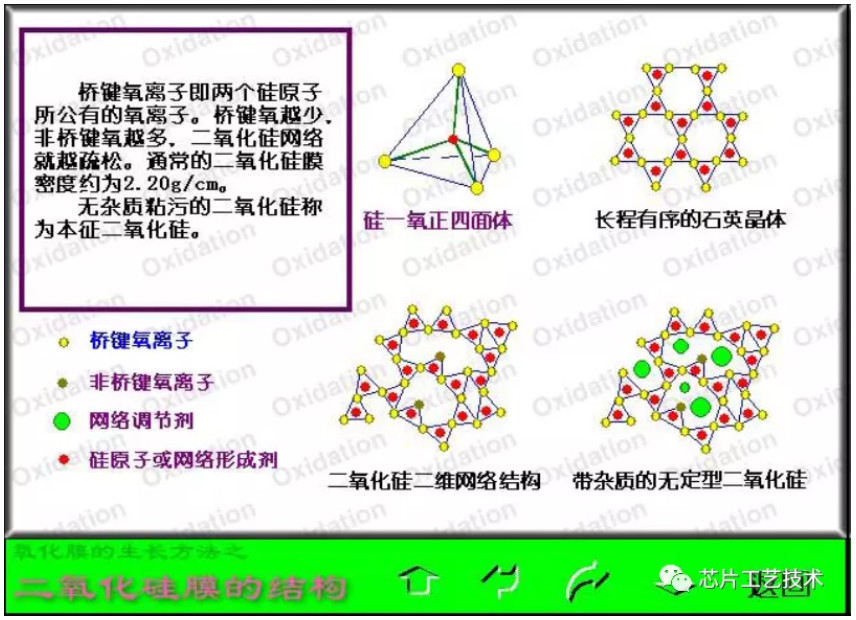

在自然界中sio2二氧化硅的存在是非常廣泛的,本內(nèi)容解釋了sio2是什么意思,sio2的物理性質(zhì)是什么,讓大家充分了解sio2

2011-12-13 10:41:13 20242

20242 關(guān)鍵詞:玻璃陶瓷;氫氟酸;蝕刻條件;蝕刻速率;機(jī)制 引言 我們江蘇華林科納研究了氧化鎂-氧化鋁-二氧化硅玻璃陶瓷在氫氟酸中的腐蝕條件和機(jī)理。結(jié)果表明,在室溫下,非晶相的腐蝕速率是純堇青石晶體的218

2022-01-04 14:39:28 1655

1655

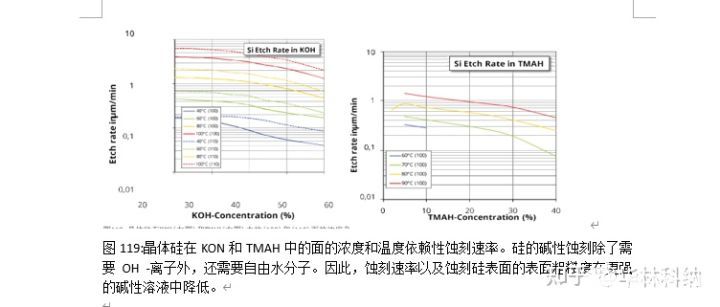

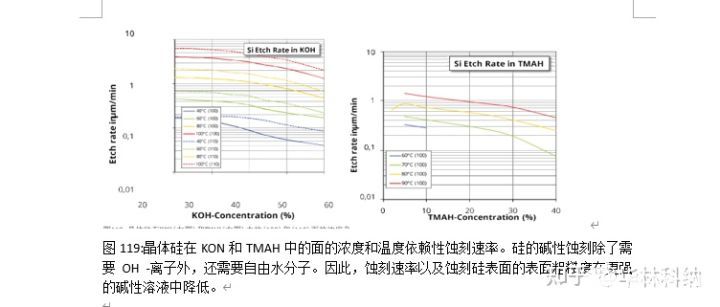

蝕刻機(jī)理 諸如KOH-、NaOH-或TMAH-溶液的強(qiáng)含水堿性介質(zhì)蝕刻晶體硅通孔 硅+ 2 OH- + 2 H O ?硅(OH) + H ?二氧化硅(OH) 2- + 2 H 因?yàn)椴煌娴腟i原子

2022-07-11 16:07:22 1344

1344

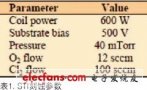

等離子體圖形化刻蝕過程中,刻蝕圖形將影響刻蝕速率和刻蝕輪廓,稱為負(fù)載效應(yīng)。負(fù)載效應(yīng)有兩種:宏觀負(fù)載效應(yīng)和微觀負(fù)載效應(yīng)。

2023-02-08 09:41:26 2467

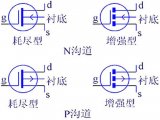

2467 鋁)的柵極和隔著氧化層(O-絕緣層SiO2)的源極施加電壓,產(chǎn)生電場(chǎng)的效應(yīng)來控制半導(dǎo)體(S)導(dǎo)電溝道開關(guān)的場(chǎng)效應(yīng)晶體管。由于柵極與源極、柵極與漏極之間均采用SiO2絕

2023-11-18 08:11:02 1325

1325

干法刻蝕技術(shù)是一種在大氣或真空條件下進(jìn)行的刻蝕過程,通常使用氣體中的離子或化學(xué)物質(zhì)來去除材料表面的部分,通過掩膜和刻蝕參數(shù)的調(diào)控,可以實(shí)現(xiàn)各向異性及各向同性刻蝕的任意切換,從而形成所需的圖案或結(jié)構(gòu)

2024-01-20 10:24:56 1114

1114

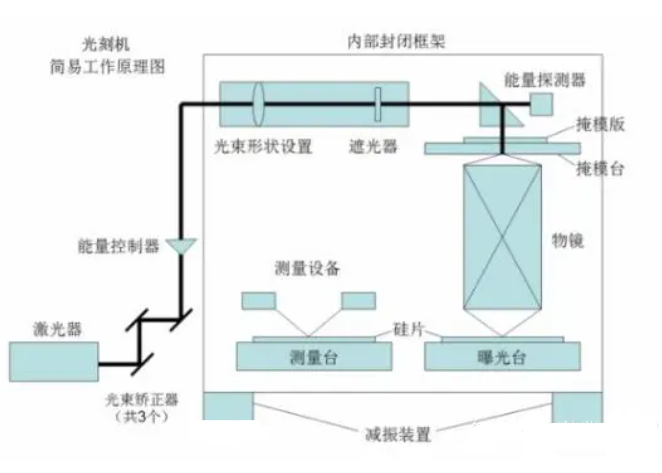

在半導(dǎo)體加工工藝中,常聽到的兩個(gè)詞就是光刻(Lithography)和刻蝕(Etching),它們像倆兄弟一樣,一前一后的出現(xiàn),有著千絲萬縷的聯(lián)系,這一節(jié)介紹半導(dǎo)體刻蝕工藝。

2024-01-26 10:01:58 552

552

(干法刻蝕硅)17、 RIE SiO2 (干法刻蝕二氧化硅)18、 RIE Si3N4 (干法刻蝕氮化硅)19、 RIE Al、AlN、Ti、TiN (干法刻蝕金屬,包括干法刻蝕鋁、干法刻蝕氮化

2015-01-07 16:15:47

AOE刻蝕氧化硅可以,同時(shí)這個(gè)設(shè)備可以刻蝕硅嗎?大致的氣體配比是怎樣的,我這里常規(guī)的刻蝕氣體都有,但是過去用的ICP,還沒有用過AOE刻蝕硅,請(qǐng)哪位大佬指點(diǎn)一下,謝謝。

2022-10-21 07:20:28

我正在使用 CY8C5867LTI-LP025。

我知道我需要使用 SIO 端口來使用 I2C、UART 等。

SPI通信是否也需要使用 SIO 端口?

2024-03-06 06:23:39

在上一講已經(jīng)知道了 FPGA就實(shí)現(xiàn)技術(shù)是可以分成三種不同 FPGA 的結(jié)構(gòu)特點(diǎn)、實(shí)現(xiàn)的機(jī)理,這三種 FPGA 分別是基于 SRAM 技術(shù)、基于反熔絲技術(shù)、基于 E2PROM/FLASH技術(shù)。就電路結(jié)構(gòu)...

2021-07-30 06:39:06

本帖最后由 gk320830 于 2015-3-9 22:04 編輯

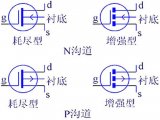

N溝道耗盡型MOS管的二氧化硅中摻有大量的正離子(不是摻入低價(jià)元素形成的P型半導(dǎo)體),也就是說在不加電的情況下G(柵極)也

2009-07-04 16:00:27

精煉、晶體生長(zhǎng)和晶圓形成。硅精煉開始于在大約 2000 °C 的電弧爐中用碳源還原二氧化硅。碳有效地從 SiO2 分子中“拉”出氧,從而將 SiO2 化學(xué)還原為大約 98% 的純硅,稱為冶金級(jí)硅

2021-07-06 09:32:40

逆變器3.第一步將是形成n(1)用 SiO2(氧化物)保護(hù)層覆蓋晶圓(2)刪除應(yīng)構(gòu)建 n 阱的層(3)植入或擴(kuò)散 n 摻雜劑進(jìn)入暴露的晶圓(4)剝離 SiO2如有侵權(quán),請(qǐng)聯(lián)系作者刪除`

2021-07-08 13:13:06

新加坡知名半導(dǎo)體晶圓代工廠招聘資深刻蝕工藝工程師和刻蝕設(shè)備主管!此職位為內(nèi)部推薦,深刻蝕工藝工程師需要有LAM 8寸機(jī)臺(tái)poly刻蝕經(jīng)驗(yàn)。刻蝕設(shè)備主管需要熟悉LAM8寸機(jī)臺(tái)。待遇優(yōu)厚。有興趣的朋友可以將簡(jiǎn)歷發(fā)到我的郵箱sternice81@gmail.com,我會(huì)轉(zhuǎn)發(fā)給HR。

2017-04-29 14:23:25

典型的硅刻蝕是用含氮的物質(zhì)與氫氟酸的混合水溶液。這一配比規(guī)則在控制刻蝕中成為一個(gè)重要的因素。在一些比率上,刻蝕硅會(huì)有放熱反應(yīng)。加熱反應(yīng)所產(chǎn)生的熱可加速刻蝕反應(yīng),接下來又產(chǎn)生更多的熱,這樣進(jìn)行下去會(huì)

2018-12-21 13:49:20

線路上的數(shù)據(jù)波都可以,但SRAM沒有響應(yīng)。MISO線ReMin在高電平。保持(引腳7)被綁定到3V,SiO2(引腳3)被連接到GND。我試圖替換MCU和SRAM,但問題仍然存在。這是我的簡(jiǎn)單代碼。我哪里錯(cuò)了?謝謝。

2019-08-08 11:07:25

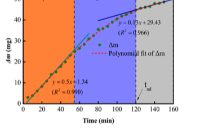

的偏壓使得正性的可移動(dòng)離子在poly/SiO2界面積累,造成閾值電壓正偏。為評(píng)估器件在使用過程中閾值電壓漂移情況,派恩杰半導(dǎo)體進(jìn)行了大量BTI實(shí)驗(yàn),基于實(shí)驗(yàn)數(shù)據(jù)建立了PBTI&NBTI

2022-03-29 10:58:06

“MOSFET”是英文MetalOxide Semicoductor Field Effect Transistor的縮寫,譯成中文是“金屬氧化物半導(dǎo)體場(chǎng)效應(yīng)管”。它是由金屬、氧化物(SiO2或

2021-04-23 07:04:52

的加工工藝流程,加工過程中需要運(yùn)用刻蝕機(jī)在晶圓上把復(fù)雜的3D圖形一層一層“堆疊”起來,實(shí)現(xiàn)單片機(jī)IC芯片的更小化。芯片,本質(zhì)上是一片載有集成電路(IC:Integrated circuit)的半導(dǎo)體元件

2018-08-23 17:34:34

臺(tái)面

刻蝕深度對(duì)埋柵SITH柵陰擊穿的影響針對(duì)臺(tái)面

刻蝕深度對(duì)埋柵型靜電感應(yīng)晶閘管(SITH)柵陰擊穿特性的影響做了實(shí)驗(yàn)研究。實(shí)驗(yàn)結(jié)果表明,隨著臺(tái)面

刻蝕深度的增大,器件柵陰擊穿由原來的軟擊穿變?yōu)橛矒舸?/div>

2009-10-06 09:30:24

IT驗(yàn)證工作得以實(shí)現(xiàn)的基礎(chǔ)。隨著電路的日益復(fù)雜化、高度集成化,可探測(cè)的節(jié)點(diǎn)越來越少,可訪問性越來越受到限制,后驅(qū)動(dòng)技術(shù)在故障注入中的應(yīng)用有效地解決了這個(gè)問題。然而后驅(qū)動(dòng)可能引發(fā)的退化加速越來越受到關(guān)心,對(duì)后全文下載

2010-04-22 11:29:19

。目前廣泛應(yīng)用的是SiO2為絕緣層的絕緣柵場(chǎng)效應(yīng)管,稱為金屬-氧化物-半導(dǎo)體場(chǎng)效應(yīng)管,簡(jiǎn)稱MOSFET。以功能類型劃分,MOSFET分為增強(qiáng)型和耗盡型兩種,其中耗盡型與增強(qiáng)型主要區(qū)別是在制造SiO2絕緣層

2019-07-29 06:01:16

介電常數(shù)膜如置于空氣中,在吸收了膜表面吸附的水分后,會(huì)有膜的介電常數(shù)比增大的問題。對(duì)此,在典型的有機(jī)系低介電常數(shù)材料MPS及PAE中,找出了吸水性非常低的材料。如把使用TEOS的等離子CVD的SiO2膜

2018-08-29 10:53:04

1. 為什么要pad oxidation??jī)H僅是為了抵消SIN和SI之間的應(yīng)力嗎?這里的所謂應(yīng)力指的是由于熱膨脹導(dǎo)致的SIN和SI之間的應(yīng)力嗎?(印象中兩者的的熱膨脹系數(shù)好象很接近的?難道SIO2的是介于兩者之間的?)

2011-12-02 14:32:59

表面產(chǎn)生龜裂,盡管可在包層中摻雜少量的B2O3 和 P2O5 來提高 SiO2 的熱膨脹系數(shù),同時(shí)降低 SiO2 的軟化溫度,但仍然難控制其中的殘余應(yīng)力。多次沉積、多次退火工藝難控制。采用 FHD 法

2018-02-22 10:06:53

上。 刻蝕只去除曝光圖形上的材料。 在芯片工藝中,圖形化和刻蝕過程會(huì)重復(fù)進(jìn)行多次。2017年3月11日,據(jù)CCTV2財(cái)經(jīng)頻道節(jié)目的報(bào)道,中微AMEC正在研制目前世界最先進(jìn)的5納米等離子刻蝕機(jī),將于2017年底將量產(chǎn)。轉(zhuǎn)自吳川斌的博客`

2017-10-09 19:41:52

刻蝕技術(shù),保留下柵隔離層上面的氮化硅層 12、濕法氧化,生長(zhǎng)未有氮化硅保護(hù)的 SiO2 層,形成 PN 之間的隔離區(qū) 13、熱磷酸去除氮化硅,然后用 HF 溶液去除柵隔離層位置的 SiO2 ,并重

2011-12-01 15:43:10

制備光路圖案。所得有機(jī)無機(jī)復(fù)合ZrO22SiO2 板型平面光波導(dǎo)(襯底層+ 導(dǎo)光層) ,用棱鏡耦合截?cái)喾y(cè)試其光損耗在632. 8 nm 波長(zhǎng)處約為0. 8 dB/ cm。對(duì)板型平面波導(dǎo)的導(dǎo)光層薄膜

2009-08-08 09:57:18

打開后,D到S才會(huì)有電流流過。但實(shí)際上由于自由電子的存在,自由電子的附著在SIO2和N+、導(dǎo)致D-S有漏電流。圖1.1.1 帶IGBT開關(guān)逆變中的漏電流2、 電源漏電流開關(guān)電源中...

2021-08-27 06:09:57

實(shí)驗(yàn)名稱:功率放大器在合成射流高效摻混機(jī)理研究中的應(yīng)用

實(shí)驗(yàn)內(nèi)容:合成射流是一種新型主動(dòng)流動(dòng)控制技術(shù),其主要工作原理是利用振動(dòng)薄膜或活塞周期性地吹/吸流體,在孔口外形成渦環(huán),這些渦環(huán)在自誘導(dǎo)

2024-03-08 17:47:25

使用過程中的耐擦洗性以及美觀度等,因此涂層的耐磨性是涂層的關(guān)鍵性能要求。考察n(SiO2)︰n(M+)︰n(PO43-)的不同比例對(duì)涂層耐摩擦次數(shù)的影響,以及在此基礎(chǔ)上添加0.5%質(zhì)量分?jǐn)?shù)的納米氧化鋯分散

2017-10-13 16:53:27

老化與熱老化;③電介質(zhì)內(nèi)部的電化學(xué)反應(yīng);④銀離子遷移;⑤電介質(zhì)在電容器制造過程中受到機(jī)械損傷;⑥電介質(zhì)分子結(jié)構(gòu)改變;⑦在高濕度或低氣壓環(huán)境中極間飛弧;⑧在機(jī)械應(yīng)力作用下電介質(zhì)瞬時(shí)短路。3.1.2引起電

2011-11-18 13:16:54

芯片制作工藝流程 工藝流程1) 表面清洗 晶圓表面附著一層大約2um的Al2O3和甘油混合液保護(hù)之,在制作前必須進(jìn)行化學(xué)刻蝕和表面清洗。2) 初次氧化 有熱氧化法生成SiO2 緩沖層,用來減小后續(xù)

2019-08-16 11:09:49

注入?yún)^(qū)表面形成薄薄的SiO2層,雜質(zhì)離子透過這層SiO2進(jìn)行注入。 硅和鍺半導(dǎo)體材料經(jīng)高度提純后,其原子排列已變成非常整齊的晶體狀態(tài),稱為單晶體也稱本征半導(dǎo)體。在本征半導(dǎo)體硅或鍺中摻入少量五價(jià)雜質(zhì)元素

2019-08-16 11:11:34

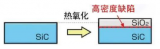

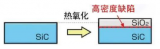

最近需要用到干法刻蝕技術(shù)去刻蝕碳化硅,采用的是ICP系列設(shè)備,刻蝕氣體使用的是SF6+O2,碳化硅上面沒有做任何掩膜,就是為了去除SiC表面損傷層達(dá)到表面改性的效果。但是實(shí)際刻蝕過程中總是會(huì)在碳化硅

2022-08-31 16:29:50

我在IND4汽車人App可以幫助大家解答汽車電子的相關(guān)技術(shù)問題,歡迎通過IND4汽車人App向我咨詢。在永磁同步電機(jī)中,轉(zhuǎn)子磁場(chǎng)中因?yàn)橛杏来挪牧蠘?gòu)成此磁體的南極和北極,轉(zhuǎn)子磁場(chǎng)的產(chǎn)生機(jī)理及在空間

2021-08-27 07:08:02

氫氟酸要好,容易清除。工藝步驟簡(jiǎn)單。困難在,擴(kuò)散均勻,印刷對(duì)齊。schmid 的腐蝕法SE 電池交鑰匙工程,centrotherm 的激光刻蝕氧化膜SE電池交鑰匙工程。 四、濕法腐蝕重?cái)U(kuò)散層

2018-09-26 09:44:54

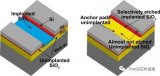

Microstructures在SEMICON China期間推出了干法刻蝕模塊與氧化物釋放技術(shù),該技術(shù)為MEMS器件設(shè)計(jì)師提供了更多的生產(chǎn)選擇,同時(shí)帶來了寬泛的制造工藝窗口,從而使良率得到了提升。麥|斯

2013-11-04 11:51:00

利用射頻共濺射方法制備了一系列不同金屬含量x的Fex(SiO2)(1−x)金屬−絕緣體顆粒膜,系統(tǒng)地研究了薄膜的霍爾效應(yīng)及其產(chǎn)生機(jī)理。在室溫和1.3 T的磁場(chǎng)下,當(dāng)體積分?jǐn)?shù)為0.52

2008-12-03 13:10:25 9

9 ,使用溫度在-200~+260℃;2、耐受強(qiáng)酸強(qiáng)堿等強(qiáng)腐蝕樣品,比如:王水、魔酸、liu酸等;3、低的溶出和析出,金屬元素空白值低,鉛含量小于0.01ppb;4、本產(chǎn)

2022-09-01 13:30:27

研究了SiC表面氫化降低界面態(tài)密度的機(jī)理。采用緩慢氧化、稀釋的HF刻蝕、沸水浸泡的表面氫化處理方法,降低SiC表面態(tài)密度。該方法用于SiC器件的表面處理,在100℃以下制備了理想

2009-05-07 20:31:44 35

35 分別以丙醇鋯和正硅酸乙酯為原料,采用溶膠-凝膠工藝制備了性能穩(wěn)定的ZrO2和SiO2溶膠。用旋轉(zhuǎn)鍍膜法在K9玻璃上分別制備了SiO2單層膜、ZrO2單層

2010-03-03 13:50:49 21

21 ITO玻璃技術(shù)之SiO2阻擋膜層規(guī)格

SiO2 阻擋膜層規(guī)格

2008-10-25 16:04:25 1408

1408 鍍復(fù)SiO2膜的電容器介質(zhì)膜

成功一種能在幾百小時(shí)連續(xù)沉積SiO2膜的新穎電子束蒸發(fā)裝置,獲國(guó)家發(fā)明專利,在此基礎(chǔ)上

2009-12-08 09:03:32 702

702 什么是Prescott/SiO2F?

這是Intel最新的CPU核心,目前還只有Pentium 4而沒有低端的賽揚(yáng)采用,其與Northwood最大的區(qū)別是采用了0.09um制造工藝

2010-02-04 11:28:54 394

394 干法刻蝕原理

刻蝕作用:去除邊緣PN結(jié),防止上下短路。干法刻蝕原理:利用高頻輝光放電反應(yīng),使CF4氣體激活成活性粒子,這些活性

2010-07-18 11:28:20 5637

5637 本文在淺溝槽隔離刻蝕過程中發(fā)現(xiàn),當(dāng)刻蝕腔室上石英窗口的溫度超過85℃時(shí),刻蝕終止出現(xiàn)在300mm晶圓的中心。我們認(rèn)為刻蝕終止的原因是由于某些低揮發(fā)SiOxCly刻蝕產(chǎn)物再淀積。石英

2012-05-04 17:09:37 2803

2803

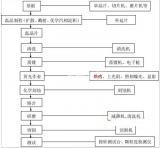

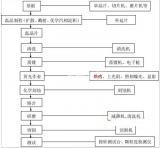

LED 芯片的制造工藝流程:外延片→清洗→鍍透明電極層→透明電極圖形光刻→腐蝕→去膠→平臺(tái)圖形光刻→干法刻蝕→去膠→退火→SiO2 沉積→窗口圖形光刻→SiO2 腐蝕→去膠→N極圖形光刻→預(yù)清洗→鍍膜→剝離→退火→P 極圖形光刻→鍍膜→剝離→研磨→切割→芯片→成品測(cè)試。

2016-08-05 17:45:21 17422

17422

理論及不同退火溫度、不同退火時(shí)間、SiO2薄膜厚度、SiO2薄膜折射率、不同蓋片等試驗(yàn)參數(shù)對(duì)制備非吸窗口的影響,并且討論了Si0,薄膜介質(zhì)膜的多孔性對(duì)無雜質(zhì)誘導(dǎo)量子阱混合的影響.實(shí)驗(yàn)制備出藍(lán)移波長(zhǎng)為53 nm的非吸收窗口,最佳制備非吸收窗口條件為退火溫度為

2018-02-10 10:16:35 0

0 鈍化層刻蝕對(duì)厚鋁鋁須缺陷影響的研究

2018-03-06 09:02:50 5607

5607 反刻是在想要把某一層膜的總的厚度減小時(shí)采用的(如當(dāng)平坦化硅片表面時(shí)需要減小形貌特征)。光刻膠是另一個(gè)剝離的例子。總的來說,有圖形刻蝕和無圖形刻蝕工藝條件能夠采用干法刻蝕或濕法腐蝕技術(shù)來實(shí)現(xiàn)。為了復(fù)制硅片表面材料上的掩膜圖形,刻蝕必須滿足一些特殊的要求。

2018-12-14 16:05:27 68523

68523 在等離子增強(qiáng)化學(xué)氣相沉積法PECVD沉積 SiO2和 SiN掩蔽層過程中!分解等離子體中濃度較高的H原子使MG受主鈍化!同時(shí)在P-GaN材料表面發(fā)生反應(yīng)形成淺施主特性的N空位。

2018-12-17 08:00:00 17

17 N溝道增強(qiáng)型MOS管在P型半導(dǎo)體上生成一層SiO2薄膜絕緣層,然后用光刻工藝擴(kuò)散兩個(gè)高摻雜的N型區(qū),從N型區(qū)引出電極(漏極D、源極S);在源極和漏極之間的SiO2絕緣層上鍍一層金屬鋁作為柵極G;P型半導(dǎo)體稱為襯底,用符號(hào)B表示。由于柵極與其它電極之間是相互絕緣的,所以NMOS又被稱為絕緣柵型場(chǎng)效應(yīng)管。

2019-03-10 10:44:22 23364

23364

外延片→清洗→鍍透明電極層→透明電極圖形光刻→腐蝕→去膠→平臺(tái)圖形光刻→干法刻蝕→去膠→退火→SiO2沉積→窗口圖形光刻→SiO2腐蝕→去膠→N極圖形光刻→預(yù)清洗→鍍膜→剝離→退火→P極圖形光刻→鍍膜→剝離→研磨→切割→芯片→成品測(cè)試。

2019-03-27 16:58:15 20979

20979 湖北興力電子材料有限公司年產(chǎn)3萬噸電子級(jí)氫氟酸項(xiàng)目開工儀式在興發(fā)集團(tuán)宜昌新材料產(chǎn)業(yè)園舉行。該項(xiàng)目建成后,將有效填補(bǔ)國(guó)內(nèi)市場(chǎng)高端電子級(jí)氫氟酸生產(chǎn)空白,實(shí)現(xiàn)高端電子級(jí)氫氟酸的國(guó)產(chǎn)化。

2019-05-17 18:13:56 6718

6718 突破!濱化集團(tuán)電子級(jí)氫氟酸成功打入韓國(guó)市場(chǎng)

2019-07-18 10:23:31 11155

11155 據(jù)最新消息,中國(guó)濱化集團(tuán)生產(chǎn)的氫氟酸已成功拿到部分韓國(guó)半導(dǎo)體廠商的批量訂單!

2019-07-18 14:56:17 2634

2634 SiO2 薄膜具有良好的硬度、光學(xué)、介電性質(zhì)及耐磨、抗蝕、機(jī)械等特性,在光學(xué)、微電子等領(lǐng)域有著廣泛的應(yīng)用前景

2020-03-10 08:00:00 23

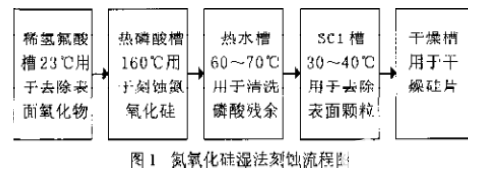

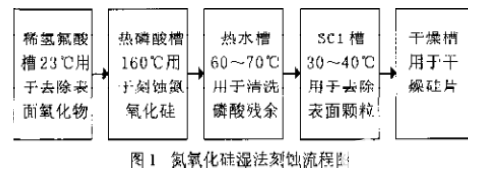

23 清洗不當(dāng)造成的表面缺陷的形成機(jī)理,并通過合理的實(shí)驗(yàn)設(shè)計(jì)和分析,給出了具體的解決方案。 熱磷酸濕法刻蝕已經(jīng)在半導(dǎo)體制造工藝中應(yīng)用了幾十年了。由于熱磷酸對(duì)氮化硅和氮氧化硅刻蝕具有良好的均勻性和較高的選擇比,一直到

2020-12-29 14:36:07 2510

2510

在集成電路的制造過程中,刻蝕就是利用化學(xué)或物理方法有選擇性地從硅片表面去除不需要的材料的過程。從工藝上區(qū)分,刻蝕可以分為濕法刻蝕和干法刻蝕。前者的主要特點(diǎn)是各向同性刻蝕;后者是利用等離子體來進(jìn)行

2020-12-29 14:42:58 8547

8547

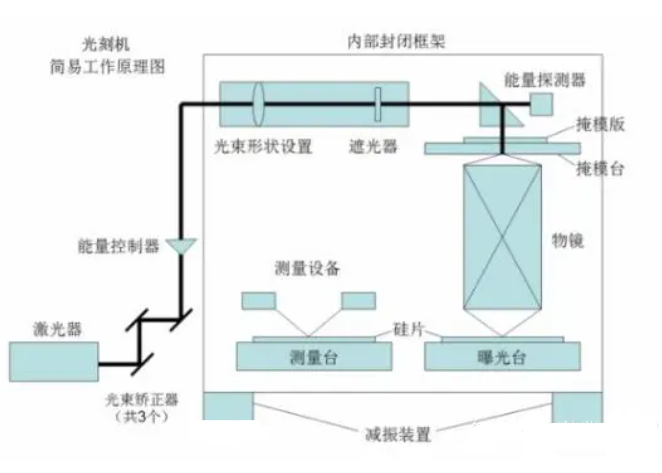

刻蝕機(jī)不能代替光刻機(jī)。光刻機(jī)的精度和難度的要求都比刻蝕機(jī)高出很多,在需要光刻機(jī)加工的時(shí)候刻蝕機(jī)有些不能辦到,并且刻蝕機(jī)的精度十分籠統(tǒng),而光刻機(jī)對(duì)精度的要求十分細(xì)致,所以刻蝕機(jī)不能代替光刻機(jī)。

2022-02-05 15:47:00 39913

39913 刻蝕速率是指在刻蝕過程中去除硅片表面材料的速度通常用?/min表示, 刻蝕窗口的深度稱為臺(tái)階高度。 為了高的產(chǎn)量, 希望有高的刻蝕速率。 在采用單片工藝的設(shè)備中, 這是一個(gè)很重要的參數(shù)。 刻蝕速率由工藝和設(shè)備變量決定, 如被刻蝕材料類型、 蝕機(jī)的結(jié)構(gòu)配置、 使用的刻蝕氣體和工藝參數(shù)設(shè)置。

2022-03-15 13:41:59 2907

2907

本文對(duì)晶片采用HF溶液洗凈的晶片氫氟酸處理后的護(hù)發(fā)素及干燥方法,使用異丙基去除上述晶片表面殘存的HF的步驟,關(guān)于晶片氫氟酸處理后的護(hù)發(fā)素和干燥方法,其特點(diǎn)是在對(duì)上述晶片施加82-84℃溫度的同時(shí)通過

2022-03-23 17:06:05 1599

1599

在微電子技術(shù)以及在微結(jié)構(gòu)、微光學(xué)和微化學(xué)傳感器中,需要在由不同材料構(gòu)成的大面積的薄膜層中構(gòu)造功能完善的結(jié)構(gòu)。

2022-03-29 15:49:58 3961

3961

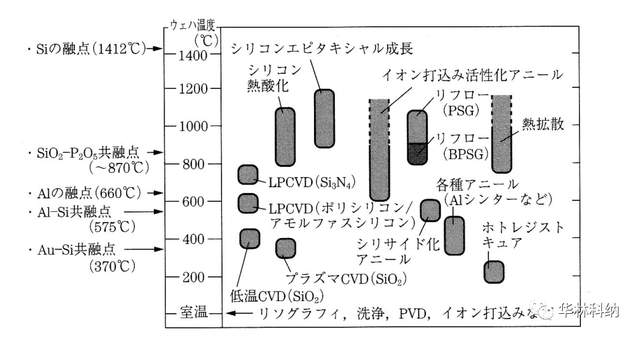

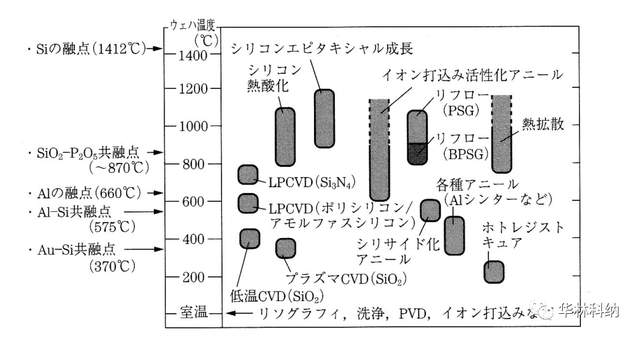

Si晶片在大氣中自然氧化,表面非常薄,但被SiO2膜復(fù)蓋。Si和在其上產(chǎn)生的SiO2膜的密合性很強(qiáng)。在高溫下進(jìn)行氧化,會(huì)產(chǎn)生厚而致密且穩(wěn)定的膜。Si的熔點(diǎn)為1412℃,但SiO2的熔點(diǎn)為1732

2022-04-13 15:26:08 4795

4795

刻蝕室半導(dǎo)體IC制造中的至關(guān)重要的一道工藝,一般有干法刻蝕和濕法刻蝕兩種,干法刻蝕和濕法刻蝕一個(gè)顯著的區(qū)別是各向異性,更適合用于對(duì)形貌要求較高的工藝步驟。

2022-06-13 14:43:31 6

6 濕法刻蝕也稱腐蝕。硅的濕法刻蝕是 MEMS 加工中常用的技術(shù)。其中,各向同性 (Isotropic)濕法刻蝕常用的腐蝕劑是由氫氟酸(HF)、硝酸( HNO3)和乙酸(CH3COOH)組成的混合物

2022-10-08 09:16:32 3581

3581 這款GO-FET生物傳感器采用由p型硅(Si)襯底以及覆蓋其上的二氧化硅(SiO2)介電層組成的p型硅片(Si/SiO2)制備。

2022-11-10 09:58:24 453

453 刻蝕是移除晶圓表面材料,達(dá)到IC設(shè)計(jì)要求的一種工藝過程。刻蝕有兩種:一種為圖形 化刻蝕,這種刻蝕能將指定區(qū)域的材料去除,如將光刻膠或光刻版上的圖形轉(zhuǎn)移到襯底薄膜 上

2023-02-01 09:09:35 1748

1748 刻蝕速率是測(cè)量刻蝕物質(zhì)被移除的速率。由于刻蝕速率直接影響刻蝕的產(chǎn)量,因此刻蝕速率是一個(gè)重要參數(shù)。

2023-02-06 15:06:26 3998

3998 刻蝕有三種:純化學(xué)刻蝕、純物理刻蝕,以及介于兩者之間的反應(yīng)式離子刻蝕(ReactiveIonEtch,RIE)。

2023-02-20 09:45:07 2586

2586 對(duì)于濕法刻蝕,大部分刻蝕的終點(diǎn)都取決于時(shí)間,而時(shí)間又取決于預(yù)先設(shè)定的刻蝕速率和所需的刻蝕厚度。由于缺少自動(dòng)監(jiān)測(cè)終點(diǎn)的方法,所以通常由操作員目測(cè)終點(diǎn)。濕法刻蝕速率很容易受刻蝕劑溫度與濃度的影響,這種影響對(duì)不同工作站和不同批量均有差異,因此單獨(dú)用時(shí)間決定刻蝕終點(diǎn)很困難,一般釆用操作員目測(cè)的方式。

2023-03-06 13:56:03 1773

1773 硅的堿性刻蝕液:氫氧化鉀、氫氧化氨或四甲基羥胺(TMAH)溶液,晶片加工中,會(huì)用到強(qiáng)堿作表面腐蝕或減薄,器件生產(chǎn)中,則傾向于弱堿,如SC1清洗晶片或多晶硅表面顆粒,一部分機(jī)理是SC1中的NH4OH

2023-06-05 15:10:01 1598

1598 目前,許多企業(yè)在SiC MOSFET的批量化制造生產(chǎn)方面遇到了難題,其中如何降低SiC/SiO?界面缺陷是最令人頭疼的問題。

2023-06-13 16:48:17 376

376

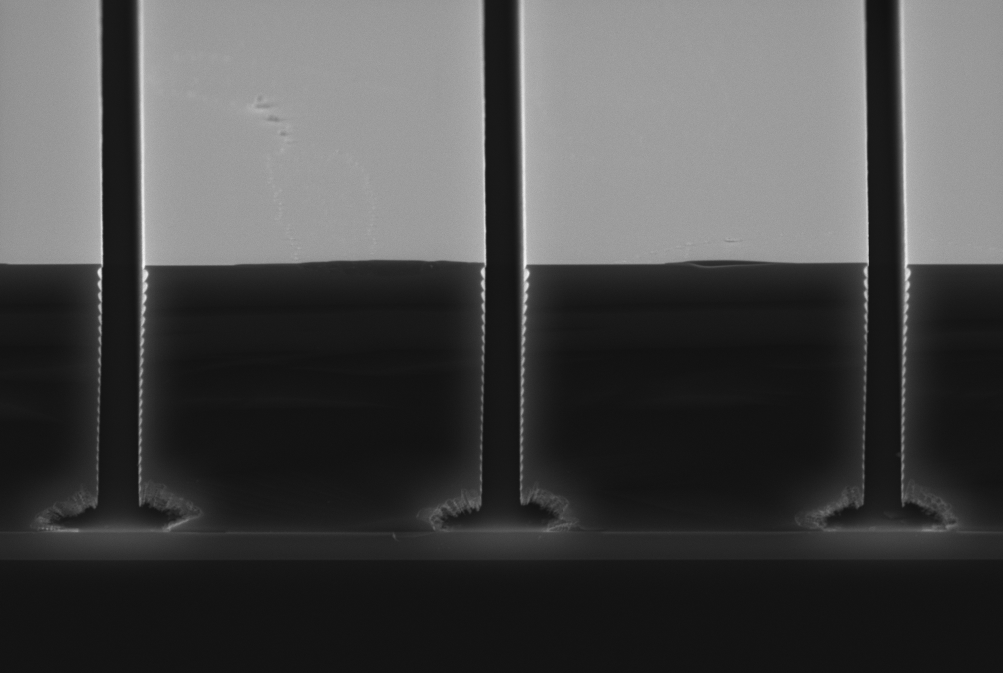

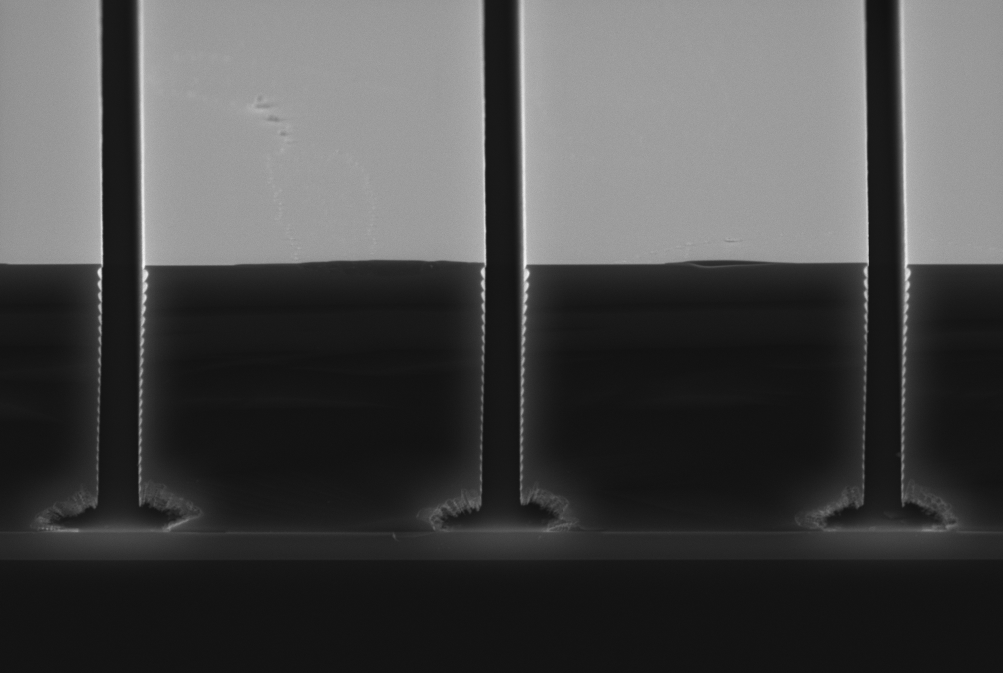

第一種是間歇式刻蝕方法(BOSCH),即多次交替循環(huán)刻蝕和淀積工藝,刻蝕工藝使用的是SF6氣體,淀積工藝使用的是C4F8氣體

2023-07-14 09:54:46 3214

3214

刻蝕(Etching)的目的是在材料表面上刻出所需的圖案和結(jié)構(gòu)。刻蝕的原理是利用化學(xué)反應(yīng)或物理過程,通過移除材料表面的原子或分子,使材料發(fā)生形貌變化。

2023-08-01 16:33:38 3915

3915 硅在暴露在空氣中時(shí)會(huì)形成一層氧化硅(SiO2)層。在許多制程步驟中,如在熱處理過程之前,需要移除這層氧化硅。氫氟酸是唯一能夠有效清洗硅片表面氧化硅的化學(xué)品。氫氟酸能夠與SiO2發(fā)生反應(yīng),生成揮發(fā)性的氟硅酸,從而清除硅片表面的氧化物層。

2023-08-02 10:40:25 543

543

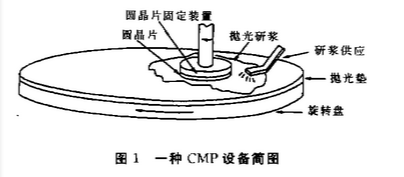

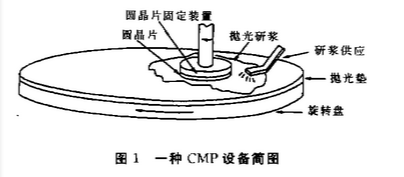

20世紀(jì)60年代以前,半導(dǎo)體基片拋光還大都沿用機(jī)械拋光,得到的鏡面表面損傷是極其嚴(yán)重的。1965年Walsh和Herzog提出SiO2溶膠和凝膠拋光后,以SiO2漿料為代表的化學(xué)機(jī)械拋光工藝就逐漸代替了以上舊方法。

2023-08-02 10:48:40 7529

7529

在半導(dǎo)體制造中,刻蝕工序是必不可少的環(huán)節(jié)。而刻蝕又可以分為干法刻蝕與濕法刻蝕,這兩種技術(shù)各有優(yōu)勢(shì),也各有一定的局限性,理解它們之間的差異是至關(guān)重要的。

2023-09-26 18:21:00 3307

3307

刻蝕(或蝕刻)是從晶圓表面去除特定區(qū)域的材料以形成相應(yīng)微結(jié)構(gòu)。但是,在目標(biāo)材料被刻蝕時(shí),通常伴隨著其他層或掩膜的刻蝕。

2023-10-07 14:19:25 2073

2073

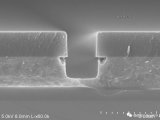

但是,在刻蝕SOI襯底時(shí),通常會(huì)發(fā)生一種凹槽效應(yīng),導(dǎo)致刻蝕的形貌與預(yù)想的有很大出入。那么什么是凹槽效應(yīng)?什么原因引起的?怎么抑制這種異常效應(yīng)呢?

2023-10-20 11:04:21 461

461

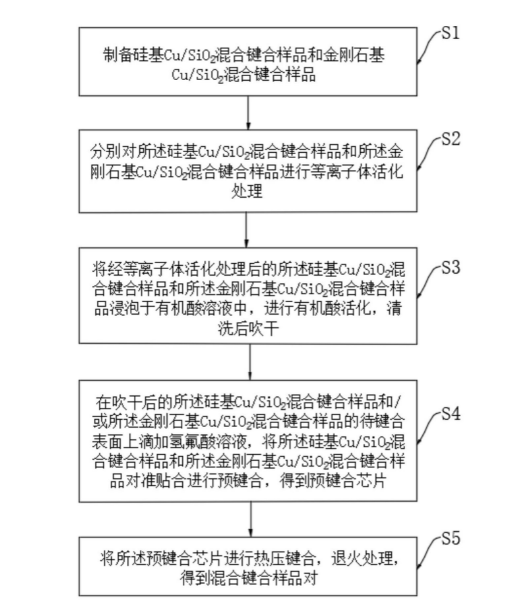

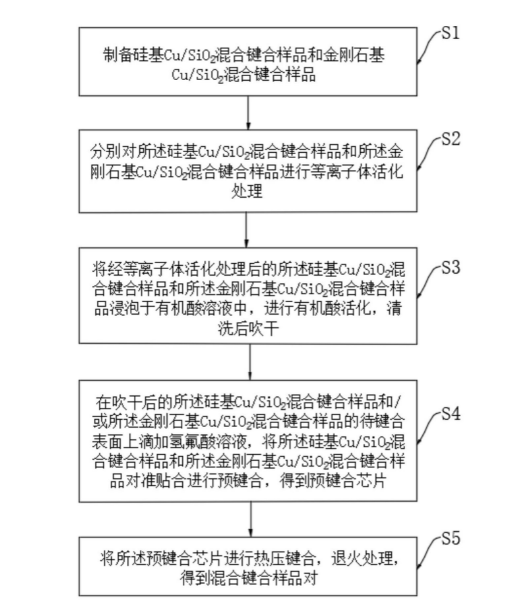

摘要本發(fā)明涉及芯片制造技術(shù)領(lǐng)域。硅基的cu/sio2混合結(jié)合樣品和金剛石基礎(chǔ)的cu/sio2混合結(jié)合樣品的準(zhǔn)備后,進(jìn)行等離子體活性。經(jīng)等離子體活性處理后,將cu/sio2混合結(jié)合試料浸泡在有機(jī)酸溶液中清洗后干燥。

2023-11-22 09:25:59 285

285

某種電介質(zhì)的介電常數(shù)ε與真空介電常數(shù)ε0的比值,稱為該電介質(zhì)的相對(duì)介電常數(shù),符號(hào)為εr,即εr=ε/ε0,εr是無量綱的純數(shù),其中真空介電常數(shù)ε0=8.854E-12F/m,SIO2的相對(duì)介電常數(shù)為εr=3.9,所以SIO2的介電常數(shù)ε=εr*ε0=3.9×8.854E-12F/m

2023-11-30 15:39:12 674

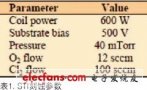

674 影響深硅刻蝕的關(guān)鍵參數(shù)有:氣體流量、上電極功率、下電極功率、腔體壓力和冷卻器。

2024-02-25 10:44:39 283

283

刻蝕機(jī)的刻蝕過程和傳統(tǒng)的雕刻類似,先用光刻技術(shù)將圖形形狀和尺寸制成掩膜,再將掩膜與待加工物料模組裝好,將樣品置于刻蝕室內(nèi),通過化學(xué)腐蝕或物理磨蝕等方式將待加工物料表面的非掩膜區(qū)域刻蝕掉,以得到所需的凹槽和溝槽。

2024-03-11 15:38:24 471

471

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論