緒論

經過了前面的文檔、編碼、驗證階段,我們手頭已經有了沒有錯誤的RTL代碼。這一章我們把這些RTL代碼轉化成后端的輸入:網表(Netlist,綜合工具自動將RTL翻譯成與或非門,用于實現)。這個步驟主要是有工具來完成的,我們知道流程就行。

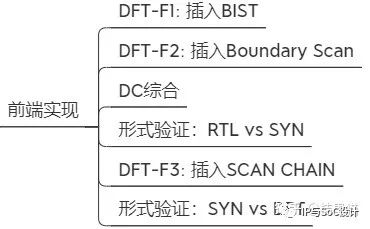

說是實現,其實包含了DFT (Design For Test)三板斧的插入、DC綜合以及形式驗證。算是芯片設計里承上啟下的一個流程。我此處把它歸到前端里了,也有歸到后端的,或者單拎出來讓DFT工程師專門做的。插句額外的話,此處只是簡單列了DFT的基本原理,實際上DFT也和驗證一樣是個有自己神奇而獨特技術棧的活,有專門的工程師工種叫DFT工程師。

一 DFT-F1: 插入BIST

BIST(Build-in-self test)是內建自測試的意思。又分為MBIST和LBIST。

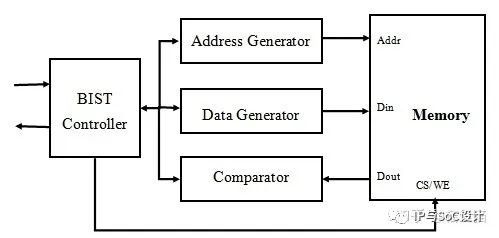

MBIST (Memory build-in-self test), 指的是存儲內建自測試。這個原理上講起來比較容易,就是在SRAM周邊加上一些測試邏輯。Memory通常來講在芯片中占據的面積比較大,也容易出錯,所以加上專門的測試邏輯。這個地方需要區分MBIST和ATE (Auto-Test-Equipment, 我們后面講芯片封裝測試的時候講)的區別,ATE的激勵是外部給的,MBIST激勵是自己生成的。而且MBIST可以每次芯片上電都測試一遍,防止芯片出錯。

這個東西的工作原理如上圖,在Memory周圍加上激勵,至于怎么加激勵有人專門研究這個(MBIST Algorithm),感興趣的可以學習一下。此外,還有一種Memory Built-in Self Repair (BISR)的辦法,MBIST檢測到Memory有問題后將有問題的cell映射到冗余的好的cell上去。

LBIST (Logic build-in-self test), 邏輯內建自測試。和MBIST同理,在關鍵邏輯上加上自測試電路,看看邏輯cell有沒有工作正常。BIST總歸會在芯片里加入自測試邏輯,都是成本。個人理解如果不要求穩定性非常好的芯片,LBIST可以不要。但是一些芯片,比如自動駕駛可能LBIST還是需要的。

一般來講BIST用工具直接插到RTL代碼里去,其實算是正常的交付功能。

二 DFT-F2: 插入Boundary Scan

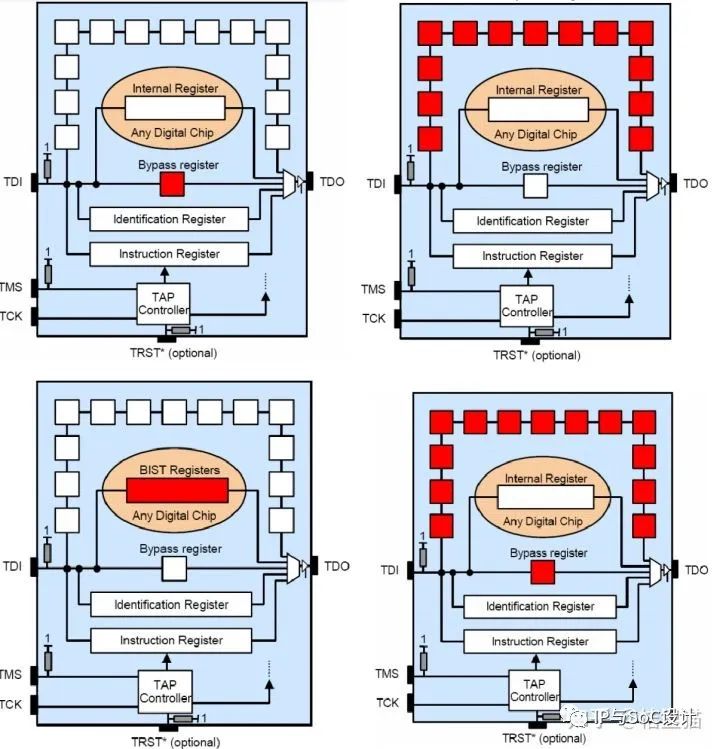

這個boundary scan主要用來對芯片的輸入輸出(也可以是關鍵邏輯塊,比如RISC-V核心)檢測和測試,其實就是我們常聽過的JTAG接口(JTAG有個很奇葩的名字,Joint Test Action Group, 聯合測試工作組 Orz)。

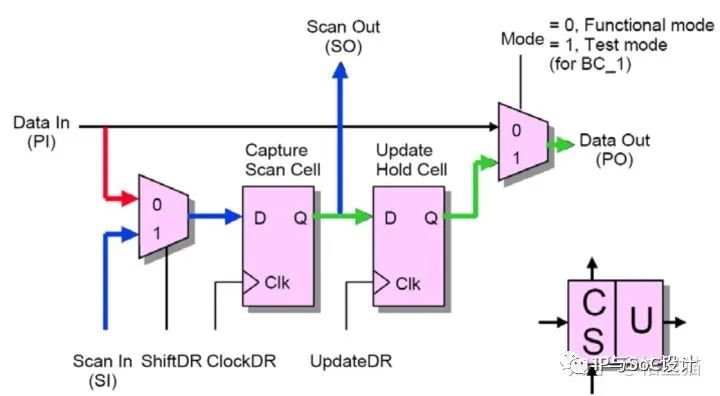

基本原理也簡單,像上面這張圖一樣,把芯片的IO用寄存器鏈穿起來。JTAG端口雖然只有4個信號,但是能實現的測試功能非常多,可不是簡單把IO串行拿出來看看這么簡單。

上面一個小方塊scan cell包含了下面內容。

里面包含了幾個capture cell寄存器,用來把IO上的值給采下來。還有一個update hold cell, 可以把想要的值傳給IO。

用法1:左上,直接bypass, 可以方便的把不同的JTAG CHAIN給穿起來。

用法2:右上,把IO穿起來,可以看IO的值,也可以外部給所有IO輸入值

用法3:左下,可以當做串口,給上面講的BIST輸入控制信號

用法4:右下,Clamp模式,bypass和chain同時開了, 可以給IO置為,但是值從bypass輸出。

JTAG也是直接加到RTL代碼,當做一個功能來用。

三 DC綜合

經過了DFT的兩把斧,我們接下來要跑綜合。綜合的主要目的是把Verilog代碼轉換成門級網表。

DC是design compiler的意思,Synopsys的軟件,當然也可以用其他廠商的RTL Compiler,不過我沒用過不熟悉。DC內部主要實現了3個步驟:

·Translation, 單純的把RTL轉化成DC內部的數據庫,這個庫和工藝無關,就是標準的與或非等等。

·Optimization, 這個階段根據工作頻率、面積、功耗來優化電路,然后生成滿足設計標準的門級網表。

·Mapping, 這個步驟與工藝相關,將門級網表映射到代工廠給的門級網表上。

這個過程其實大部分都是工具來完成的,我們只用設置一些配置。

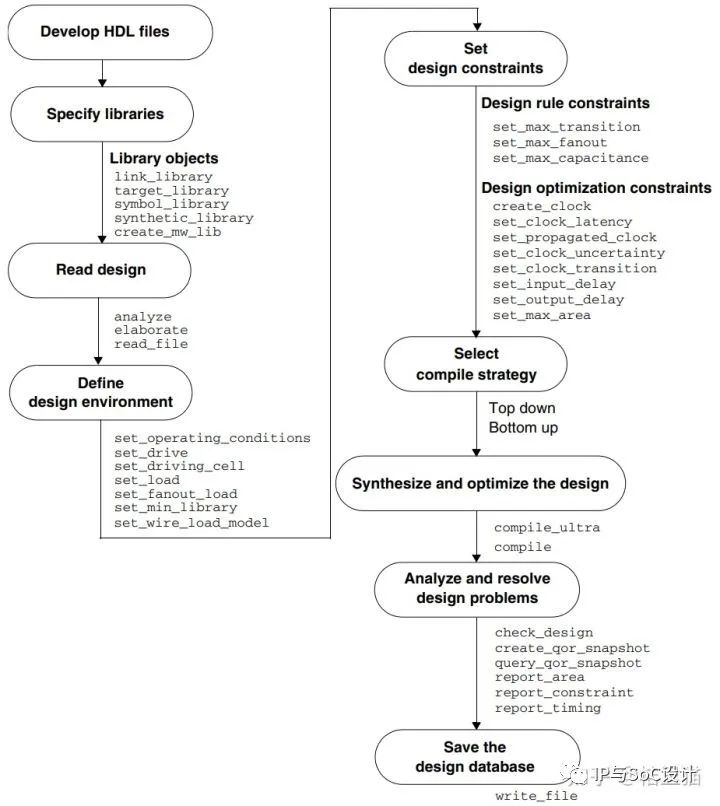

一共九個步驟。

step0 Develop HDL files. 這個步驟就是前面介紹了一大堆設計的Verilog文件

step1 Specify libraries. 這個步驟主要是指定一下需要的庫文件。幾個庫文件都是干嘛的我們簡單講講。link library指的鏈接的庫,比如RAM, ROM core的庫,一般放在link library. target library是代工廠給得工藝庫,最后會把網表映射到這個庫的單元上。symbol library可以不用,GUI用到的,synopsys library. synopsys的標準lib. 中間過程要用到。

step2 Read Design. 比較簡單,把你的設計讀到DC里面去。

step3&4 Design Constraint. 這兩個步驟其實可以一起講。給綜合設置一些約束,比如時鐘頻率,允許的時鐘不確定性等等。

step5 Compiler Strategy. 這個步驟主要是選綜合策略。綜合策略一般有兩種,top-down, bottom up。top-down用來綜合小模塊,設計約束在頂層,當做一個整體一把綜合了。bottom up一般用來綜合大型的設計。先約束并綜合底層,然后設置一個dont touch, 一層一層向上綜合。

step6 Synthesis. 綜合優化,主要占用時間的就是這一步驟。一般會在機器上跑幾個小時到幾天甚至幾周時間。

step7 Report design. 這個步驟主要是報出綜合的面積,時序,看看面積有沒有超標,時序有沒有違例,如果時序或者面積有問題,返回step0修改設計,重新來綜合。

基本上的綜合流程就這些。

四 形式驗證:RTL vs SYN Netlist

做完了綜合,我們還有做個步驟,到底綜合對了沒,等不等價,需要驗證一下。這種驗證叫形式驗證 Formal Verification。有個工具叫formality的可以干這個活。簡單理解這個步驟就是做等價性驗證的。這個步驟比綜合會快很多。這也可以理解,一個是從無到有的生成,另一個只是對比一下功能是不是等價的。原理大概是在RTL代碼和netlist中抽取一些點(一般是寄存器的輸入或者輸出),驗證組合邏輯的等價性。

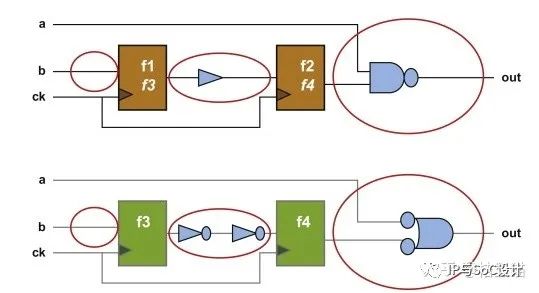

如上面兩個設計,使用的單元是不一樣的,但其實功能是等價的。formality只能保證功能是等價的,但是保證不了STA不出問題。所以只能說STA沒問題的情況下,formality能保證SYN功能正確。

五 DFT-F3:SCAN CHAIN

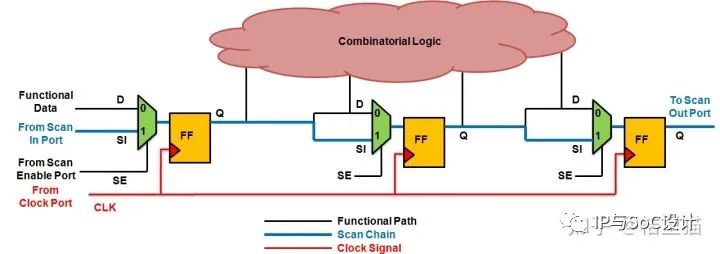

emmm 形式驗證完后,還有一個DFT步驟。DFT的第三把斧: 加入scan chain. 這個步驟一般不加在RTL而是直接加在DFT網表。原理也很簡單,把設計中的所有寄存器連接成一條或者幾條鏈。

向上面這樣。正常的功能數據走functional path, 在測試模式下所有FF都是移位寄存器,可以把值讀出來看看。

當然,也可以把值插進去,看看某段組合邏輯有沒有問題。

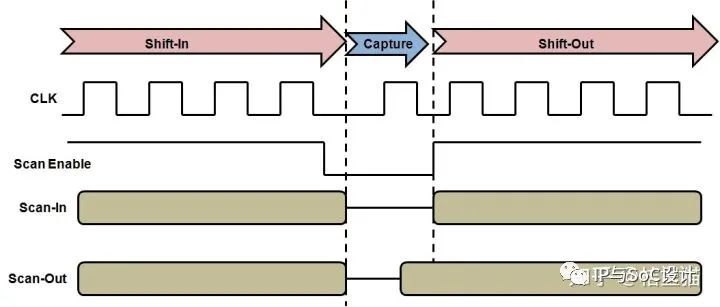

比如這樣,先拉高scan enable, 用若干拍把數據load到寄存器里,然后拉低scan一拍,讓組合邏輯算出結果,然后繼續拉高scan enable, 把計算結果shfit out出來。

其實這里有個搞笑的事兒,研究生第一次流片的時候看到DFT scan chain,覺得這個東西賊有用,畢竟沒有專業測試,一旦邏輯什么寫錯了,我豈不是可以自己寫一段數據,直接shift到芯片里,看看哪里有了BUG,針對性的解決。那一瞬間,感覺自己像個小天才Orz...

后來知道一般設計中寄存器何止成千上萬,即使拆成多條鏈,每條也很長。指望手動造一個scan數據來debug是不現實的。一般都是自動生成若干組pattern, 自動測試,如果輸出和預期不一致,丫直接當做廢片處理了Orz。所以不量產的芯片不用加DFT,加了也沒啥實質性的用處。

DFT三板斧就講完了。

六 形式驗證:DFT vs SYN

最后再來一次形式驗證。對比一下加入DFT的網表和綜合出來的網表是不是功能一致的。原理和上面一樣,無須贅述。

七 總結

經過這篇文章,我們終于得到了芯片設計的網表。行文至此,我們前端設計的所有流程就都講完了。

編輯:黃飛

?

電子發燒友App

電子發燒友App

評論