本文研究主要考慮基于CuSn金屬互化物的微凸點(μbump)作為芯片堆疊的手段。系統(tǒng)研究了形成金屬互化物凸點連接的兩種方法。

2012-03-08 16:29:24 5495

5495

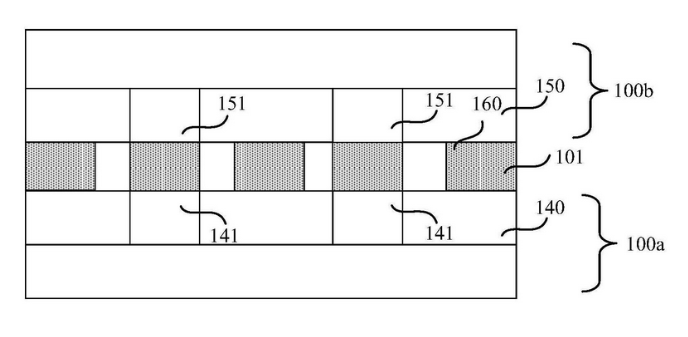

電子發(fā)燒友網(wǎng)報道(文/黃山明)近日,華為密集公布了多項技術(shù)專利,其中引人注意的是華為再次公布了兩項與芯片堆疊有關(guān)的專利。為何說再次,因為就在一個月前,華為同樣公開了“一種芯片堆疊封裝及終端設(shè)備

2022-05-09 08:09:00 24420

24420 元器件PIP(堆疊封裝)和PoP(堆疊組裝)的比較

1. PiP (Package In Package,堆疊封裝)

PiP一般稱堆疊封

2009-11-20 15:47:28 6429

6429 、行業(yè)交流和采購洽談于一體的綜合商貿(mào)平臺。本屆活動將分為中國(上海)國際顯示技術(shù)及應(yīng)用創(chuàng)新展(簡稱“DIC EXPO”)、中國(上海)國際顯示產(chǎn)業(yè)高峰論壇(簡稱“DIC Forum”)和國際顯示技術(shù)創(chuàng)新大獎 (簡稱“DIC AWARD”)三大版塊。通過三位一體的協(xié)同運營,DIC將實現(xiàn)以展共見行業(yè)

2022-07-11 09:40:03 2844

2844

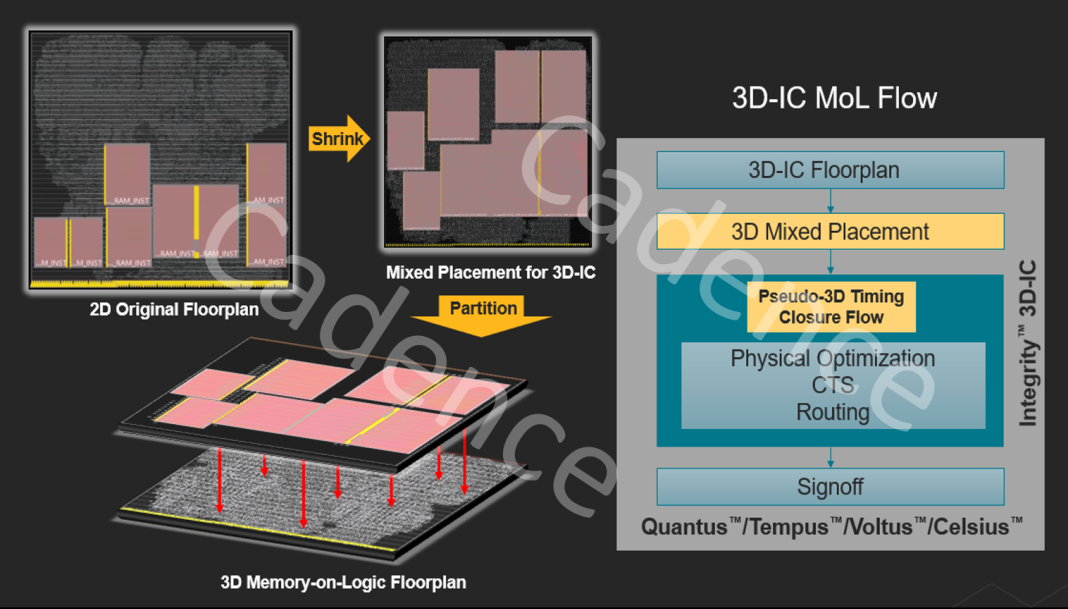

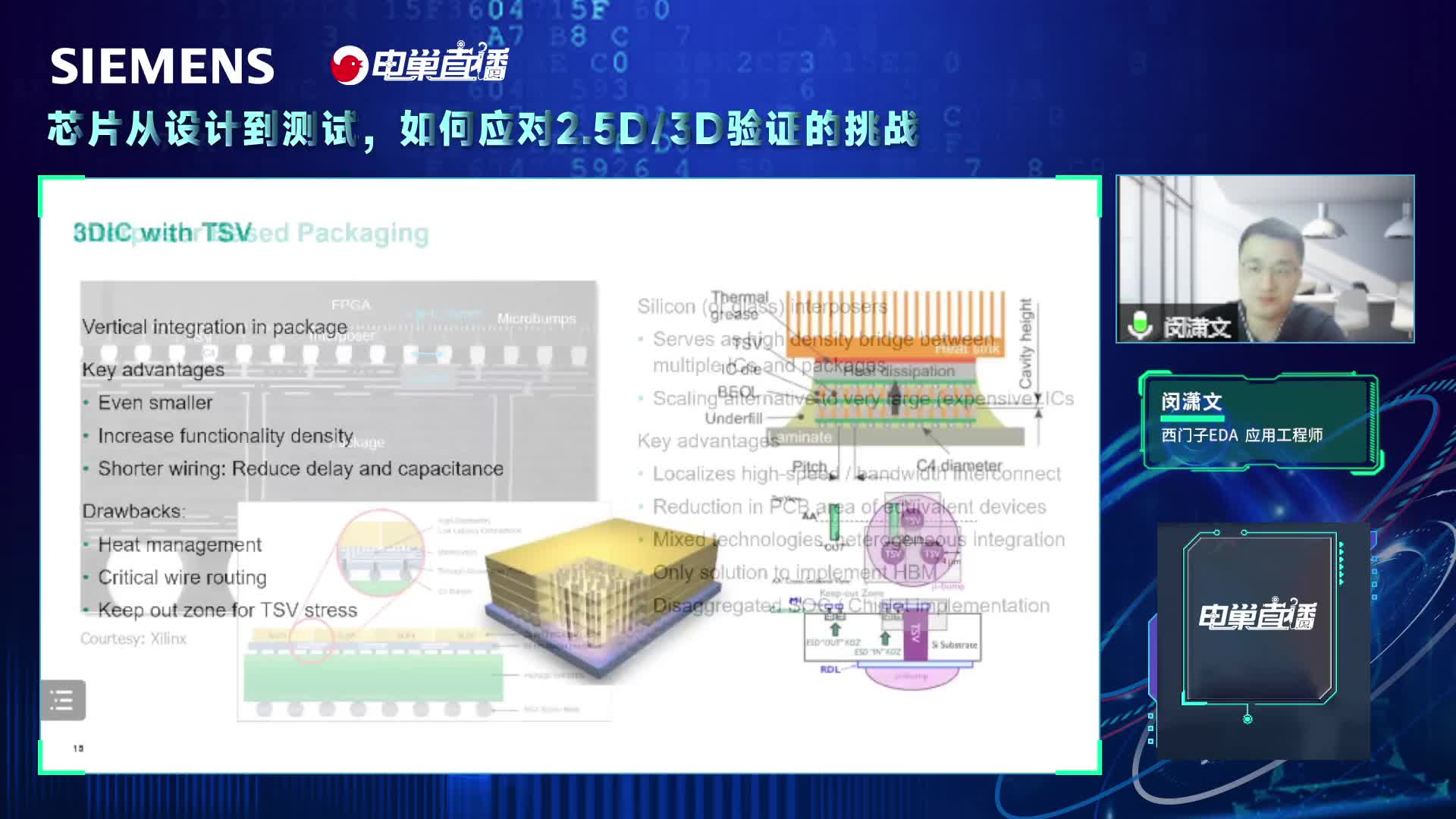

、性能更高,也因此成了新的設(shè)計主流,席卷了AI、服務(wù)器與汽車芯片等市場。但新的設(shè)計方案除了需要新一代的die-to-die的接口IP、2.5D/3D的封裝技術(shù)外,也需要在EDA工具與工作流上做出創(chuàng)新。 ? 西門子3D IC設(shè)計流工具 ? 為了解決3DIC集成在設(shè)計工具上

2023-11-09 00:22:00 1275

1275 DIC 2021第四屆上海國際顯示技術(shù)及應(yīng)用創(chuàng)新展覽會DISPLAY INNOVATION CONVENTION & EXPO展會主題:新型顯示 觸手可及時間:2021年6月30-7月2日

2020-09-15 16:19:16

芯片堆疊技術(shù)在SiP中應(yīng)用的非常普遍,通過芯片堆疊可以有效降低SiP基板的面積,縮小封裝體積。 芯片堆疊的主要形式有四種: 金字塔型堆疊 懸臂型堆疊 并排型堆疊 硅通孔TSV型堆疊

2020-11-27 16:39:05

,使用斜杠分隔方式,比如這里小編輸入了+2/-0.9。選中文字之后,我們點擊工具欄中的“堆疊”選項。(2)執(zhí)行結(jié)果如下圖所示: 3、對角線堆疊樣式: (1)輸入自己所要進行堆疊操作的文字,使用“#”分隔方式

2020-04-21 15:21:11

和3DIC技術(shù)的發(fā)展,F(xiàn)PGA不斷在加速取代ASSP和ASIC,但這還需要更多的突破,其中最大的障礙就是互聯(lián)問題,需在縱向架構(gòu)上“守正出奇”。

2019-09-23 07:50:27

大家好。對于我們的大學(xué)實驗室,我為Nexys和Atlys板創(chuàng)建了運營商,可以簡化在實驗室環(huán)境中的處理。雖然這些仍然可以改進,但實現(xiàn)了一些主要目標(biāo)。 - 易于存儲,可堆疊設(shè)計 - 學(xué)生可以看到電路板

2019-09-26 08:25:42

labview中能實現(xiàn)將一個個圓堆疊成圓柱嗎? 類似下圖

2022-05-03 15:05:25

與堆疊儀器集成系統(tǒng)相比,PXI和VXI具有哪些優(yōu)點和缺點?如何實現(xiàn)基于LAN的混合型系統(tǒng)的設(shè)計? 如何利用PC標(biāo)準(zhǔn)I/O簡化系統(tǒng)通信和連通能力?

2021-04-13 06:08:55

1、什么是堆疊設(shè)計也稱作系統(tǒng)設(shè)計,根據(jù)產(chǎn)品規(guī)劃,產(chǎn)品定義的要求,為實現(xiàn)一定的功能,設(shè)計出合理可靠的具備可量產(chǎn)性的PCB及其周邊元器件擺放的一種方案。2、堆疊工程師一般由結(jié)構(gòu)工程師進行堆疊,有些公司

2021-11-12 08:17:17

元器件內(nèi)芯片的堆疊大部分是采用金線鍵合的方式(Wire Bonding),堆疊層數(shù)可以從2~8層)。 STMICRO聲稱,誨今厚度到40μm的芯片可以從2個堆疊到8個(SRAM,Hash

2018-09-07 15:28:20

串聯(lián)堆疊,可創(chuàng)建一個溝道長度為3μm的有效器件(圖1)。 圖1:將三個MOSFET串聯(lián)堆疊,可提供3μm的溝道長度。 堆疊MOSFET在現(xiàn)代模擬設(shè)計中非常常見,但并不是沒有問題。其主要問題是電容

2021-10-12 16:11:28

沒有讀者認識到發(fā)生在3DIC集成中的技術(shù)進步,他們認為該技術(shù)只是疊層和引線鍵合,是一種后端封裝技術(shù)。而我們該如何去拯救3DIC集成技術(shù)?

2021-04-07 06:23:51

有兩個主要組成部分 - 一個是為整個3DIC設(shè)備構(gòu)建一個精確的電源模型,可以在詳細的瞬態(tài)和AC Spice分析中使用,另一個是確保模型有效地反映了非常寬的響應(yīng)范圍,包括從板級/封裝級的MHz到芯片

2017-09-25 10:14:10

各位高手。我想用labview實現(xiàn)多個2維數(shù)組的堆疊顯示,比如將10個二維數(shù)組堆疊顯示在三位空間里,且依然保留每一層的強度信息,效果類似圖:

2016-10-01 14:29:49

`華爾街日報發(fā)布文章稱,科技產(chǎn)品下一個重大突破將在芯片堆疊領(lǐng)域出現(xiàn)。Apple Watch采用了先進的的3D芯片堆疊封裝技術(shù)作為幾乎所有日常電子產(chǎn)品最基礎(chǔ)的一個組件,微芯片正出現(xiàn)一種很有意思的現(xiàn)象

2017-11-23 08:51:12

Viterbi Compiler MegaCore Function User Guide

好東西哦。網(wǎng)上搜集,希望對你有用。

2006-03-25 15:40:49 32

32 Reed-Solomon Compiler

2006-03-25 15:42:49 26

26 Altera viterbi compiler

2006-03-25 15:45:58 18

18 Altera viterbi compiler v1.0 下載

2009-03-23 09:45:42 0

0 MATLAB Compiler The Language of Technical Computing:This chapter describes the MATLAB Compiler

2010-02-10 11:19:36 0

0 交換機堆疊

交換機堆疊是通過廠家提供的一條專用連接電纜,從一臺交換機的"UP"堆疊端口直接連接到另一臺交換機的"DOWN"堆疊端口。以實現(xiàn)單臺交換機

2010-01-08 11:28:05 880

880 集線器的堆疊

部分集線器具有堆疊功能。集線器堆疊是通過廠家提供的一條專用連接電纜,從一臺集線器的"UP"堆疊端口直接連接到另一臺集線器的"DOWN"堆疊端口

2010-01-08 10:15:16 1443

1443 當(dāng)大部份芯片廠商都感覺到遵循摩爾定律之途愈來愈難以為繼時,3DIC成為了該產(chǎn)業(yè)尋求持續(xù)發(fā)展的出路之一。然而,整個半導(dǎo)體產(chǎn)業(yè)目前也仍在為這種必須跨越工具、制程、設(shè)計端并加

2011-06-22 08:51:53 261

261 當(dāng)大部份芯片廠商都感覺到遵循摩爾定律之途愈來愈難以為繼時,3DIC成為了該產(chǎn)業(yè)尋求持續(xù)發(fā)展的出路之一。然而,整個半導(dǎo)體產(chǎn)業(yè)目前也仍在為這種必須跨越工具、制程、設(shè)計端并加

2011-06-24 09:12:47 985

985 據(jù)臺灣對外貿(mào)易發(fā)展協(xié)會(TAITRA)透露,芯片代工巨頭臺積電(TSMC)有望超過intel,在2011年底推出業(yè)內(nèi)首款采用3-D芯片堆疊技術(shù)的半導(dǎo)體芯片產(chǎn)品。

2011-07-07 09:19:07 858

858 芯片堆疊封裝是提高存儲卡類產(chǎn)品存儲容量的主流技術(shù)之一,采用不同的芯片堆疊方案,可能會產(chǎn)生不同的堆疊效果。針對三種芯片堆疊的初始設(shè)計方案進行了分析,指出了堆疊方案失

2012-01-09 16:14:14 42

42 Altera公司藉助TSMC的CoWoS整合生產(chǎn)及封裝技術(shù)開發(fā)下一世代3DIC芯片

2012-03-23 08:31:27 991

991 2012年4月27日訊 - GLOBALFOUNDRIES今天宣布,在為新一代移動和消費電子應(yīng)用實現(xiàn)3D芯片堆疊的道路上,公司達到了一個重要的里程碑。在其位于美國紐約薩拉托加郡的Fab 8,GLOBALFOUNDRIES已開始

2012-04-28 09:15:03 1294

1294 因應(yīng)臺積電明年積極布建?? 20nm制程產(chǎn)能并跨及3DIC封測,國內(nèi)封測雙雄日月光、矽品及記憶體封測龍頭力成,下半年起也積極搶進3DIC封測,布建3DIC封測產(chǎn)能。

2012-07-30 09:08:04 1020

1020 TCL圖紙PDP42U3A_DIC

2017-02-28 22:21:46 2

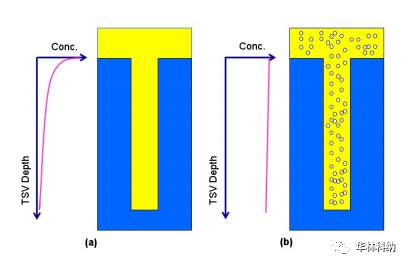

2 在不同的芯片或技術(shù)組合中,TSV技術(shù)還能提供更高水平的靈活度,例如采用45奈米制程的數(shù)字芯片中的芯片至芯片堆棧,以及在模擬晶圓(例如180nm)中,微機電(MEMS)組件或光傳感器和光電二極管數(shù)組的堆棧,這只是其中的幾個例子。

2017-04-26 11:34:40 3981

3981 CodeVision C Compiler 參考中文版

2017-09-21 09:26:29 0

0 來縮減晶方尺寸,同時也能使用先進的封裝技術(shù)來實現(xiàn)系統(tǒng)小型化。 3DIC成為縮小傳感器IC新解方 對于更高系統(tǒng)整合度的需求持續(xù)增加,這不只促使傳統(tǒng)的組裝服務(wù)供貨商,也推動半導(dǎo)體公司開發(fā)更創(chuàng)新和更先進的封裝技術(shù)。 最具前景且

2017-11-22 11:26:42 3

3 被稱之為“堆疊硅片互聯(lián)技術(shù)”的3D封裝方法采用無源芯片中介層、微凸塊和硅通孔 (TSV)技術(shù),實現(xiàn)了多芯片可編程平臺。

2019-01-03 13:20:59 3225

3225 在近日舉行的英特爾“架構(gòu)日”活動中,英特爾不僅展示了基于10納米的PC、數(shù)據(jù)中心和網(wǎng)絡(luò)系統(tǒng),支持人工智能和加密加速功能的下一代“Sunny Cove”架構(gòu),還推出了業(yè)界首創(chuàng)的3D邏輯芯片封裝技術(shù)——Foveros。這一全新的3D封裝技術(shù)首次引入了3D堆疊的優(yōu)勢,可實現(xiàn)在邏輯芯片上堆疊邏輯芯片。

2018-12-14 15:35:32 7850

7850 英特爾近日向業(yè)界推出了首款3D邏輯芯片封裝技術(shù)“Foveros”,據(jù)悉這是在原來的3D封裝技術(shù)第一次利用3D堆疊的優(yōu)點在邏輯芯片上進行邏輯芯片堆疊。也是繼多芯片互連橋接2D封裝技術(shù)之后的又一個顛覆技術(shù)。

2018-12-14 16:16:45 2343

2343 近日,武漢新芯研發(fā)成功的三片晶圓堆疊技術(shù)備受關(guān)注。有人說,該技術(shù)在國際上都處于先進水平,還有人說能夠“延續(xù)”摩爾定律。既然3D芯片堆疊技術(shù)有如此大的作用,那今天芯師爺就跟大家一起揭開它的面紗。

2018-12-31 09:14:00 30341

30341 對全新芯片堆疊技術(shù)的全面支持確保實現(xiàn)最高性能的3D-IC解決方案

2019-05-18 11:28:01 3642

3642 日前,麻省理工學(xué)院助理教授Max Shulaker在DARPA電子復(fù)興倡議(ERI)峰會上展示了一塊碳納米管+RRAM通過ILV技術(shù)堆疊的3DIC晶圓。

2019-08-05 15:08:16 2935

2935 對于我國的半導(dǎo)體行業(yè)來說,碳納米管+RRAM+ILV 3DIC是一個值得關(guān)注的領(lǐng)域。目前碳納米管+RRAM+ILV 3DIC是否能真正成為下一代標(biāo)準(zhǔn)半導(dǎo)體工藝還存在很大的不確定因素,因此在適當(dāng)

2019-09-09 17:00:42 5922

5922 困于10nm的Intel也在這方面尋找新的機會,其在去年年底的“架構(gòu)日”活動中,推出其業(yè)界首創(chuàng)的3D邏輯芯片封裝技術(shù)——Foveros,F(xiàn)overos首次引入3D堆疊的優(yōu)勢,可實現(xiàn)在邏輯芯片上堆疊

2020-01-28 16:10:00 3031

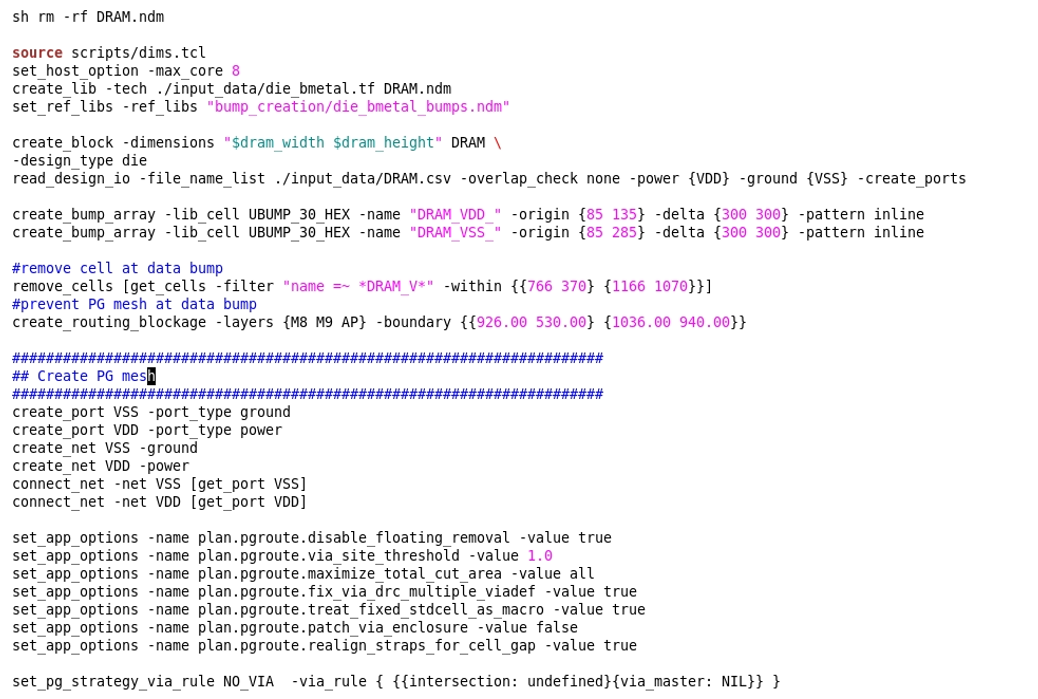

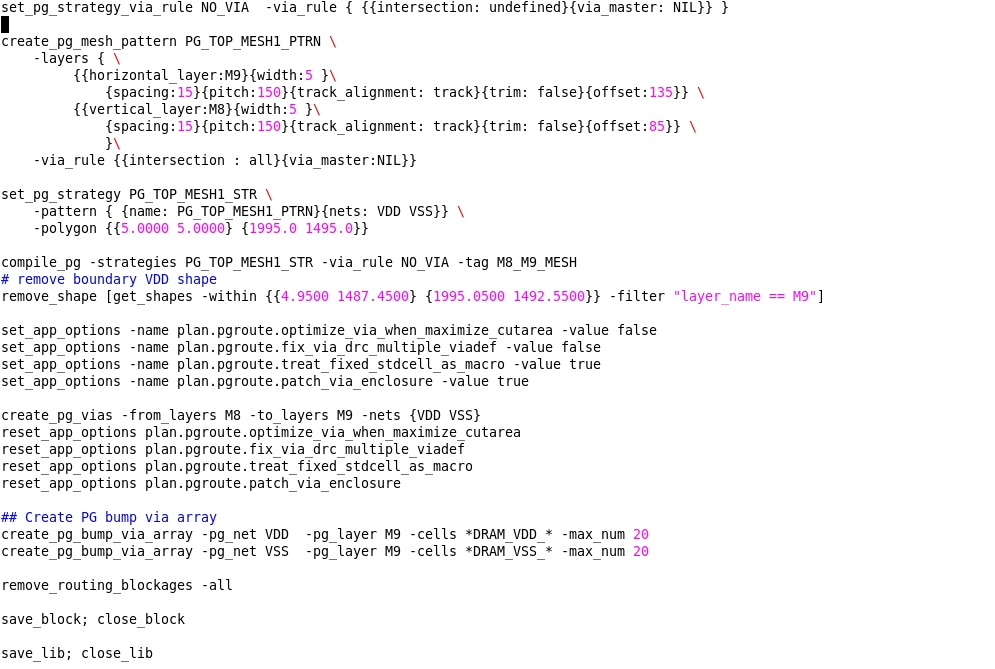

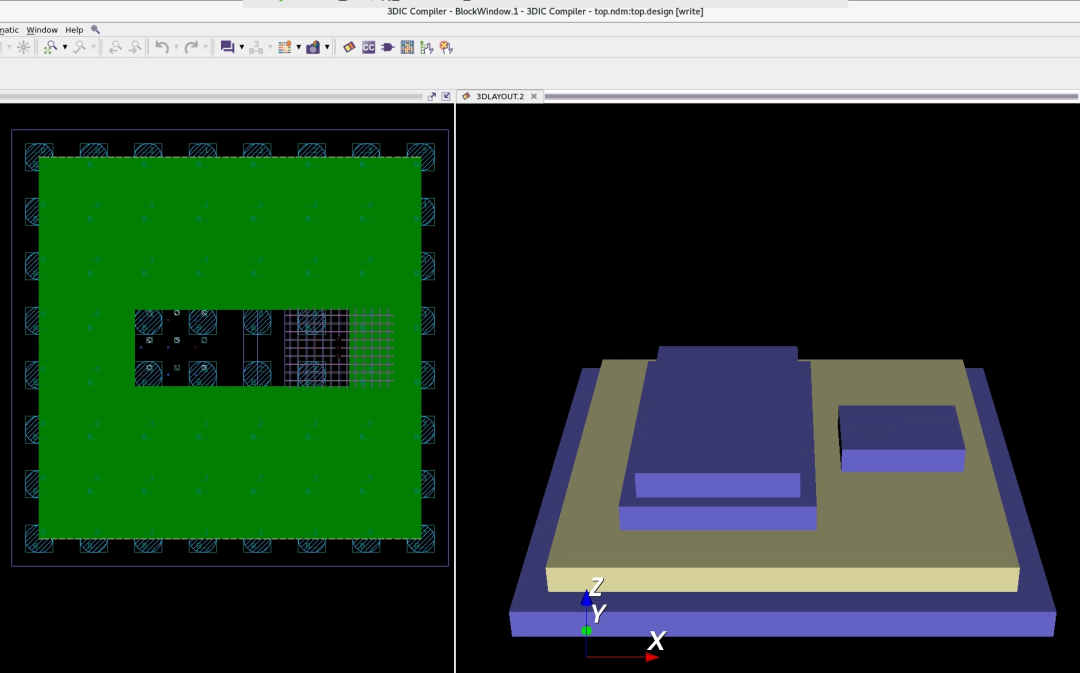

3031 新思科技的3DIC Compiler建立在一個IC設(shè)計數(shù)據(jù)模型的基礎(chǔ)上,通過更加現(xiàn)代化的3DIC結(jié)構(gòu),實現(xiàn)了容量和性能的可擴展性。該平臺提供了一個集規(guī)劃、架構(gòu)探究、設(shè)計、實現(xiàn)、分析和signoff于一體的環(huán)境。

2020-08-28 15:43:55 2457

2457 重點 ● TSMC認證基于新思科技3DIC Compiler統(tǒng)一平臺的CoWoS和InFO設(shè)計流程 ● 3DIC Compiler可提高先進封裝設(shè)計生產(chǎn)率 ● 集成Ansys芯片封裝協(xié)同分析解決方案

2020-10-14 11:11:21 2099

2099 AD2009:3個半的DIC線DPM過時的數(shù)據(jù)Sheet

2021-05-14 12:28:34 8

8 隨著摩爾定律的逐漸失效,縮小芯片尺寸的挑戰(zhàn)日益艱巨。但隨著新工藝和技術(shù)接連涌現(xiàn),芯片設(shè)計規(guī)模仍在持續(xù)拓展。其中一種方式就是采用3DIC,它將硅晶圓或裸晶垂直堆疊到同一個封裝器件中,從而帶來性能、功耗

2021-06-09 17:46:17 1962

1962 多芯片系統(tǒng)設(shè)計分析的統(tǒng)一平臺,為客戶構(gòu)建了一個完全集成、性能卓著且易于使用的環(huán)境,提供了從開發(fā)、設(shè)計、驗證、信號完整性仿真、電源完整性仿真到最終簽核的3DIC全流程解決方案。 隨著芯片制造工藝不斷接近物理極限,芯片的布局設(shè)計——異構(gòu)集成的3DIC先進

2021-08-30 13:32:23 1506

1506 隨著芯片制造工藝不斷接近物理極限,芯片的布局設(shè)計——異構(gòu)集成的3DIC先進封裝(以下簡稱“3DIC”)已經(jīng)成為延續(xù)摩爾定律的最佳途徑之一。

2021-08-30 14:12:17 1436

1436 3DIC架構(gòu)并非新事物,但因其在性能、成本方面的優(yōu)勢及其將異構(gòu)技術(shù)和節(jié)點整合到單一封裝中的能力,這種架構(gòu)越來越受歡迎。隨著開發(fā)者希望突破傳統(tǒng)二維平面IC架構(gòu)的復(fù)雜度和密度限制,3D集成提供了引入更多

2021-09-03 10:17:53 6458

6458 盛合晶微原名中芯長電半導(dǎo)體有限公司,是中國大陸第一家致力于12英寸中段凸塊和硅片級先進封裝的企業(yè),也是大陸最早宣布以3DIC多芯片集成封裝為發(fā)展方向的企業(yè)。

2021-10-11 14:14:51 1915

1915 新思科技3DIC Compiler是統(tǒng)一的多裸晶芯片設(shè)計實現(xiàn)平臺,無縫集成了基于臺積公司3DFabric技術(shù)的設(shè)計方法,提供完整的“探索到簽核”的設(shè)計平臺

2021-11-01 16:29:14 371

371 雙方拓展戰(zhàn)略合作,提供全面的3D系統(tǒng)集成功能,支持在單一封裝中集成數(shù)千億個晶體管 新思科技3DIC Compiler是統(tǒng)一的多裸晶芯片設(shè)計實現(xiàn)平臺,無縫集成了基于臺積公司3DFabric技術(shù)

2021-11-05 15:17:19 5826

5826 新思科技和三星晶圓廠(以下簡稱為“三星”)著力提升先進節(jié)點和多裸晶芯片封裝的創(chuàng)新和效率,滿足HPC、AI、汽車和5G等應(yīng)用的大量需求

2021-12-08 11:08:36 1231

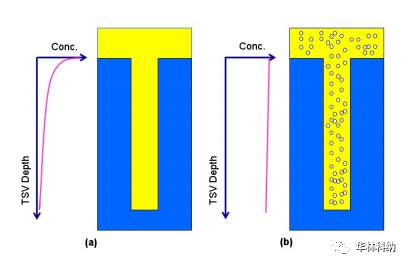

1231 直通硅通孔(TSV)器件是3D芯片封裝的關(guān)鍵推動者,可提高封裝密度和器件性能。要實現(xiàn)3DIC對下一代器件的優(yōu)勢,TSV縮放至關(guān)重要。

2022-04-12 15:32:46 942

942

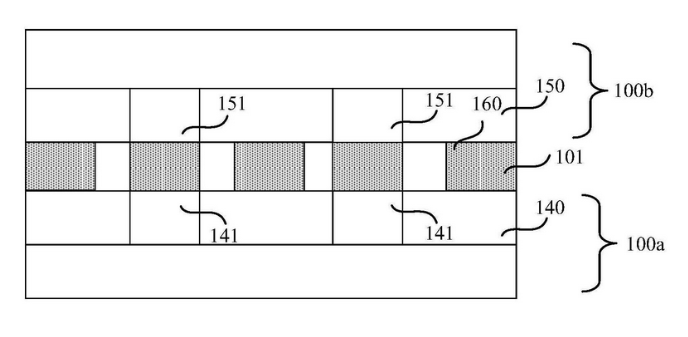

自今年4月5日華為公布芯片堆疊專利后,而過了一個月,5月6日,華為又公開了一項名為“芯片堆疊封裝結(jié)構(gòu)及其封裝方法、電子設(shè)備”的專利,申請公布號為CN114450786A。 據(jù)國家知識產(chǎn)權(quán)局官網(wǎng)顯示

2022-05-07 15:59:43 100213

100213 電子發(fā)燒友網(wǎng)報道(文/黃山明)近日,華為密集公布了多項技術(shù)專利,其中引人注意的是華為再次公布了兩項與芯片堆疊有關(guān)的專利。為何說再次,因為就在一個月前,華為同樣公開了“一種芯片堆疊封裝及終端設(shè)備”的專利。多項與芯片堆疊相關(guān)專利的公開,或許也揭露了華為未來在芯片技術(shù)上的一個發(fā)展方向。

2022-05-09 09:50:20 5437

5437 堆疊技術(shù)也可以叫做3D堆疊技術(shù),是利用堆疊技術(shù)或通過互連和其他微加工技術(shù)在芯片或結(jié)構(gòu)的Z軸方向上形成三維集成,信號連接以及晶圓級,芯片級和硅蓋封裝具有不同的功能,針對包裝和可靠性技術(shù)的三維堆疊處理技術(shù)。

2022-05-10 15:58:13 3605

3605

在芯片成品制造環(huán)節(jié)中,市場對于傳統(tǒng)打線封裝的依賴仍居高不下。市場對于使用多芯片堆疊技術(shù)、來實現(xiàn)同尺寸器件中的高存儲密度的需求也日益增長。這類需求給半導(dǎo)體封裝工藝帶來的不僅僅是工藝能力上的挑戰(zhàn),也對工藝的管控能力提出了更高的要求。

2022-08-07 11:43:22 3393

3393 “芯片堆疊”技術(shù)近段時間經(jīng)常聽到,在前段時間蘋果舉行線上發(fā)布會時,推出了號稱“史上最強”的Apple M1 ultra,這就是一種采用堆疊思路設(shè)計的芯片。

2022-08-11 15:39:02 9324

9324

目前有多種基于 3D 堆疊方法, 主要包括: 芯片與芯片的堆疊( D2D) 、芯片與圓片的堆疊( D2W ) 以及圓片與圓片的堆疊( W2W) 。

2022-11-01 09:52:51 1430

1430 ? 芯和半導(dǎo)體2.5D/3D多芯片Chiplets解決方案

2022-11-24 16:54:08 550

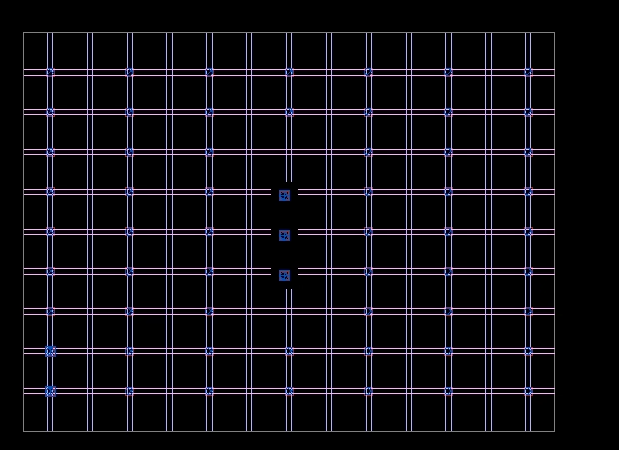

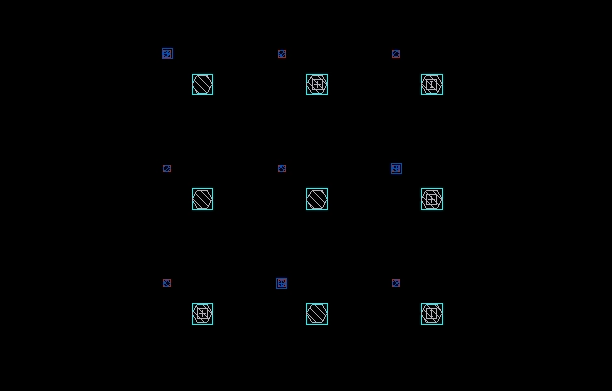

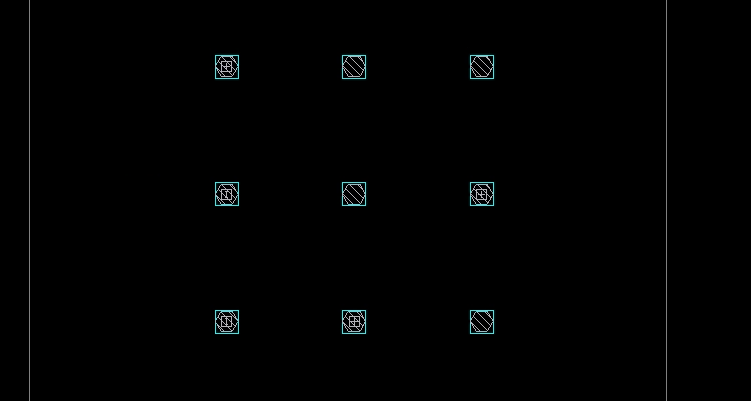

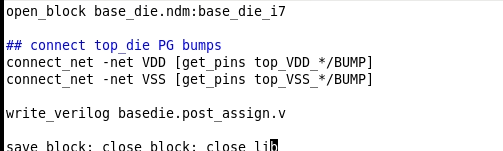

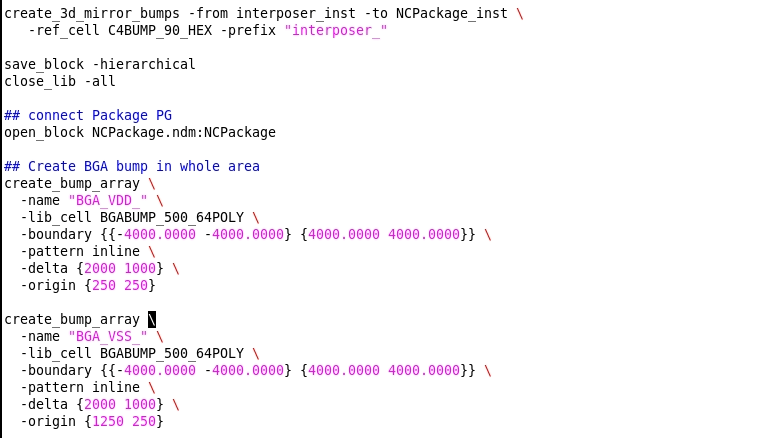

550 在沒有bump library cells的情況下,3DIC Compiler 如何在GUI界面使用“pseudo” bumps 快速實現(xiàn)Bump Planning,流程包括: 定義bump

2022-11-24 16:58:19 863

863 在3DFabric?技術(shù)和3Dblox?標(biāo)準(zhǔn)中的合作,新思科技提供了一系列全面的、系統(tǒng)級的、經(jīng)過產(chǎn)品驗證的解決方案,助力共同客戶能夠滿足復(fù)雜的多裸晶芯片系統(tǒng)對于功耗和性能的嚴(yán)苛要求。 經(jīng)過流片驗證的新思科技3DIC Compiler是該解決方案中的一個關(guān)鍵技術(shù)。作為統(tǒng)一的多裸晶芯片協(xié)同設(shè)計和分析平臺,

2022-12-01 14:10:19 486

486 為什么芯片可以進行堆疊呢?這里面我們講的主要是未經(jīng)過封裝的裸芯片。曾經(jīng)有用戶問我,封裝好的芯片可不可以進行堆疊呢?一般來說是不可以的,因為封裝好的芯片引腳在下表面直接焊接到基板上,而裸芯片的引腳一般在芯片上表面,通過鍵合的方式連接到基板。

2023-02-11 09:44:18 1596

1596 目前階段開始有同構(gòu)集成。國際上已經(jīng)有異構(gòu)集成CPU+GPU+NPU的Chiplet,其他功能芯片則采用次先進工藝制程的芯粒,感存算一體屬于3DIC的Chiplet這樣的方案可以靈活堆出算力高達200tops。

2023-02-14 15:00:00 2011

2011 HPC、AI、數(shù)據(jù)中心以及汽車自動化等應(yīng)用對于高效能和高性能算力需求持續(xù)增長,單芯片系統(tǒng)實現(xiàn)方案從設(shè)計、實現(xiàn)、生產(chǎn)制造、可靠性等各個方面都遇到了嚴(yán)峻的技術(shù)挑戰(zhàn)。

2023-02-15 16:01:39 1488

1488 下的“存儲墻”、“功耗墻”問題。存算一體將存儲與計算有機融合以其巨大的能效比提升潛力,有望成為數(shù)字經(jīng)濟時代的先進生產(chǎn)力。存算一體芯片設(shè)計迭代和投產(chǎn)的效率至關(guān)重要,如何能夠設(shè)計出更低損耗、更低噪聲、更低能耗,并符合信號完整性、電源完整性指標(biāo)性能的存算一體芯片,從而提高存算一體芯片的設(shè)計效率呢?

2023-02-24 09:34:28 2954

2954 M3T-NC30WA V.6.00 C/C++ Compiler 用戶手冊 (C/C++ Compiler Package for M16C Series and R8C Family)

2023-04-17 19:32:55 0

0 R32C/100 Series C Compiler Package V.1.02 C Compiler 用戶手冊

2023-04-19 19:24:26 0

0 M3T-NC308WA V.5.42 C Compiler 用戶手冊 (C Compiler Package for M32C Series)

2023-04-19 19:25:01 0

0 ?? 原文標(biāo)題:誰說3DIC系統(tǒng)設(shè)計難?最佳PPAC目標(biāo)輕松實現(xiàn) 文章出處:【微信公眾號:新思科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

2023-04-21 02:05:04 323

323

?? 原文標(biāo)題:下周五|誰說3DIC系統(tǒng)設(shè)計難?最佳PPAC目標(biāo)輕松實現(xiàn) 文章出處:【微信公眾號:新思科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

2023-04-21 19:30:01 273

273

? ? 原文標(biāo)題:仿真分析:3DIC全流程解決方案的第一步 文章出處:【微信公眾號:新思科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

2023-05-11 20:16:30 425

425

? ? 原文標(biāo)題:下周五|仿真分析:3DIC全流程解決方案的第一步 文章出處:【微信公眾號:新思科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

2023-05-11 20:16:35 276

276

? ? 原文標(biāo)題:本周五|仿真分析:3DIC全流程解決方案的第一步 文章出處:【微信公眾號:新思科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

2023-05-11 20:16:38 272

272

原文標(biāo)題:1+1>2?3DIC+Metis助力實現(xiàn)協(xié)同設(shè)計和仿真分析 文章出處:【微信公眾號:新思科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

2023-05-11 20:16:40 272

272

原文標(biāo)題:下周五|1+1>2?3DIC+Metis助力實現(xiàn)協(xié)同設(shè)計和仿真分析 文章出處:【微信公眾號:新思科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

2023-05-11 20:17:25 292

292

RH850 Family C Compiler Package CC-RH V1.02.00 用戶手冊: Compiler

2023-05-15 19:47:57 0

0 3DIC設(shè)計的重要性日益凸顯。當(dāng)今市場對AI應(yīng)用的需求在不斷增加,而摩爾定律的步伐卻在放緩,這使得芯片開發(fā)者不得不尋求其他類型的芯片架構(gòu),以滿足消費者和領(lǐng)先服務(wù)提供商的預(yù)期。3DIC設(shè)計并不是簡單

2023-06-27 17:35:01 746

746 RH850 Family C Compiler Package CC-RH V1.02.00 用戶手冊: Compiler

2023-07-12 18:40:53 0

0 芯片技術(shù)領(lǐng)域的應(yīng)用概要,用于簡化芯片堆疊結(jié)構(gòu)及其形成方法、芯片封裝結(jié)構(gòu)、電子設(shè)備、芯片堆棧結(jié)構(gòu)的制造技術(shù)。該芯片的堆疊結(jié)構(gòu)至少包括兩個堆疊的芯片,每一個芯片包括電線層,電線層設(shè)有電具組。

2023-08-09 10:13:42 1369

1369

新思科技經(jīng)認證的多裸晶芯片系統(tǒng)設(shè)計參考流程和安全的Die-to-Die IP解決方案,加速了三星SF 5/4/3工藝和I-Cube及X-Cube技術(shù)的設(shè)計和流片成功。 新思科技3DIC

2023-09-14 09:38:28 839

839 長期以來,個人計算機都可以選擇增加內(nèi)存,以便提高處理超大應(yīng)用和大數(shù)據(jù)量工作的速度。由于3D芯片堆疊的出現(xiàn),CPU芯粒也有了這個選擇,但如果你想打造一臺更具魅力的計算機,那么訂購一款有超大緩存的處理器可能是正確的選擇。

2023-10-15 10:24:23 371

371

交換機為什么要堆疊?有哪些設(shè)備可以堆疊?如何建立堆疊? 交換機的堆疊是一種將多個交換機連接在一起管理和操作的技術(shù)。通過堆疊,管理員可以將一組交換機視為一個虛擬交換機來進行集中管理和配置,提供靈活性

2023-11-09 09:24:35 1140

1140 作為全球領(lǐng)先的互聯(lián)產(chǎn)品和解決方案公司,奇異摩爾期待以自身 Chiplet 互聯(lián)芯粒、網(wǎng)絡(luò)加速芯粒產(chǎn)品及全鏈路解決方案,結(jié)合智原全面的先進封裝一站式服務(wù),通力協(xié)作,深耕 2.5D interposer 與 3DIC 領(lǐng)域,攜手開啟 Chiplet 時代的新篇章。

2023-11-12 10:06:25 456

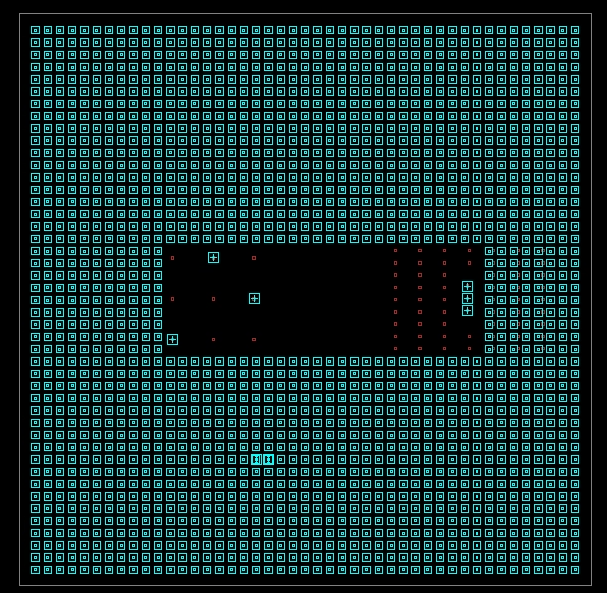

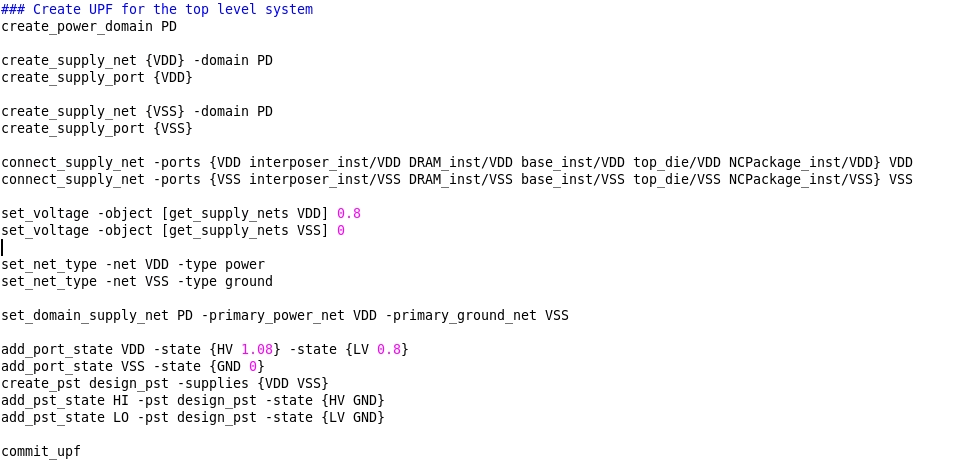

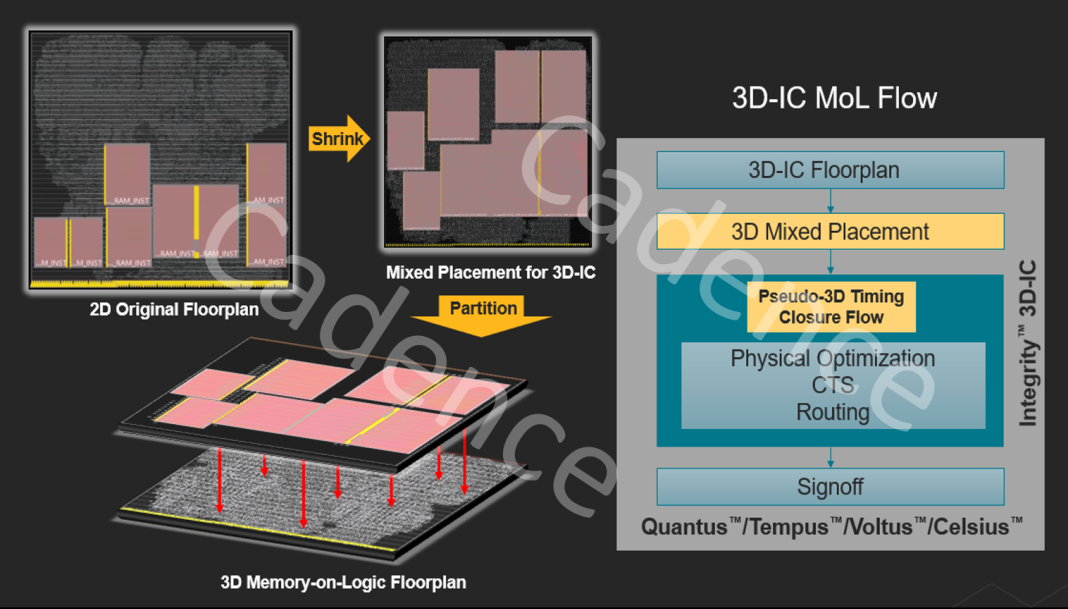

456 3D-IC 設(shè)計之 Memory-on-Logic 堆疊實現(xiàn)流程

2023-12-01 16:53:37 255

255

TSV是2.5D和3D集成電路封裝技術(shù)中的關(guān)鍵實現(xiàn)技術(shù)。半導(dǎo)體行業(yè)一直在使用HBM技術(shù)將DRAM封裝在3DIC中。

2023-11-27 11:40:20 211

211

利用Multi-Die系統(tǒng)能實現(xiàn)異構(gòu)集成,并且利用較小Chiplet實現(xiàn)更高良率,更小的外形尺寸和緊湊的封裝,降低系統(tǒng)的功耗和成本。Ansys半導(dǎo)體產(chǎn)品研發(fā)主管Murat Becer指出:“3DIC正在經(jīng)歷爆炸性增長,我們預(yù)計今年3DIC設(shè)計的數(shù)量將是去年的3倍左右。”

2023-11-29 16:35:48 268

268 本文介紹了堆疊線的定義、分類、作用以及與光纖線的區(qū)別,并提供詳細的堆疊線接法和相關(guān)問題的解答。堆疊線是一種用于連接網(wǎng)絡(luò)設(shè)備的高性能數(shù)據(jù)線纜,通過在設(shè)備之間建立邏輯連接,實現(xiàn)設(shè)備的堆疊和集中管理。

2024-01-08 13:43:04 230

230 新思科技3DIC Compiler集成了3Dblox 2.0標(biāo)準(zhǔn),可用于異構(gòu)集成和“從架構(gòu)探索到簽核”的完整解決方案。

2024-01-12 13:40:50 232

232

什么是交換機堆疊?有哪些設(shè)備可以堆疊?如何建立堆疊? 交換機堆疊是指將多個交換機通過特定的方法連接在一起,形成一個邏輯上的單一設(shè)備。堆疊可以實現(xiàn)多交換機的集中管理和統(tǒng)一配置,提供更高的可靠性和性能

2024-02-04 11:21:47 379

379 ; 新思科技廣泛的高質(zhì)量 IP組合降低集成風(fēng)險并加快產(chǎn)品上市時間,為采用Intel 18A 工藝的開發(fā)者提供了競爭優(yōu)勢; 新思科技 3DIC Compiler提供了覆蓋架構(gòu)探索到簽收的統(tǒng)一平臺,可實現(xiàn)采用

2024-03-05 10:16:59 84

84

電子發(fā)燒友App

電子發(fā)燒友App

評論