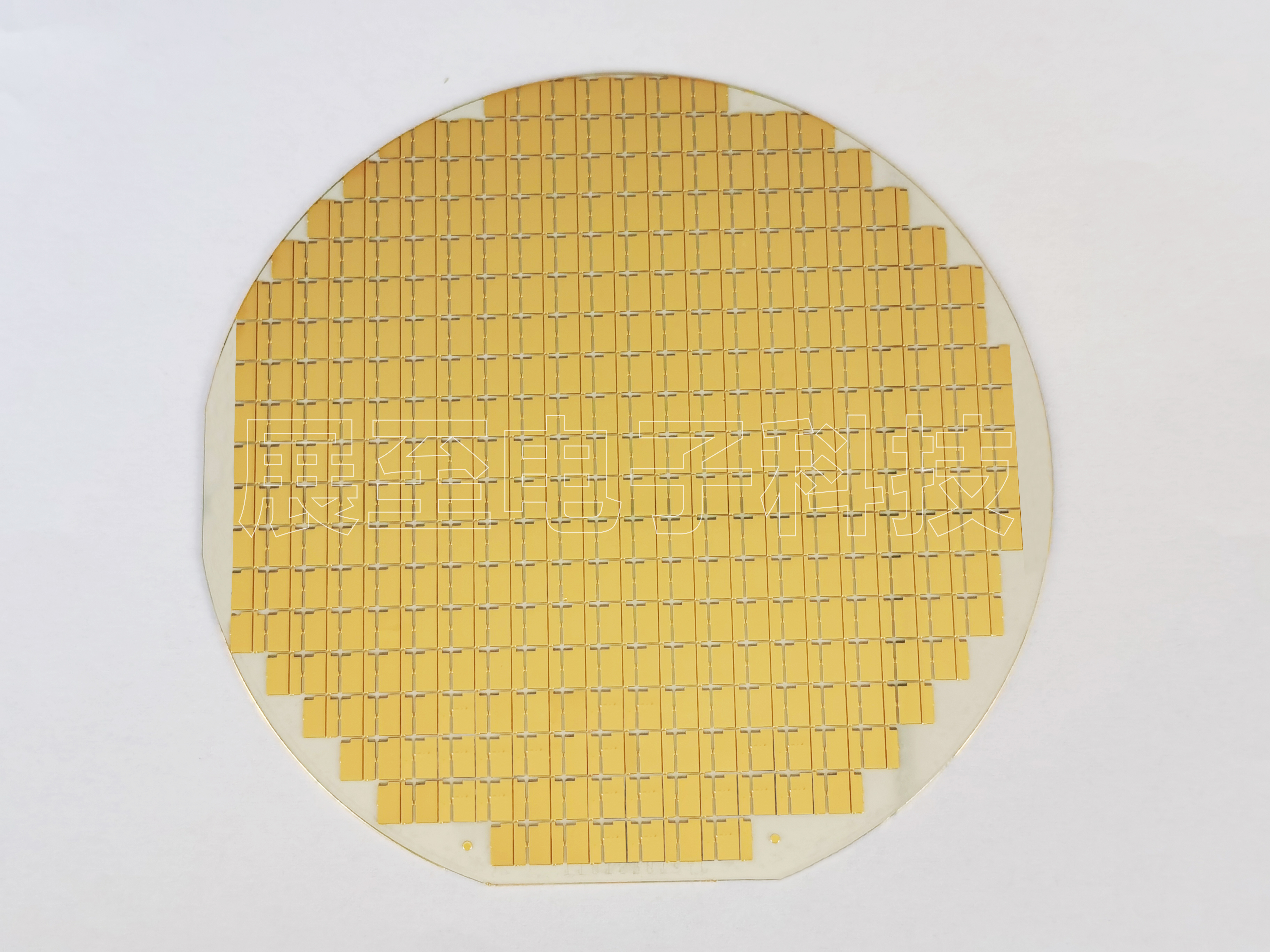

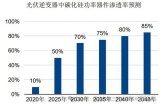

二十多年來,碳化硅(Silicon Carbide,SiC)作為一種寬禁帶功率器件,受到人們越來越多的關注。

與硅相比,碳化硅具有很多優(yōu)點,如:碳化硅的禁帶寬度更大,這使碳化硅器件擁有更低的漏電流及更高的工作溫度,抗輻照能力得到提升;碳化硅材料擊穿電場是硅的 10 倍,因此,其器件可設計更高的摻雜濃度及更薄的外延厚度,與相同電壓等級的硅功率器件相比,導通電阻更低;碳化硅具有高電子飽和速度的特性,使器件可工作在更高的開關頻率;同時,碳化硅材料更高的熱導率也有助于提升系統(tǒng)的整體功率密度。

碳化硅器件的高頻、高壓、耐高溫、開關速度快、損耗低等特性,使電力電子系統(tǒng)的效率和功率密度朝著更高的方向前進。

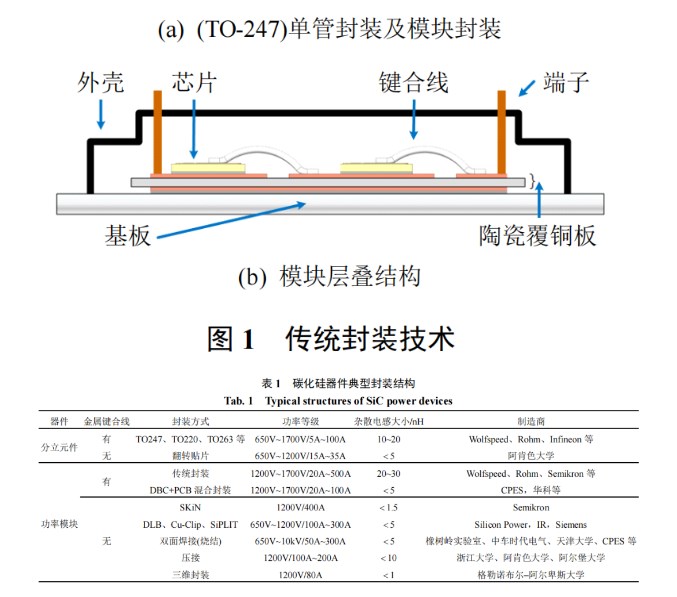

碳化硅器件的這些優(yōu)良特性,需要通過封裝與電路系統(tǒng)實現(xiàn)功率和信號的高效、高可靠連接,才能得到完美展現(xiàn),而現(xiàn)有的傳統(tǒng)封裝技術應用于碳化硅器件時面臨著一些關鍵挑戰(zhàn)。?碳化硅器件的結電容更小,柵極電荷低,因此,開關速度極快,開關過程中的 dv/dt 和 di/dt 均極高。雖然器件開關損耗顯著降低,但傳統(tǒng)封裝中雜散電感參數(shù)較大,在極高的 di/dt 下會產(chǎn)生更大的電壓過沖以及振蕩,引起器件電壓應力、損耗的增加以及電磁干擾問題。在相同雜散電容情況下,更高的dv/dt 也會增加共模電流。

針對上述問題,國內外學者們研究開發(fā)了一系列新的封裝結構,用于減小雜散參數(shù),特別是降低雜散電感。除開關速度更快外,碳化硅器件的工作溫度可達到 300℃以上。而現(xiàn)有適用于硅器件的傳統(tǒng)封裝材料及結構一般工作在 150℃以下,在更高溫度時可靠性急劇下降,甚至無法正常運行。解決這一問題的關鍵在于找出適宜高溫工作的連接材料,匹配封裝中不同材料的熱性能。此外,多功能集成封裝技術以及先進的散熱技術在提升功率密度等方面也起著關鍵作用。本文重點就低雜散電感封裝、高溫封裝以及多功能集成封裝 3 個關鍵技術方向對現(xiàn)有碳化硅功率器件的封裝進行梳理和總結,并分析和展望所面臨的挑戰(zhàn)和機遇。

1、低雜散電感封裝技術?

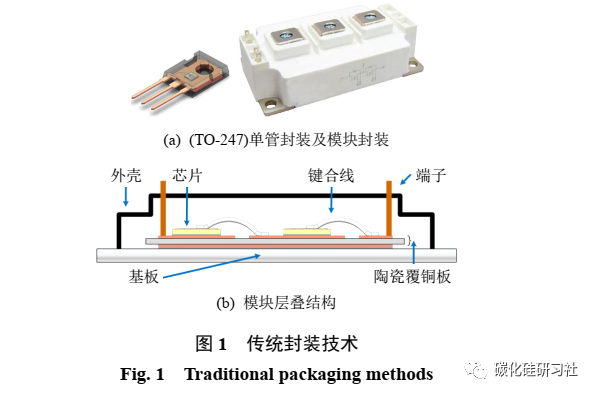

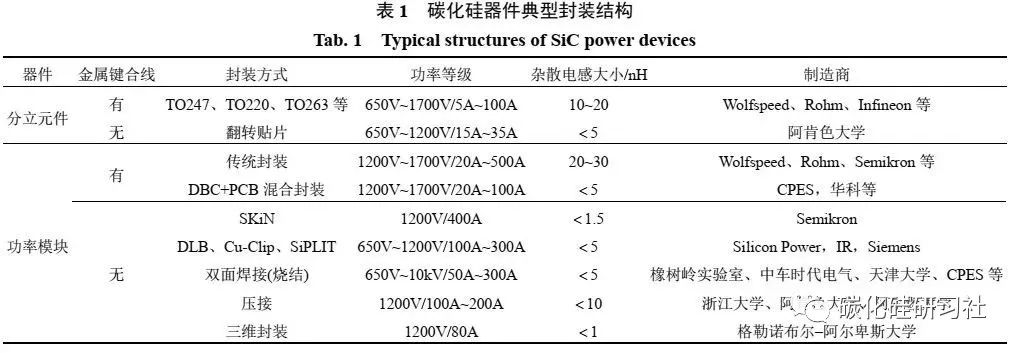

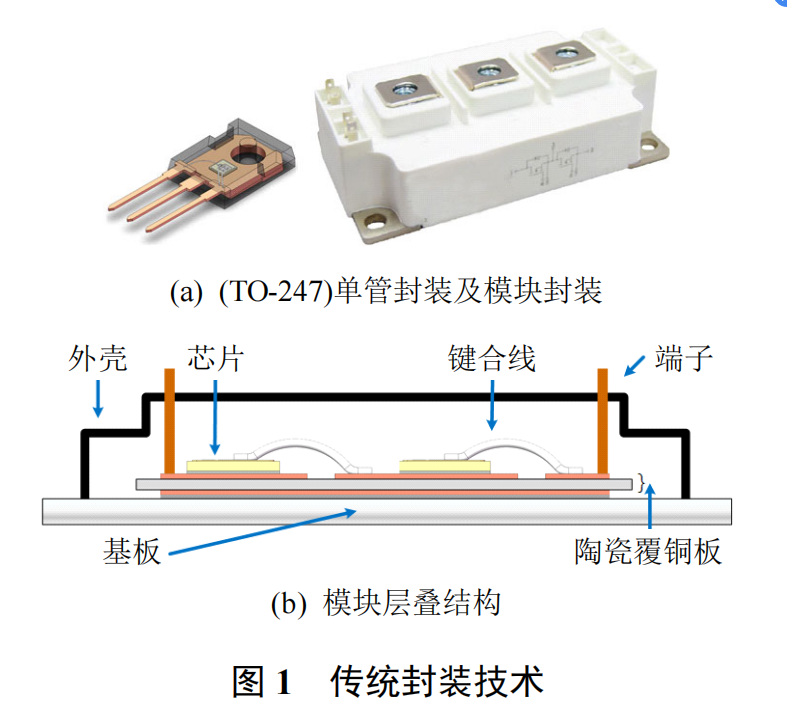

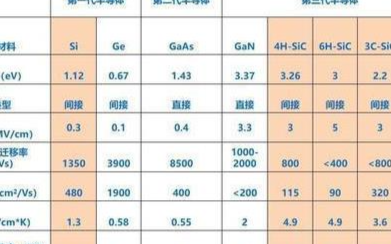

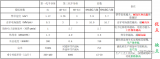

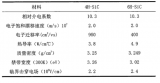

目前已有的大部分商用 SiC 器件仍采用傳統(tǒng) Si器件的封裝方式,如圖 1 所示。該方式首先通過焊錫將芯片背部焊接在基板上,再通過金屬鍵合線引出正面電極,最后進行塑封或者灌膠。傳統(tǒng)封裝技術成熟,成本低,而且可兼容和替代原有 Si 基器件。?但是,傳統(tǒng)封裝結構導致其雜散電感參數(shù)較大,在碳化硅器件快速開關過程中造成嚴重電壓過沖,也導致?lián)p耗增加及電磁干擾等問題。而雜散電感的大小與開關換流回路的面積相關。其中,金屬鍵合連接方式、元件引腳和多個芯片的平面布局是造成傳統(tǒng)封裝換流回路面積較大的關鍵影響因素。表 1 列出了典型的碳化硅器件封裝結構并進行分類,同時列出了相關封裝方式的雜散電感參數(shù)大小。由表 1 可知,消除金屬鍵合線可以有效減小雜散電感值,將其大小控制在 5nH 以下。下面就其中典型的封裝結構分別進行介紹。

1.1 單管翻轉貼片封裝

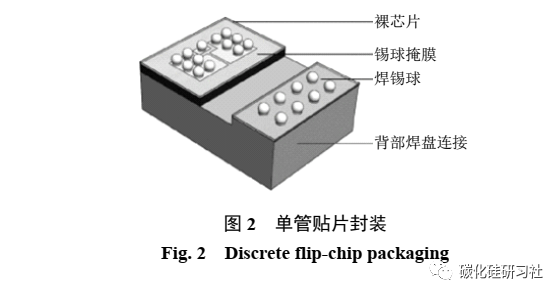

阿肯色大學團隊借鑒 BGA 的封裝技術,提出了一種單管的翻轉貼片封裝技術,如圖 2 所示。該封裝通過一個金屬連接件將芯片背部電極翻轉到和正面電極相同平面位置,然后在相應電極位置上植上焊錫球,消除了金屬鍵合線和引腳端子。相比于 TO-247 封裝,體積減小了 14 倍,導通電阻減小了 24%。

1.2 DBC+PCB 混合封裝

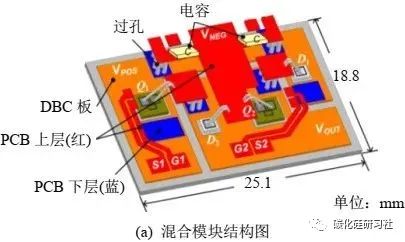

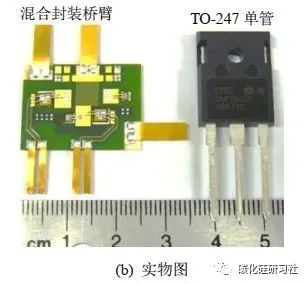

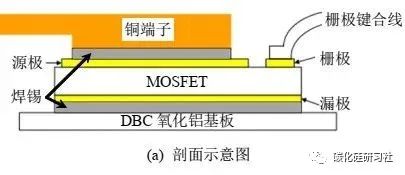

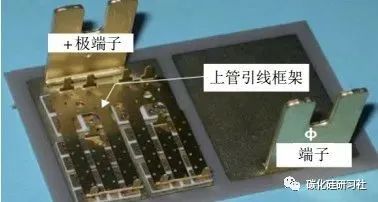

傳統(tǒng)模塊封裝使用的敷銅陶瓷板(direct bonded copper-DBC)限定了芯片只能在二維平面上布局,電流回路面積大,雜散電感參數(shù)大。CPES、華中科技大學等團隊將DBC 工藝和 PCB 板相結合,利用金屬鍵合線將芯片上表面的連接到 PCB 板,控制換流回路在 PCB 層間,大大減小了電流回路面積,進而減小雜散電感參數(shù)。如圖 3 所示,該混合封裝可將雜散電感可控制在 5nH 以下,體積相比于傳統(tǒng)模塊下降 40%。

?

?

柔性PCB 板結合燒結銀工藝的封裝方式也被用于商業(yè)模塊中。如圖 4 所示為 Semikron 公司利用SKiN 封裝技術制作的 1200V/400A 的 SiC 模塊[11]。該技術采用柔性 PCB 板取代鍵合線實現(xiàn)芯片的上下表面電氣連接,模塊內部回路寄生電感僅有1.5nH,開關速度大于 50kV/?s,損耗相比于傳統(tǒng)模塊可降低 50%。

該混合封裝方式結合了 2 種成熟工藝的優(yōu)勢,易于制作,可實現(xiàn)低雜散電感以及更小的體積。但PCB 板的存在限制了上述封裝方式高溫運行的可靠性。

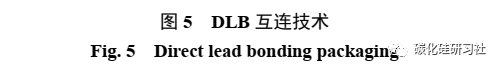

1.3 芯片正面平面互連封裝

除采用柔性 PCB 板取代金屬鍵合線外,還可使用平面互連的連接方式來實現(xiàn)芯片正面的連接。圖 5 為 SiliconPower 公司采用端子直連(direct lead bonding,DLB)的焊接方法,類似的還有IR 的Cu-Clip IGBT,Siemens 的 SiPLIT 技術等。平面互連的方式不僅可以減小電流回路,進而減小雜散電感、電阻,還擁有更出色的溫度循環(huán)特性以及可靠性。

?

?

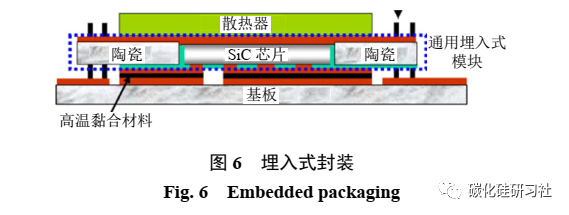

用于 SiC 芯片的埋入式封裝也可認為是一種芯片正面的平面直連封裝。如圖 6 所示,該方法將芯片置于陶瓷定位槽中,再用絕緣介質填充縫隙,最后覆蓋掩膜兩面濺射金屬銅,實現(xiàn)電極連接。通過選擇合理的封裝材料,減小了模塊在高溫時的層間熱應力,并能在 279℃的高溫下測量模塊的正反向特性。

平面直連的封裝工藝通過消除金屬鍵合線,將電流回路從 DBC 板平面布局拓展到芯片上下平面的層間布局,顯著減小了回路面積,可實現(xiàn)低雜散電感參數(shù),與之后介紹的雙面散熱封裝以及三維封裝實現(xiàn)低雜散電感的基本思路相同,只是實現(xiàn)方式略有不同。

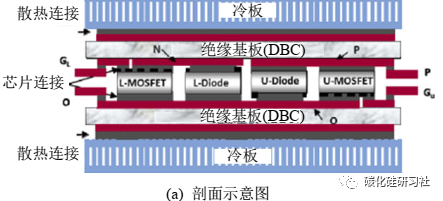

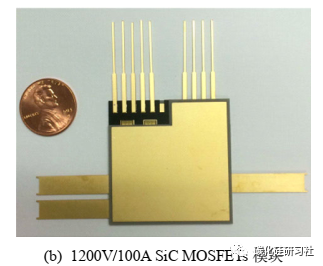

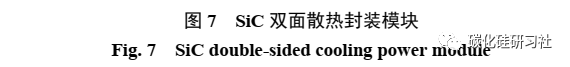

1.4 雙面散熱封裝技術

雙面封裝工藝由于可以雙面散熱、體積小,較多用于電動汽車內部 IGBT 的封裝應用。圖7為一典型的雙面散熱封裝 SiC 模塊,該模塊上下表面均采用 DBC 板進行焊接,所以可實現(xiàn)上下表面同時散熱。

?

?

該工藝的難點在于,芯片上表面需要進行濺射或電鍍處理使其可焊接,并且在芯片上表面增加金屬墊片、連接柱等來消除同一模塊中不同高度芯片的高度差。再加上 SiC 芯片普遍面積小,如何保證在上表面有限面積范圍內的焊接質量是該工藝過程中的關鍵。得益于上下 DBC 的對稱布線與合理的芯片布局,該封裝可將回路寄生電感參數(shù)降到3nH 以下,模塊熱阻相比于傳統(tǒng)封裝下降38%。國內如株洲中車時代電氣、天津大學等團隊都對此類雙面封裝模塊進行了熱、電氣、可靠性等多方面的研究。

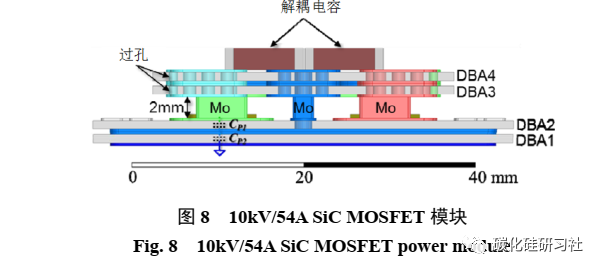

CPES?針對 10kV 的 SiC MOSFET 采用了如圖 8所示的封裝設計。使用銀燒結技術將芯片和敷鋁陶瓷板(direct bonded aluminum,DBA)、鉬片相連接。其中芯片下部采用兩層 DBA 板疊加,并將中間層連接到母線中間電壓,一方面可以減小板子邊緣的場強,另一方面減小了橋臂中點對地的寄生電容,降低 EMI。該模塊可以采用雙面散熱,也可將瓷片電容焊接在芯片上部 DBA 板上,減小回路寄生電感到小于 5nH。

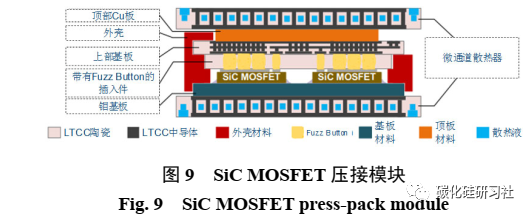

圖 9 為浙江大學和阿肯色大學合作提出的一種用于 SiC MOSFET 的雙面壓接模塊。該模塊使用低溫共燒陶瓷(LTCC)工藝和帶有彈性的 Fuzz Button 取代傳統(tǒng) DBC 板和金屬鍵合線實現(xiàn)芯片互聯(lián)以及散熱設計,回路寄生電感參數(shù)僅為 4.3nH。不足之處在于 LTCC 導熱系數(shù)低,而且壓接模塊的特性對外部壓力反應敏感。此外還有浙江大學與阿爾堡大學合作設計的直接通過螺釘固定的雙面壓接 SiC MOSFET 模塊,也實現(xiàn)了低寄生電感參數(shù)和良好均勻的散熱特性。

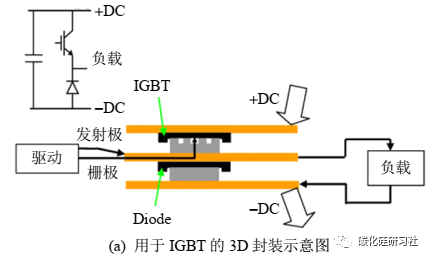

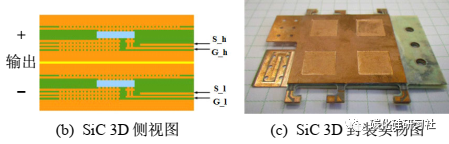

1.5 三維(3D)封裝技術

三維封裝技術利用了 SiC 功率器件垂直型的結構特點,將開關橋臂的下管直接疊在上管之上,消除了橋臂中點的多余布線,可將回路寄生電感降至1nH 以下。Vagnon于 2008 年即提出了利用金屬片直連的模塊單元,如圖10(a)所示,并基于此封裝制作了 Buck 變換器模塊。

實驗測試表明,該 3D 封裝模塊基本消除了共源極電感,而且輻射電磁場相比于傳統(tǒng)模塊大大減小,共模電流也得到了很好的抑制。類似的,文獻將 SiCMOSFET芯片嵌入 PCB 內部,形成如圖 10(b)所示的 3D 封裝形式。芯片表面首先經(jīng)過鍍銅處理,再借由過孔沉銅工藝將芯片電極引出,最后使用PCB 層壓完成多層結構,圖 10(c)為實物模塊。得益于PCB 的母排結構,模塊回路電感僅有 0.25nH,并可同時實現(xiàn)門極的開爾文連接方式。

該封裝的功率密度極高,如何保證芯片溫度控制是一大難點,外層銅厚和表面熱對流系數(shù)對芯片散熱影響很大。除功率芯片之外,無源元件如磁芯,電容等均可通過適當?shù)姆绞角度?PCB 當中以提高功率密度。

?

?

由上述新型結構可以看出,為充分發(fā)揮 SiC 器件的優(yōu)勢,提高功率密度,消除金屬鍵合線連接是一種趨勢。通過采用各種新型結構,降低模塊回路寄生電感值,減小體積是推進電力電子走向高頻、高效、高功率密度的保證。

2 高溫封裝技術

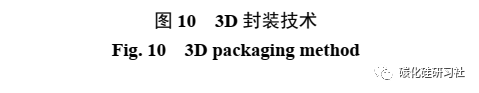

在進行芯片正面連接時可用銅線替代鋁線,消除了鍵合線與 DBC 銅層之間的熱膨脹系數(shù)差異,極大地提高模塊工作的可靠性。此外,鋁帶、銅帶連接工藝因其更大的截流能力、更好的功率循環(huán)以及散熱能力,也有望為碳化硅提供更佳的解決方案。圖 11 所示分別為銅鍵合線、銅帶連接方式。

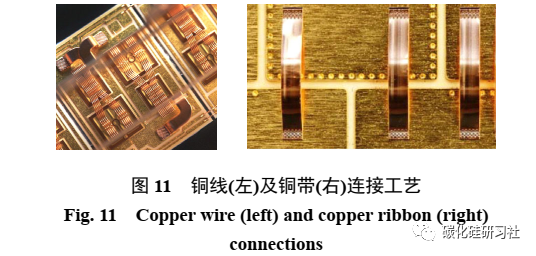

錫片或錫膏常用于芯片和 DBC 板的連接,焊接技術非常成熟而且簡單,通過調整焊錫成分比例,改進錫膏印刷技術,真空焊接減小空洞率,添加還原氣體等可實現(xiàn)極高質量的焊接工藝。但焊錫熱導率較低(~50W/(m?K)),且會隨溫度變化等,并不適宜 SiC 器件在高溫下工作。

此外,焊錫層的可靠性問題也是模塊失效的一大原因。燒結銀連接技術憑借其極高的熱導率(~200W/(m?K)),低燒結溫度,高熔點等優(yōu)勢,有望取代焊錫成為 SiC 器件的新型連接方法[38-39]。銀燒結工藝通常是將銀粉與有機溶劑混合成銀焊膏,再印刷到基板上,通過預熱除去有機溶劑,然后加壓燒結實現(xiàn)芯片和基板的連接。

為降低燒結溫度,一種方法是增大燒結中施加的壓力,這增加了相應的設備成本,而且容易造成芯片損壞;另一種方法是減小銀顆粒的體積如采用納米銀顆粒,但顆粒加工成本高,所以很多研究繼續(xù)針對微米銀顆粒進行研究以得到合適的燒結溫度、壓力、時間參數(shù)來現(xiàn)更加理想的燒結效果。圖 12 給出了一些典型的焊錫和燒結材料的熱導率和工作溫度對比圖。

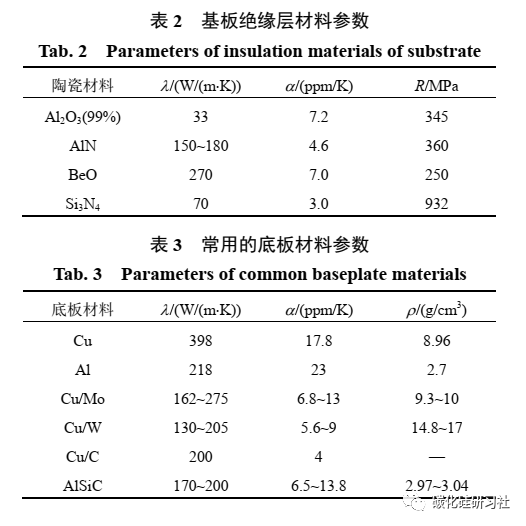

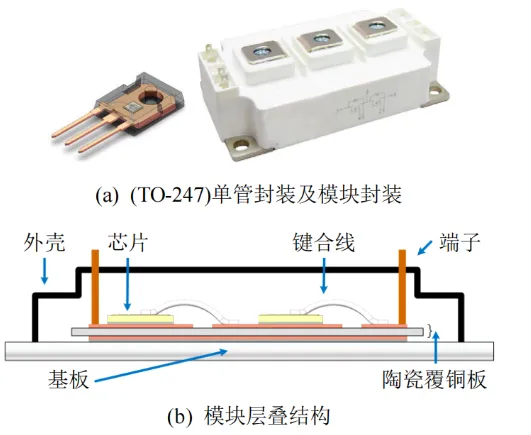

此外,為確保碳化硅器件穩(wěn)定工作,陶瓷基板和金屬底板也需要具備良好的高溫可靠性。表 2、3分別給出了目前常用的一些基板絕緣材料和底板材料,其中:λ 為熱導率;α為熱膨脹系數(shù);R為撓曲強度;ρ 為密度。λ 越高,散熱效果越好,α 則影響了封裝在高溫工作時不同層材料之間的熱應力大小,不同材料間α 差異越大,材料層間熱應力就越高,可靠性越低。所以提高λ值?、α 值和碳化硅材料(3.7ppm/K)相近的材料是提高封裝可靠性和關鍵所在。

如表2 所示,Al2O3 具有成本低,機械強度高等優(yōu)點,是目前最常用的絕緣材料,但λ 值低,α值明顯偏大,不適合碳化硅的高溫工作。

AlN λ值高,α 值接近 SiC 材料,成本合適,是目前較為理想的碳化硅器件的基板材料。BeO 雖然 λ 值高,但其強毒性則限制了其應用。

Si3N4 α 值最接近 SiC材料,而且 R 值大,在熱循環(huán)中更不容易斷裂,也是一種適合碳化硅器件高溫工作的絕緣材料,但其λ值較低,而且成本很高,限制了其廣泛的應用。

為提高陶瓷基板覆銅層的可靠性,覆鋁陶瓷板(DBA)以及活性金屬釬焊(active metal brazing,AMB)等工藝也受到人們越來越多的關注。如表 3所示,Cu 作為底板材料熱導率最高,但其與基板之間熱膨脹系數(shù)相差較大。

Al 作為底板,成本低,還可顯著降低整體重量,但在熱導率和熱膨脹系數(shù)匹配方面均表現(xiàn)較差。Cu基合金如 Cu/Mo,Cu/W,Cu/C 等在熱導率和熱膨脹系數(shù)方面性能均較為優(yōu)越,但其密度和成本均較高。

AlSiC 的成本,密度,熱膨脹系數(shù)均十分理想,但缺點在于熱導率較低。具體使用情況需要結合實際情況綜合決定。

綜上可以看出,材料是保證碳化硅器件高溫可靠工作的根本。而在實際設計過程是,考慮多方面綜合因素尋找最合適的材料也是器件封裝設計中的一大難點所在。

3?多功能集成封裝技術??

3.1 多功能集成封裝技術

碳化硅器件的出現(xiàn)推動了電力電子朝著小型化的方向發(fā)展,其中集成化的趨勢也日漸明顯。瓷片電容的集成較為常見,通過將瓷片電容盡可能靠近功率芯片可有效減小功率回路寄生電感參數(shù),減小開關過程中的震蕩、過沖現(xiàn)象。但目前瓷片電容不耐高溫,所以并不適宜于碳化硅的高溫工作情況。

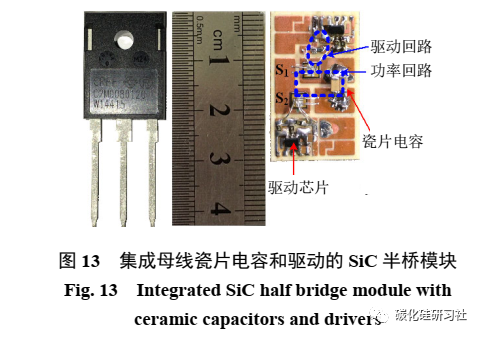

驅動集成技術也逐漸引起了人們的重視,三菱、英飛凌等公司均提出了 SiC 智能功率模塊(intelligent power module,IPM),將驅動芯片以及相關保護電路集成到模塊內部,并用于家電等設備當中。如圖 13 所示,浙江大學團隊通過將瓷片電容、驅動芯片和 1200V SiC 功率芯片集成在同一塊 DBC 板上,使半橋模塊面積僅為 TO-247 單管大小,極大地減小了驅動回路和功率回路的寄生電感參數(shù)。阿肯色大學則針對碳化硅芯片開發(fā)了相關的 SiC CMOS 驅動芯片以充分開發(fā) SiC 的高溫性能。

此外,還有 EMI 濾波器集成,溫度、電流傳感器集成、微通道散熱集成等均有運用到碳化硅封裝設計當中。

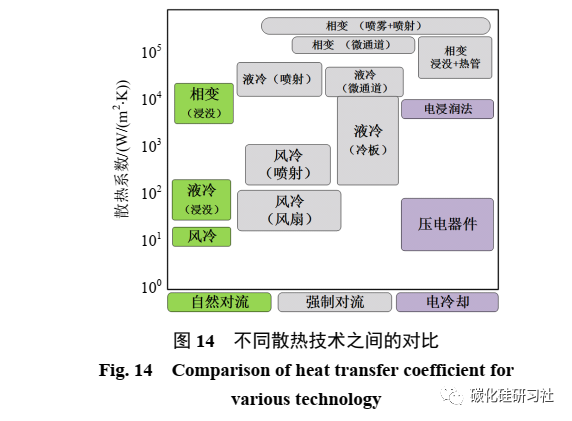

3.2 散熱技術

散熱技術也是電力電子系統(tǒng)設計的一大重點和難點。設計中,通常是將單管或模塊貼在散熱器上,再通過風冷或者液冷進行散熱。將微通道集成在模塊的基板內,使得模塊整體熱阻下降 34%。

微通道散熱技術也被用于芯片的直接散熱,例如文獻中介紹了用于寬禁帶器件的 3 種典型方式:一種是將微通道直接做在芯片的襯底上;第 2 種則將微通道集成在芯片下層的厚金屬層中;第 3 種則通過金屬鍍層和熱介質材料將芯片直接連接到 Si 基微通道結構上。

這種直接作用于芯片的散熱技術消除了模塊多層結構的限制,可以極大提高芯片的散熱效率。相變散熱技術如熱管、噴霧等方式相比于單相氣冷、水冷等具有更高的熱導率,非常高效,也為 SiC 器件的散熱提供了一種解決思路。圖 14 給出了目前的散熱方式之間的傳熱系數(shù)簡單對比。

4 挑戰(zhàn)機遇和前景展望?

在電力電子朝著高效高功率密度發(fā)展的方向上前進時,器件的低雜散參數(shù)、高溫封裝以及多功能集成封裝起著關鍵性作用。通過減小高頻開關電流回路的面積實現(xiàn)低雜散電感是碳化硅封裝的一種技術發(fā)展趨勢。然而,實現(xiàn)碳化硅封裝技術的突破并大規(guī)模應用,還需要開展大量的工作,以下列舉一些核心挑戰(zhàn)以及前景展望:

1)低雜散電感封裝結構綜合性能的進一步研究驗證。例如封裝結構的功率循環(huán)、溫度循環(huán)能力,實際散熱效果,制造難度和成本,以及實現(xiàn)大功率模組的串并聯(lián)難易程度等。

2)適用于高溫工作的封裝材料的研究。開發(fā)耐高溫、具有優(yōu)良導熱系數(shù)、熱膨脹系數(shù)相互匹配的封裝材料始終是提升封裝高溫工作可靠性的關鍵;同時,改進工藝、降低現(xiàn)有優(yōu)良封裝材料的生產(chǎn)成本和工藝難度也是封裝朝著高溫方向發(fā)展的重要制約因素。

3)多功能集成封裝模塊的內部干擾、共同散熱等關鍵問題研究。模塊的多功能集成是電力電子的發(fā)展趨勢,但瓷片電容、傳感器、柵極驅動等還無法完全匹配碳化硅的高溫高頻性能、散熱和電磁兼容問題;開發(fā)高溫電容、功率芯片片內集成傳感器、研究 SiC CMOS 驅動芯片或者采用 SOI(silicon on insulator)等工藝方案都有待進一步探索。

4)新型散熱方式的探索。減小芯片散熱路徑上的熱阻是封裝散熱技術的關鍵,一方面,利用高導熱系數(shù)材料,另一方面可以減少封裝的層疊結構,如:DBC 直連散熱器、微通道液冷散熱器集成及芯片直接散熱方式等均為碳化硅器件的散熱提供了更多的可能。可以預見,碳化硅器件和封裝技術的發(fā)展已經(jīng)為電力電子技術打開了一扇更廣闊的大門,助力電力電子技術朝著高頻、高效、高功率密度的方向前進。

?5 結論?

本文分析和探討了碳化硅器件封裝中的 3 個關鍵技術問題:

1)整理歸納了低雜散電感參數(shù)的新型封裝結構,從設計原理上概括了其基本思路并列舉了一些典型封裝結構;

2)總結了目前常用的一些高溫封裝方式和材料特性等,并指出高溫封裝中的關鍵性問題和解決思路;

3)綜述概括了現(xiàn)有的碳化硅封裝多功能集成的趨勢以及散熱技術。最后,對碳化硅的封裝技術作了展望,指出了其所面臨的挑戰(zhàn)和機遇。

審核編輯:湯梓紅

電子發(fā)燒友App

電子發(fā)燒友App

評論