核心結論

1. 先進制程受限,先進封裝/Chiplet提升算力,必有取舍。

在技術可獲得的前提下,提升芯片性能,先進制程升級是首選,先進封裝則錦上添花。

2. 大功耗、高算力的場景,先進封裝/Chiplet有應用價值。

3. 我國先進制程產能儲備極少,先進封裝/Chiplet有助于彌補制程的稀缺性。

先進封裝/Chiplet可以釋放一部分先進制程產能,使之用于更有急迫需求的場景。

用面積和堆疊跨越摩爾定律限制

芯片升級的兩個永恒主題:性能、體積/面積。芯片技術的發展,推動著芯片朝著高性能和輕薄化兩個方向提升。而先進制程和先進封裝的進步,均能夠使得芯片向著高性能和輕薄化前進。面對美國的技術封裝,華為難以在全球化的先進制程中分一杯羹,手機、HPC等需要先進制程的芯片供應受到嚴重阻礙,亟需另辟蹊徑。而先進封裝/Chiplet等技術,能夠一定程度彌補先進制程的缺失,用面積和堆疊換取算力和性能。

1. 先進制程受限,先進封裝/Chiplet提升算力,必有取舍

何謂先進封裝?

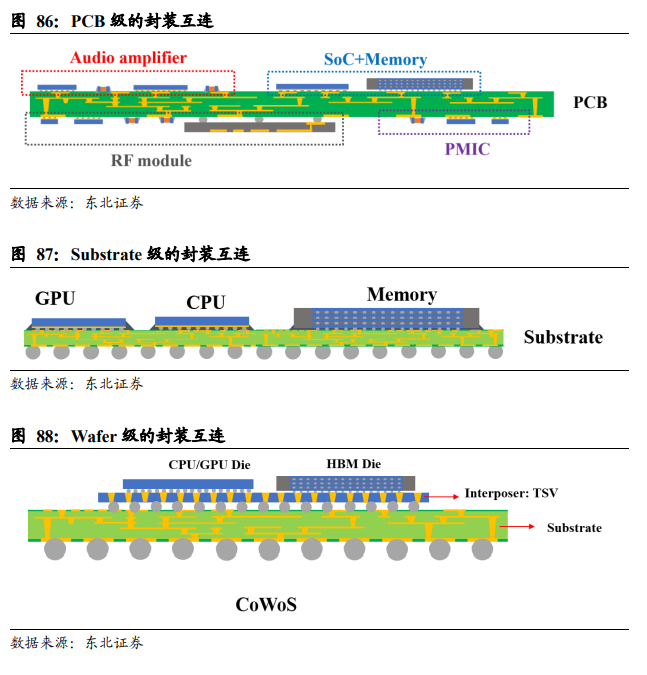

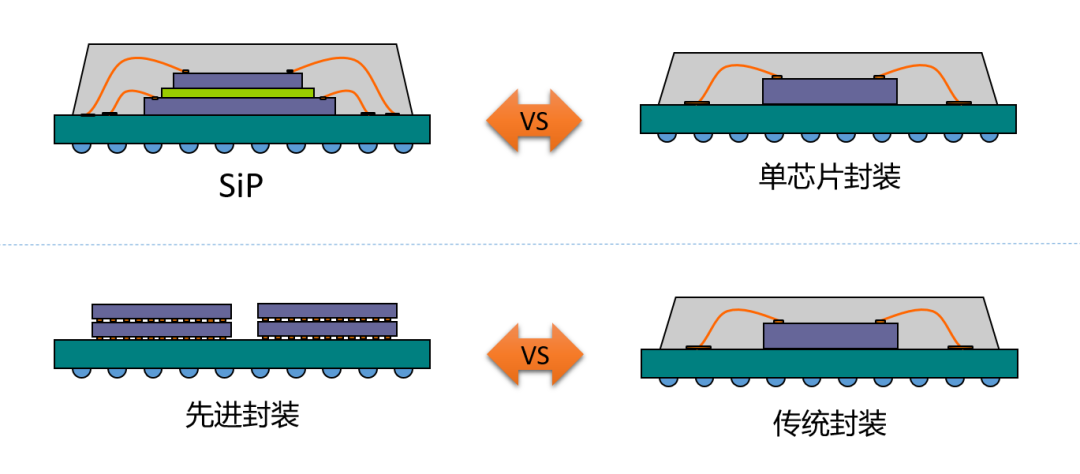

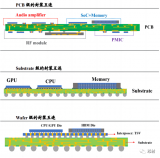

先進封裝是對應于先進圓晶制程而衍生出來的概念,一般指將不同系統集成到同一封裝內以實現更高效系統效率的封裝技術。換言之,只要該封裝技術能夠實現芯片整體性能(包括傳輸速度、運算速度等)的提升,就可以視為是先進封裝。傳統的封裝是將各個芯片單獨封裝好,再將這些單獨的封裝芯片裝配到PCB主板上構成完整的系統,芯片間的信息交換屬于PCB級的互連(interconnect),又稱板級互連;或者將不同的芯片貼裝到同一個封裝基板Substrate上,再完成系統級的封裝,芯片間的通訊屬于Substrate級的互連。這兩種形式的封裝互連技術,芯片間的信息傳輸需要通過PCB或Substrate布線完成。理論上,芯片間的信息傳輸距離越長,信息傳遞越慢,芯片組系統的性能就越低。因此,同一芯片水平下,PCB級互連的整體性能比Substrate級互連的性能弱。

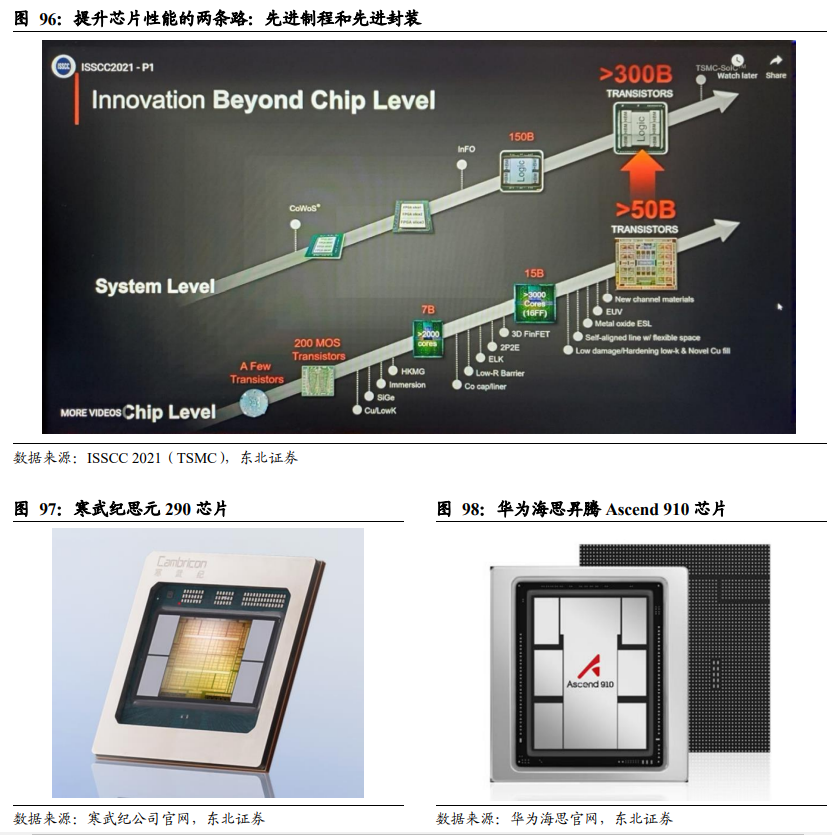

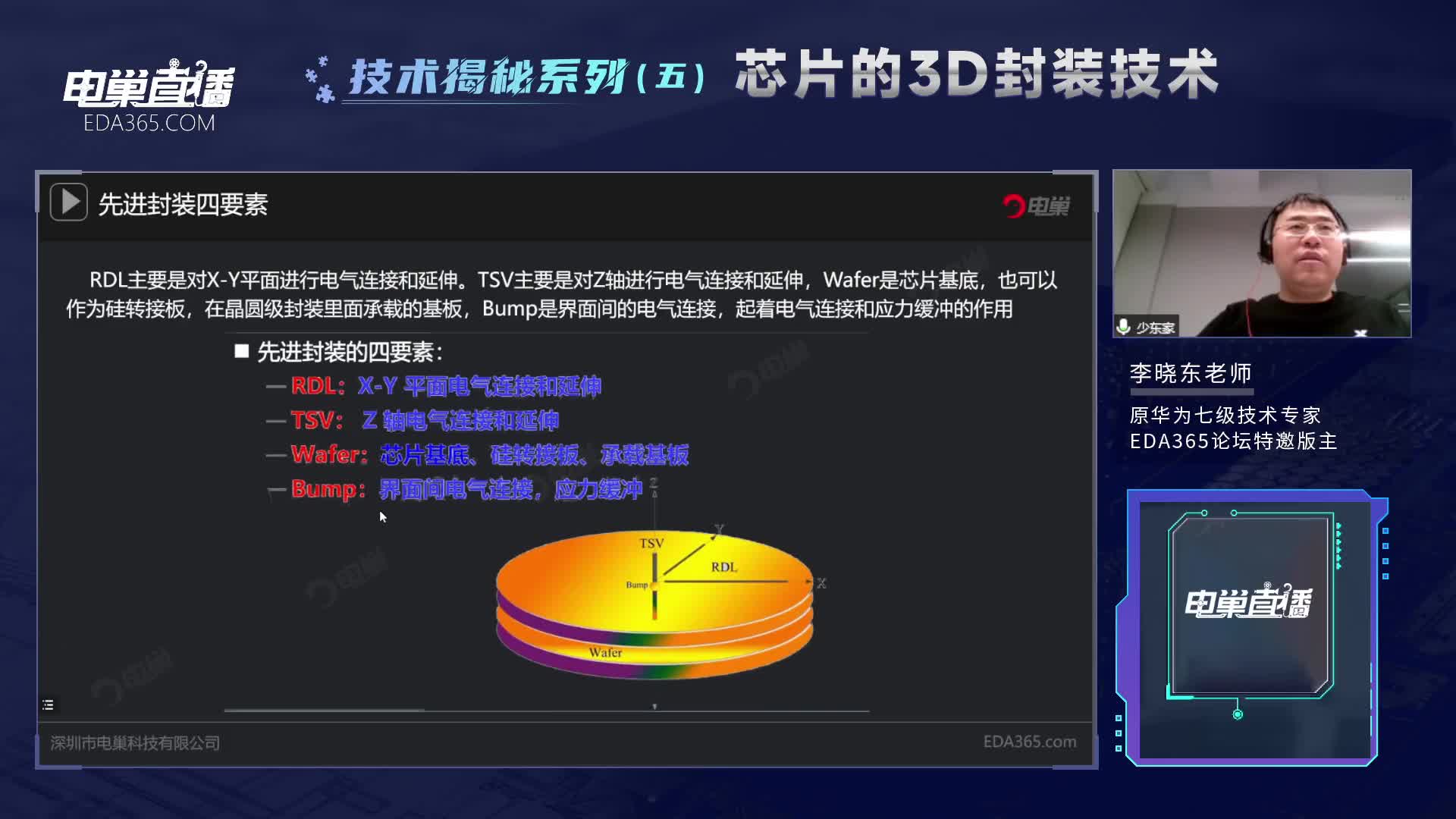

在摩爾定律失效之前,芯片系統性能的提升可以完全依賴于芯片本身制程提升(制程提升使得芯片集成晶體管數量提升)。但隨著摩爾定律失效,芯片制程提升速度大大放緩,芯片系統性能的提升只能通過不斷優化各個芯片間的信息傳輸效率,圓晶Wafer級封裝互連技術的價值凸顯。

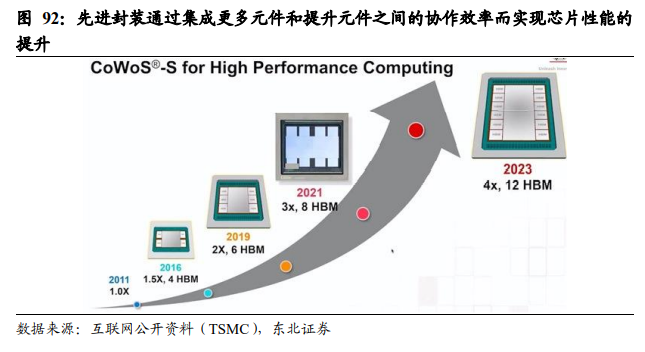

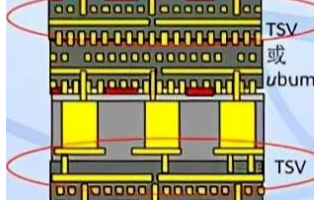

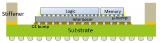

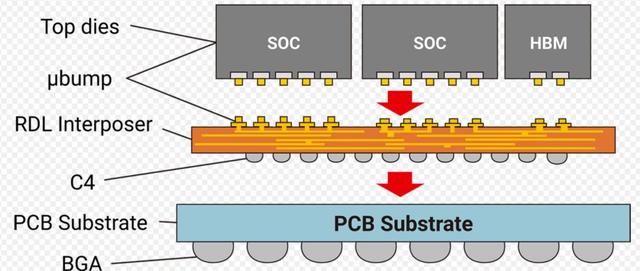

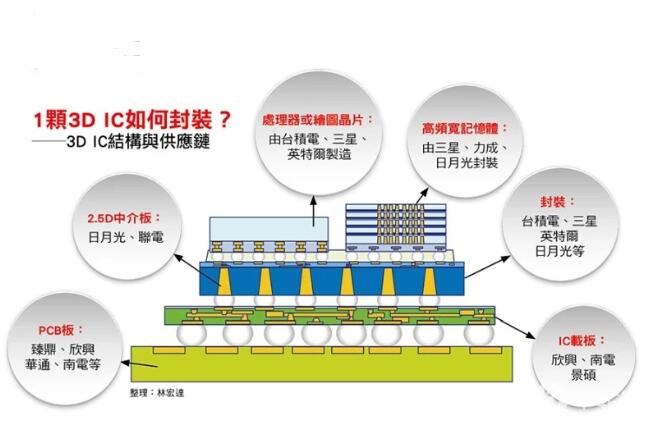

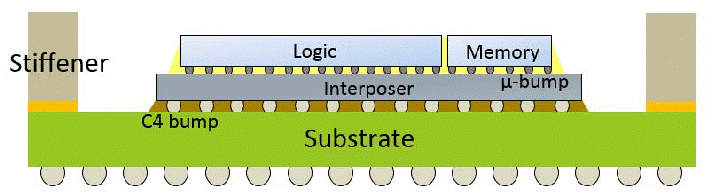

Wafer級的封裝互連技術,將不同的SoC集成在TSV(硅通孔技術:Through silicon via)內插板(interposer)上。Interposer本身材料為硅,與SoC的襯底硅片相同,通過TSV技術以及再布線(RDL)技術,實現不同SoC之間的信息交換。換言之,SoC之間的信息傳輸是通過Interposer完成。Interposer再布線采用圓晶光刻工藝,比PCB和Substrate布線更密集,線路距離更短,信息交換更快,因此可以實現芯片組整體性能的提升。圖XX示例為CoWoS封裝(Chip on Wafer on Substrate),CPU/GPU die與Memory die通過interposer實現互連,信息直接通過interposer上的RDL布線傳輸,不經過Substrate或PCB,信息交換快,系統效率高。

從半導體制程進入10nm以來,摩爾定律已經失效,即芯片迭代不再滿足“集成電路芯片上所集成的晶體管數目,每隔18個月就翻一番;微處理器的性能每隔18個月提高一倍,而價格下降一倍”。在后摩爾定律時代,對于“more than moore”的延續,先進封裝是業界公認的有效途徑。

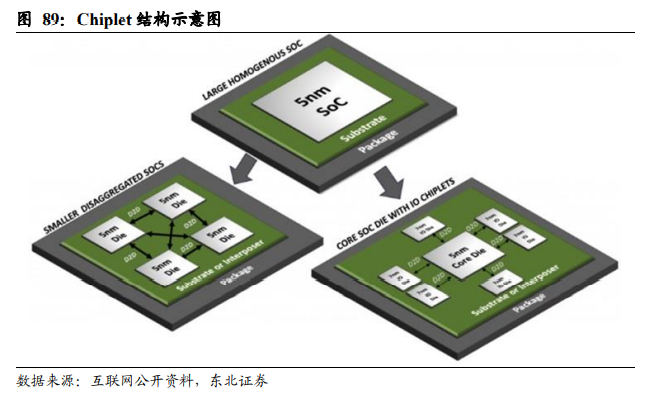

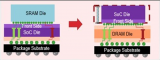

何謂Chiplet?

Chiplet即小芯片之意,指在晶圓端將原本一顆“大”芯片(Die)拆解成幾個“小”芯片(Die),因單個拆解后的“小”芯片在功能上是不完整的,需通過封裝,重新將各個“小”芯片組合起來,功能上還原原來“大”芯片的功能。Chiplet可以將一顆大芯片拆解設計成幾顆與之有相同制程的小芯片,也可以將其拆解成設計成幾顆擁有不同制程的小芯片。

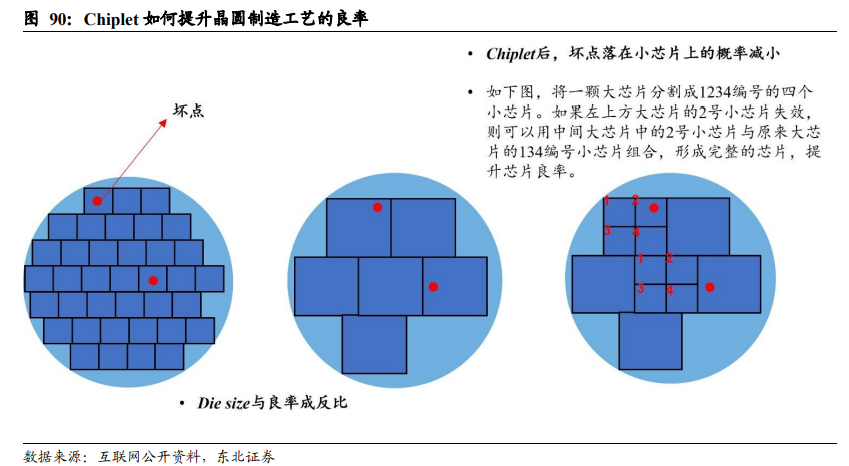

Chiplet可以提升芯片制造的良率。對于晶圓制造工藝而言,芯片面積(Die size)越大,工藝的良率越低。可以理解為,每片wafer上都有一定概率的失效點,對于晶圓工藝來說,在同等技術條件下難以降低失效點的數量,如果被制造的芯片,其面積較大,那么失效點落在單個芯片上的概率就越大,因而良率就越低。如果Chiplet的手段,將大芯片拆解分割成幾顆小芯片,單個芯片面積變小,失效點落在單個小芯片上的概率將大大降低。芯片面積Die size與良率成反比。(注:以上解讀僅為東北電子團隊調研學習理解后的觀點,不具備業界技術權威性,僅供投資者理解基礎概念用)

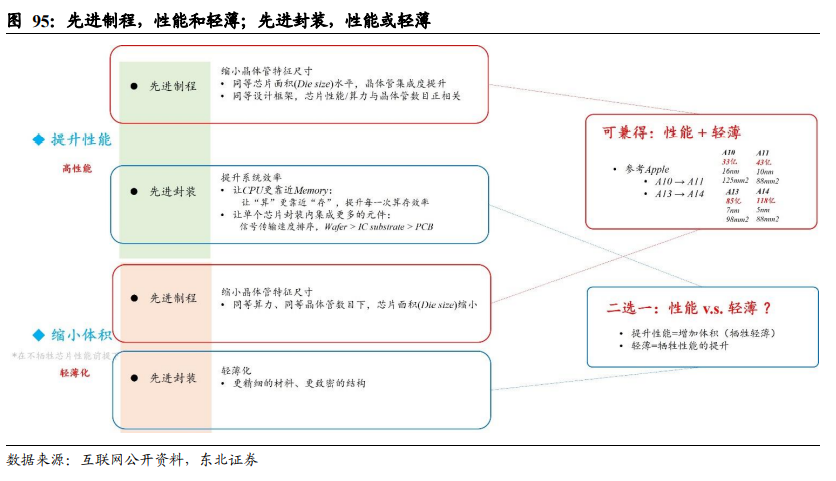

先進制程和先進封裝,對芯片性能、輕薄化的提升,孰更顯著?

在提升芯片性能方面,先進制程路線是通過縮小單個晶體管特征尺寸,在同等芯片面積(Die size)水平下,提升晶體管集成度(同等設計框架,芯片性能/算力與晶體管數目正相關);而先進封裝并不能改變單個晶體管尺寸,只能從系統效率提升的角度,一是讓CPU更靠近Memory,讓“算”更靠近“存”,提升每一次計算的算存效率。二是讓單個芯片封裝內集成更多的元件:信號傳輸速度排序,Wafer > IC substrate > PCB,元件在芯片內部的通訊效率比在板級上更高,從系統層面提升芯片性能。

在芯片輕薄化方面,在不犧牲芯片整體性能的前提下,先進制程能夠在算力和晶體管數目不變時,通過縮小單個晶體管特征尺寸,實現芯片面積(Die size)縮小;而先進封裝,因為封裝對晶體管尺寸無微縮的能力,只能通過更精細的材料、更致密的結構來實現輕薄化。比如,手機AP處理器的封裝多采用FCCSP的封裝形式,其結構包括一個CSP載板,而Fanout(TSMC與APPLE公司合作,APPLE公司的A系列芯片多采用InFO技術封裝,即Fannout)封裝,取消了CSP載板(CSP載板約0.3 mm厚度),封裝后的芯片更輕薄,對整機(手機)結構空間余量有重要提升。

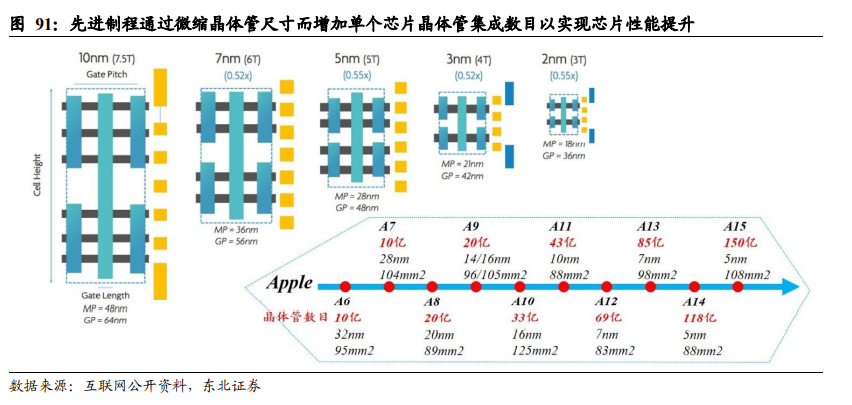

在高性能和輕薄化兩個方向上,先進制程可以做到兼顧,而先進封裝則有取舍。比如,APPLE的A系列芯片,從A10升級到A11時,由16 nm工藝提升至10 nm工藝,芯片面積從125 mm2減小至88 mm2,而晶體管集成數則由33億顆增加至43億顆;A系列芯片從A13升級到A14時,晶圓工藝從7nm升級到5nm,芯片面積從98 mm2減小至88 mm2,而晶體管集成數則由85億顆增加至118億顆,做到了性能提升和輕薄化的兼顧。而先進封裝,要做到芯片性能提升,因為封裝對晶體管尺寸微縮沒有效果,提升性能一是增加芯片內部各元件的協作效率,二是往一個系統中堆疊更多的元件(本質上也是提升了系統內的晶體管數據),代價就是系統體積、面積更為龐大,即先進封裝提升性能的代價是犧牲輕薄,實現輕薄的代價是犧牲性能的提升。

在技術可獲得的前提下,提升芯片性能,先進制程升級是首選,先進封裝則錦上添花。通常我們可以見到的是,高性能、大算力的芯片,會考慮上先進封裝(2.5D、CoWoS等),但這些大算力芯片往往也同時采用的先進制程工藝,也就是說,先進封裝/Chiplet應用通常只出現在頂級的旗艦芯片的封裝方案選擇中,并不是一個普適性的大規模應用方案。比如寒武紀的7 nm AI訓練芯片思元290,從芯片宣傳圖片可以看出,其可能采用“1+4”架構,即1顆CPU/GPU搭配4顆HBM存儲的Chiplet封裝形式,該芯片也是寒武紀的旗艦芯片產品之一;華為海思昇騰910芯片,采用7 nm的先進制程工藝,從宣傳圖可以看出,也是采用了多顆芯片堆疊的CoWoS結構,也系Chiplet的一種形式。這些芯片都是在擁有先進制程的基礎上,為了進一步提升芯片性能,而采用了CoWoS這些2.5D先進封裝技術,說明了先進制程在工藝路線的選擇上是優于先進封裝的,先進制程是升級芯片性能的首選,先進封裝則是錦上添花。

2. 大功耗、高算力的場景,先進封裝/Chiplet有應用價值

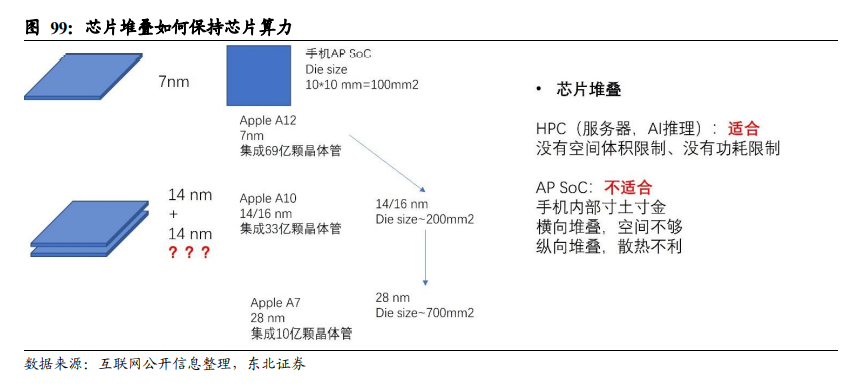

在先進制程不可獲得的情況下,通過芯片堆疊(先進封轉/Chiplet)和計算架構重構,以維持產品性能。以APPLE的A系列芯片參數為例,A12、A10、A7芯片分別采用7 nm、14/16 nm(Samsung 14 nm、TSMC 16 nm)、28 nm制程。A系列的手機AP芯片,通常芯片面積(Die Size)在約100 mm2大小。在這100 mm2大小的芯片上, A12、A10、A7芯片分別集成了約69億、33億、10億顆晶體管。下面,我們簡單進行算術換算,討論降制程如何維持芯片的算力。如果芯片工藝從7 nm降至14 nm,A12芯片上7nm工藝集成69億顆晶體管,如果用14 nm工藝以試圖達到接近的算力,首先要保證晶體管數目與A12芯片一致,即~70億顆,且在未考慮制程提升對單個晶體管性能有顯著提升的背景下,14 nm工藝的芯片需要兩倍于7 nm工藝的面積,即~200 mm2;如果芯片工藝從7 nm降至28 nm,參考28 nm的A7芯片只集成了10億顆晶體管,如果要達到70億晶體管數目,則需要將芯片面積擴大至~700 mm2。芯片面積越大,工藝良率越低,在實際制造中得到的單顆芯片的制造成本就越高,因此,在先進制程不可獲得的背景下,降制程而通過芯片堆疊的方式,的確可以一定程度減少算力劣勢,但是因為堆疊更多芯片,需要更大的IC載板、更多的Chiplet小芯片、更多的封裝材料,也導致因為制程落后帶來的功耗增大、體積/面積增加、成本的增加。因此,比如,通過14 nm的兩顆芯片堆疊,去達到同樣晶體管數目的7 nm芯片性能;通過多顆28 nm的芯片堆疊,去達到14 nm芯片性能。此種堆疊方案在HPC(服務器、AI推理)、基站類大芯片領域可能有適用價值,但對于消費電子領域如手機AP芯片和可穿戴芯片,在其應用場景對空間體積有嚴苛約束的條件下,芯片堆疊則較難施展。

3. 我國先進制程產能儲備極少,先進封裝/Chiplet有助于彌補制程的稀缺性

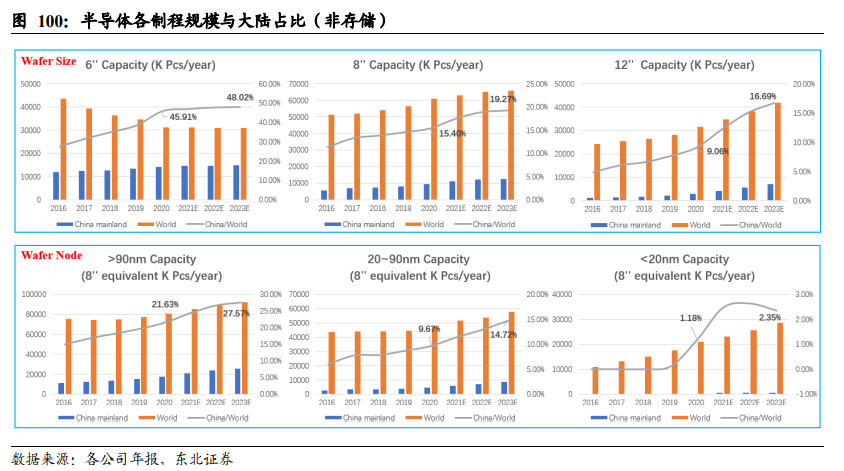

尖端科技全球化已死,大陸先進制程的產能極為稀缺、緊缺。按不同晶圓尺寸統計,大陸6英寸晶圓產能已占全球近一半,而12英寸產能僅為全球約10%。按不同制程統計,大陸90 nm以上制程占全球約20%,20-90 nm制程占全球約10%,20 nm以下制程僅占全球約1%。大陸高端制程占比低,產業結構存在明顯短板,未來擴產空間大。高端制程擴產投入大,3 nm制程芯片每萬片產能的投資約100億美元,遠高于28 nm制程芯片每萬片約7億美元的投資。彌補大陸晶圓產業結構短板,需重點投資高端制程晶圓制造產能,既需要完成技術攻關,又需要大額投資支持,任重而道遠。

先進封裝/Chiplet可以釋放一部分先進制程產能,使之用于更有急迫需求的場景。從上文分析可見,通過降制程和芯片堆疊,在一些沒有功耗限制和體積空間限制、芯片成本不敏感的場景,能夠減少對先進制程的依賴。可以將當下有限的先進制程產能,以更高的戰略視角,統一做好規劃,應用在更需要先進工藝的應用需求中。

研究團隊簡介:?

李玖:北京大學光學博士,北京大學國家發展研究院經濟學學士(雙學位),電子科技大學本科,曾任華為海思高級工程師、?光峰科技博士后研究員,具有三年產業經驗,2019 年加入東北證券,現任電子行業首席分析師。?

武芃睿:英國南安普頓大學光電研究中心碩士,華中科技大學光電信息本科,武漢大學工商管理學士(雙學位)。曾任華為和 上海微電子光電工程師,具有三年產業經驗,2020 年加入東北證券,現任電子行業高級分析師。

編輯:黃飛

?

電子發燒友App

電子發燒友App

評論