電子封裝是芯片成為器件的重要步驟,涉及的材料種類繁多,大量材料呈現顯著的溫度相關、率相關的非線性力學行為。 相關工藝過程中外界載荷與器件的相互作用呈現典型的多尺度、多物理場特點,對電子封裝的建模仿真方法也提出了相應的要求。 在可靠性驗證方面,封裝的失效主要包括熱-力致耦合失效、電-熱-力致耦合失效等。 隨著新型封裝材料、技術的涌現,電子封裝可靠性的試驗方法、基于建模仿真的協同設計方法均亟待新的突破與發展。

0 前言

電子封裝是電子制造產業鏈中將芯片轉換為能夠可靠工作的器件的過程。 由于裸芯片無法長期耐受工作環境的載荷、缺乏必要的電信號連接,無法直接用于電子設備。 因此,雖然不同類型產品有所差別,但是電子封裝的主要功能比較接近,主要包括四大功能:①機械支撐,將芯片及內部其他部件固定在指定位置; ②環境保護,保護芯片免受外界的水汽、腐蝕、灰塵、沖擊等載荷影響; ③電信號互連,為內部組件提供電通路及供電; ④散熱,將芯片工作時產生的熱量及時導出。 按照工藝階段的不同,電子封裝通常可分為零級封裝(芯片級互連)、一級封裝(芯片級封裝)、二級封裝(模塊級封裝)和三級組裝。

由于芯片及封裝涉及大量不同類型材料,部分材料特性相差甚遠,在封裝工藝過程中,如果內部缺陷、殘余應力、變形等問題控制不當,極易在封裝過程中或者產品服役中引發可靠性問題。 隨著封裝密度不斷提升、功能多樣化,如 3D 封裝、異質集成技術等,電子封裝中多場多尺度耦合的可靠性問題更加明顯。

1 電子封裝可靠性研究共性技術

1.1 典型封裝材料

目前制約微電子器件封裝快速發展的一大因素就是缺乏相應的封裝材料及完整的材料數據。 封裝材料關系著電子微器件的強度和可靠性,材料的力學響應對于封裝材料的選取和電子微器件的強度與可靠性設計非常關鍵。 因此急需針對典型封裝材料的優缺點進行評價、開發加速評估方法,展望適合未來封裝技術發展的先進封裝材料。

封裝材料一般包括:互連材料、基板材料和密封材料等。 其中互連材料與芯片直接接觸,對芯片散熱和可靠性最為關鍵,其需要耐受的溫度和應力也更高。 本文以封裝互連材料為例,介紹其研究進展與挑戰。

由于 RoHS 和 WEEE 指令的限制,Sn-Pb 焊料無法繼續應用于電子器件。 目前,無鉛焊料主要以錫為基礎,通過添加 Cu、Ag、Zn、Bi 等合金元素組成,主要包括 Sn-Cu 合金、Sn-Ag 合金、Sn-Ag-Cu合金、Sn-Zn 合金以及Sn-Bi合金等。

Sn-Cu 二元合金的共晶成分是 Sn-0.7Cu,共晶溫度為 227℃,Sn-Cu 合金由于其優異的力學性能和低廉的價格,被認為是含鉛焊料最有潛力的替代焊料。 Sn-Ag 二元合金的共晶成分是 Sn-3.5Ag,共晶溫度是 221℃。 Sn-Ag 合金具有優異的力學性能和較好的可靠性,其缺點是潤濕性比較差且表面張力比較高。 為克服這一缺點,人們在 Sn-Ag 合金中加入Cu 形成了具有優異潤濕性和力學性能的 Sn-Ag-Cu 合金,它已成為近年來使用最廣泛的焊料合金。

有研究通過添加一些稀土元素來進一步改善焊料的綜合性能。 Sn 和 Zn 元素可以以固溶體的形式存在,Sn-Zn 系合金的研究也有明顯的進展,但其潤濕性、抗氧化性、力學性能和熱學性能往往不相匹配。 Sn-Bi 系合金也是典型的低熔點合金,但硬度高、延伸率低,其導電性和導熱性略低于前幾種合金焊料。

當前,隨著半導體技術的發展,以 SiC 為代表的寬禁帶半導體材料由于其導熱系數高、介電常數低、帶隙高,可以實現器件在 200℃ 以上結溫下穩定工作,是功率半導體器件的必然發展趨勢。 當環境溫度高于 200℃ 時,絕大多數焊點合金的抗疲勞性能和抗蠕變性能均無法滿足寬禁帶器件互連的可靠性要求。 雖然個別焊料合金可以勉強滿足高溫封裝要求,但它們價格昂貴(如 Au/Sn,Au/Ge,Au/Si)或者加工性差(如 Bi/Ag,Zn/Al)。 因此,急需發展新型的耐高溫連接材料和技術。

近年來,研究人員在耐高溫互連材料方面做了大量努力。 提出了多種滿足寬禁帶電子器件高溫封裝要求的互連技術。 其中以瞬時液相擴散連接(Transient liquid phase, TLP)和低溫燒結金屬連接(Low temperature joining technique, LTJT)廣受關注。

TLP 是將低熔點的中間層材料置于高熔點的母材中間,在適當的壓力下加熱到高于中間層材料熔點溫度,熔化中間層材料并與母材反應生成高熔點的金屬間化合物而實現低溫固態連接。 TLP 連接的中間層材料必須具有較低的熔點,常用的低熔點元素有Sn和In,二者的熔點分別為 231℃和 156℃,能與這兩種元素形成高熔點金屬間化合物的元素有Ag、Au、Ni。 Cu 與 Sn 之間也可形成 Cu-Sn 高熔點化合物。

綜上,TLP 連接可以實現低溫連接和高溫應用,是寬禁帶半導體器件互連的可行技術。 但是這種方法也有明顯缺點,如需要事先在連接件表面鍍覆金屬,增加了成本和工序; 連接時保溫時間較長,而且連接完成后往往還需要進行退火處理。 雖然耐溫能力比傳統焊料合金有明顯提高,但是脆性的金屬間化合物高溫可靠性仍存在隱患; 工藝控制方法略微復雜,需要避免反應不充分或者過反應。

因此,低溫燒結金屬連接技術受到更為廣泛的關注,尤其是低溫燒結納米銀連接技術,由于其高導熱、低壓/無壓力燒結、低溫燒結致密和低彈性模量等特性,已成為目前寬禁帶半導體器件封裝的首選互連材料。

近年來,針對納米銀焊膏的燒結工藝及其燒結銀接頭的性能及機械可靠性已經有了大量的研究成果。 例如,YANG 等發現,在相同的電流密度下,使用納米銀膏封裝的發光二極管(Light emitting diode, LED)比用焊料和導電銀膠封裝的LED 光輸出量大,表明其熱導率優于焊料和導電銀膠。 BAI 等利用低溫燒結納米銀對單芯片封裝和多芯片封裝進行了深入研究。 結果表明,低溫燒結連接法封裝的功率半導體模塊比傳統焊料封裝的功率半導體模塊具有更好的電學、熱學和力學性能。

雖然在大多數電子器件應用場合,燒結銀的性能已被證明具有顯著優勢。 但是以往低溫燒結需要輔助較高壓力,工藝復雜,設備要求高。 因此不少學者通過改進材料制備方法和工藝,簡化了互連工藝復雜度,降低低溫燒結工藝和設備成本。 例如,YASUDA 等在 250℃-400℃ 和輔助壓力小于 5MPa 的條件下,使用粒徑為 5-20nm 的銀作為連接材料,實現了芯片與基板的互連且剪切強度達到 20MPa 以上。 FU 等利用粒徑為 2 μm 以下的銀顆粒,在 250℃ 下首次無壓燒結實現了大尺寸芯片(≥100 mm?^2^?)與基板的連接,其剪切強度達到 40 MPa,孔隙率為 25.6%,熱導率為 263 W/m·K。

鑒于無壓燒結銀的致密度略低于大壓力燒結銀,低溫無壓燒結納米銀的性能和可靠性需要進一步驗證。 這是因為在相同的燒結工藝下,連接面積越大,相應的孔隙率越高,連接強度越低; 提高升溫速率可以促進焊膏的致密化過程,有利于晶粒的均勻化,但容易造成連接層產生缺陷,致使芯片受到熱沖擊,如果燒結溫度太高或保溫時間太長不利于銀顆粒燒結致密化過程,反而會使晶粒粗化。

為解決上述問題,LU 等率先利用電流輔助燒結技術可以在 1 s 內實現電子器件與銅基板的快速致密化互連,燒結銀層的導電率高達 3.7×10****^7 ^****S/m,比傳統熱壓燒結銀層高近兩個數量級,接頭剪切強度可達 40 MPa。 WANG 等將進一步發現在低溫環境下包覆在納米銀焊膏表面有機物的熱分解可以促使納米銀顆粒在 180℃ 下完成燒結。 隨后,ALLEN 等利用該電流輔助燒結方法在電子印刷領域開展了應用研究。 該工藝過程可在 2 μs 內使熱壓燒結接頭具有更高的抗機械疲勞性能。 CAO 等也發現在相同的加載水平下,電流輔助燒結銀接頭具有更好的循環剪切變形能力。

1.2 典型建模仿真方法

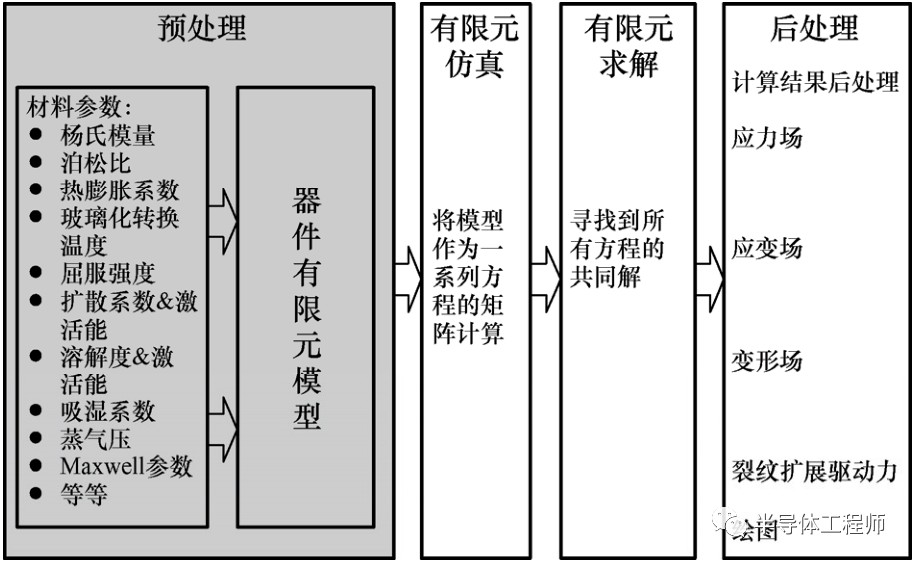

圖 1 為在電子封裝中有限元求解過程的基本流程圖,通常包括預處理、建模、求解和后處理等步驟,其中材料參數和模型對于仿真結果的準確性有重要影響。

圖 1 半導體封裝有限元建模流程圖

1.2.1 多尺度建模

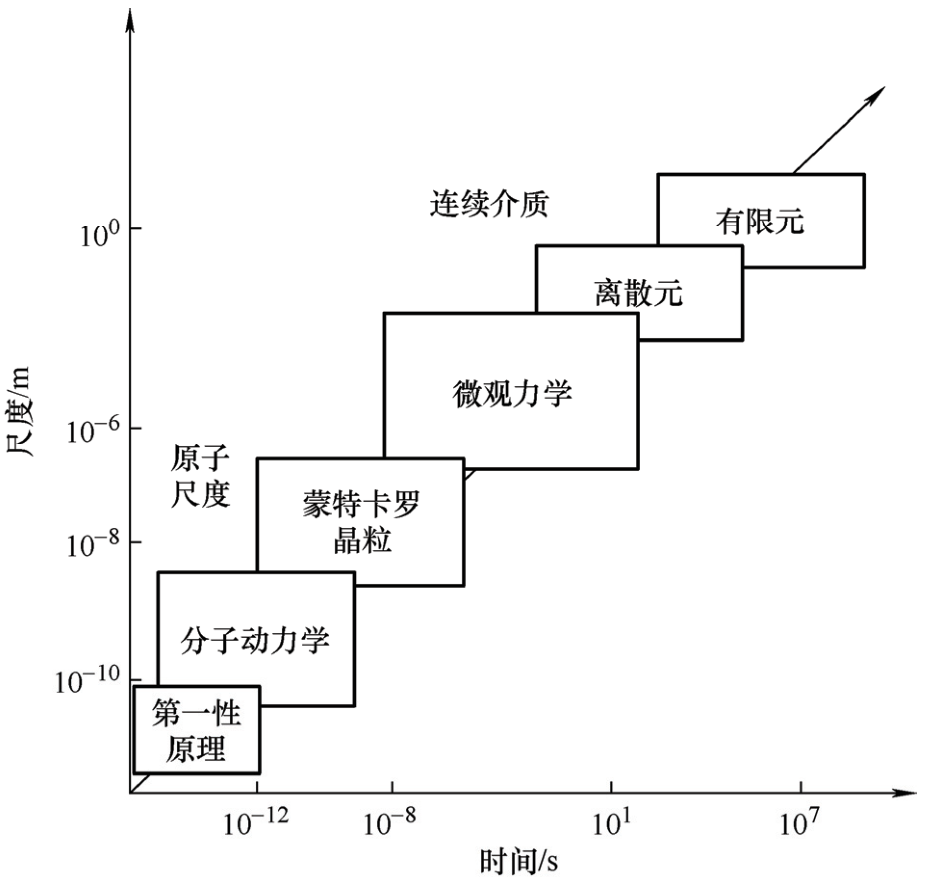

隨著封裝技術的不斷發展,封裝材料和結構研究的尺度和時間跨度可能超過 12 個數量級,并且每個級別都涉及不同的領域,如圖 2 所示。 多尺度建模的最終目標是從第一性原理開始預測材料行為,將信息傳遞到分子尺度,最終傳遞到宏觀尺度。 從“自下而上”的角度來看,多尺度方法應該考慮材料的內在屬性。 目前的大部分工作都集中于納米結構材料。

圖 2 模擬方法的尺度和時間跨度

對結構分析來說,基于連續介質的方法被用以描述或預測宏觀材料的行為,例如傳統力學和有限元方法。 分子動力學仿真主要關注具有熱力學平衡的結構,這顯然不像是數學連續體,而是一種離散的晶格結構。 因此,除非采取措施確保分析的等效性,否則對分子模型進行連續力學概念的直接應用是不恰當的。

1.2.2 多物理場的耦合分析

在電子封裝流程中,多物理場效應廣泛存在。 微機電系統(Microelectromechanical systems, MEMS)具有微米尺寸的組件,廣泛應用于商業和工業系統中,如集成硅壓力傳感器、加速度計和運動檢測器等已經在汽車和工業應用中使用了多年。 這些微小型系統(有些甚至比人類頭發更細)從應力、溫度、靜電、壓電和電磁效應中催生出它們的功能。 有兩種數值技術可用于模擬涉及的多物理場:直接耦合和順序耦合。

(1) 直接耦合分析。 直接耦合分析將所有物理場組合為一個矩陣中的有限元方程,并將矩陣作為一個整體求解。 直接耦合的一個示例是熱效應和電效應的組合,以此研究電阻或介電材料的電磁能所產生的焦耳熱大小。 在某些換能器中,電學和力學的直接耦合可以確定施加電壓引起的變形量,反之亦然。 在這些類型的分析案例中,我們就可以在單個解決方案中考慮所有物理場。

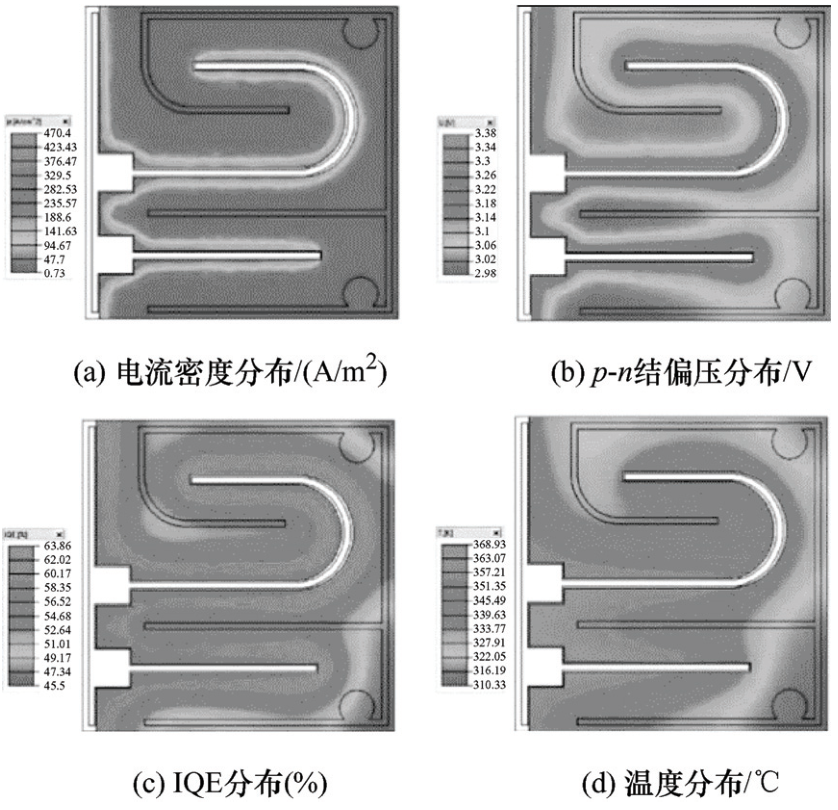

以 LED 的仿真為例。 LED 異質結構被認為是一組平面半導體層和電極。 一維模型可用于模擬 LED 能帶圖,它可以視作異質結構內的偏置電壓、電子和空穴傳輸的函數,還可以模擬提供光發射的載流子復合過程。 因此,我們可以獲得內部量子效率(Internal Quantum Efficiency, IQE)、電流密度和發射光譜與 p-n 結偏壓和溫度之間的關系,如圖 3 所示。

圖 3 LED 芯片的仿真結果,所有結果都顯示在有源層上

(2) 順序耦合。 在順序耦合中,一個場的方程被部分求解,并且結果作為載荷(一個物理場與另一個物理場相互作用的結果)傳遞到下一個物理場以驅動該場的求解。 然后分析軟件將此迭代傳遞到下一個物理場,依此類推,直到最后一個場。 在這之后順序迭代過程從頭開始直到找到最終解。

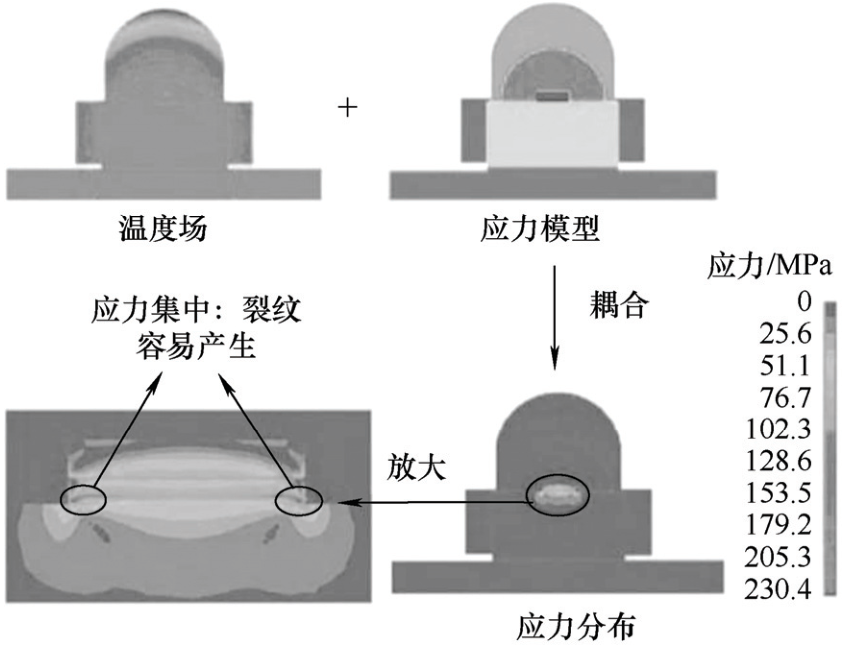

例如,在各種制造工藝、加速測試、不當的處理和應用過程中,LED器件和模塊中經常產生空隙、裂縫和分層等缺陷。 缺陷主要在制造早期形成,但是在后續的溫度、濕度、應力等不均勻載荷下逐步擴展最終失效。 如圖 4 所示,通過非線性有限元法(Finite element method,FEM)對各種情況下的缺陷進行建模,以研究界面、界面初始缺陷和熱接觸電阻、非線性應力及光學界面之間的聯系,從而分析它們對 LED 熱學及光學性能的影響。 在順序耦合場分析中,我們先計算初始溫度場,再將其傳遞給結構分析。

圖 4 大功率 LED 的熱應力分析

通常,對于多物理場分析,物理場之間的數據交換需要仔細協調,并且必須將各種場、載荷以及邊界條件的不同網格要求相關聯。 為了使所有這些功能正常運行,需要在各個場之間進行復雜的反饋循環,以便耦合分析能收斂到準確解。 一些研究表明,在產品生命周期的不同階段,解決這類問題的時間和成本相差近 10 倍。 考慮更多的物理效應可以產生更準確的分析、更少的物理原型、更短的產品開發周期、更低的開發成本以及更快的上市時間。

有些分析可能具有單向耦合。 在熱應力問題中,溫度場在結構場中產生熱應變,但結構應變一般不影響溫度分布。 因此,不需要在兩個場的解中迭代。 更多復雜情況涉及雙向耦合。 例如,在 MEMS 的壓電分析中,處理結構場和電場之間的相互作用。 在流體-結構相互作用問題中流體壓力導致結構變形,反過來結構導致流體解發生變化。 這些問題需要兩個物理領域之間的迭代才能收斂。 場之間的耦合可以通過直接或間接實現耦合。 跨場的耦合可能很復雜,因為不同場在求解器中可能涉及不同類型的分析。

電子制造中常用其他建模技術包括如下。

(1)子模型技術。 利用子建模技術,基于從一個初始的、相對粗糙的、全局的模型,研究模型中具有精細網格的局部部分。 當需要獲得一個準確的局部解,并且細化的局部區域建模對整體解的影響可以忽略不計時,子模型技術是十分有用的,可以結合使用線性和非線性過程。 子模型作為與全局分析獨立的分析運行。

(2)自適應網格技術。 自適應網格劃分是一種工具,它可以在整個分析時保持高質量的網格劃分,即使出現大變形或材料損耗,自適應網格不會改變拓撲(元素和連接)。 自適應網格重構通常用于精度控制,然而它也可用于某些情況下的扭曲控制。

(3)單元移除和重新激活。 在一般分析步驟中,從模型中刪除指定的元素。 在移走之前,要移除的區域上的力/變量被存儲作用于該區域邊界的節點上。 在移除步中,這些力被降至零; 因此,移除部分對于剩余部分是完全沒有影響的。 這些力被逐漸降低,以確保去除元素對模型平滑的影響。

1.3 失效類型及機理分析

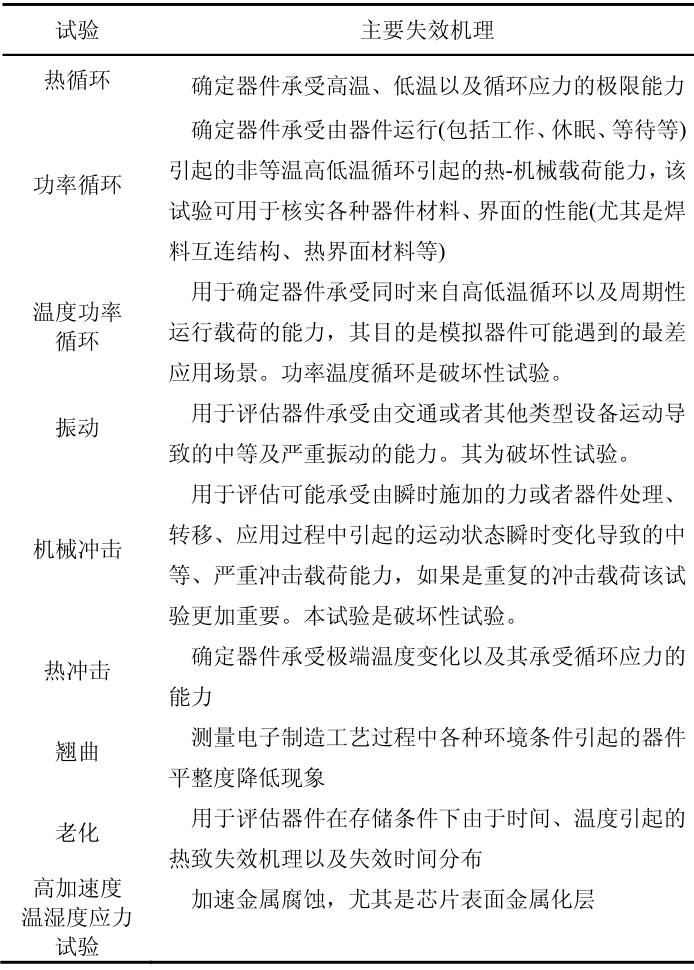

經過封裝后的電子產品需要經過嚴格的可靠性試驗,才能最終篩選出合格產品供應給產業鏈下游。 相關的可靠性試驗標準較多,通常來說,可供參考的主要標準有國軍標(GJB 548、GJB 150)、國標(GB/T 2423)、美軍標(MIL-STD-202、MIL-STD-750、MIL-STD-883)、JEDEC 標準(Joint Electron Device Engineering Council,電子器件工程聯合會)中的 JESD22 系列等。 常見的可靠性試驗見表 1。

表 1 常見的可靠性試驗

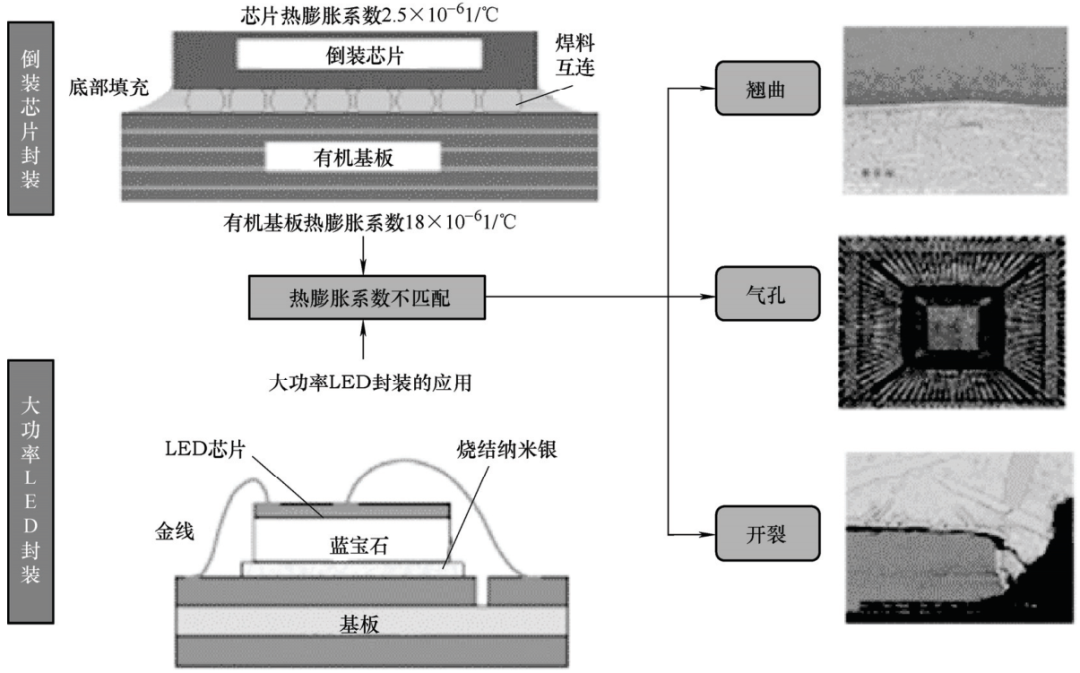

總體來說,在可靠性試驗和實際應用中,封裝互連材料的失效主要為電-熱-力致耦合失效。 其中電對互連可靠性的影響主要表現為兩方面:電流密度超過閾值導致電遷移和電致發熱引起的溫度變化(即功率循環)。 電遷移的主要原因是電流超過一定閾值后,電子風引起互連材料內部的原子定向遷移,從而導致局部電流進一步集中,從而形成正反饋,并最終導致互連結構的孔洞和斷路。 另一方面,隨著電子制造技術的進步,芯片互連材料越來越廣泛地應用于動態服役環境(即應力和應變的分布隨著時間而變化的環境)中。 而功率耗散和環境溫度的周期性變化使得電子封裝及其組件在封裝工藝或者服役過程中不斷經歷溫度循環的作用。 由于芯片、基板以及互連材料的熱膨脹系數(Coefficient of thermal expansion, CTE)不匹配,使得在互連界面處應力不為零,會導致焊層產生塑性應變的積累,使得互連焊層中的損傷不斷累積,發生翹曲、氣孔、裂紋,導致最終失效,如圖 5 所示,我們稱之為低周棘輪疲勞失效。

圖 5 器件失效機理

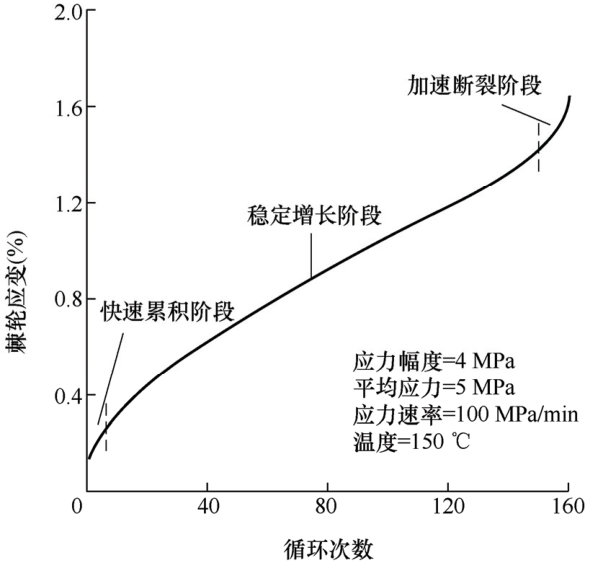

WANG 等對低溫燒結納米銀焊膏薄膜試樣的單軸棘輪失效行為進行研究。 從圖 6 可以看出,材料的低周棘輪疲勞塑性應變演化可分為三個階段:初始快速累積、穩態增長和加速斷裂。 第一階段較為短暫,在此階段棘輪應變迅速累積。 第二階段占試件循環壽命的大部分,此階段棘輪應變以一個幾乎恒定的速率累積,棘輪應變穩定增長; 進入加速斷裂階段后,棘輪應變率和棘輪應變均表現出加速增長的趨勢,試樣在很少的循環次數內就因過大的棘輪應變而導致最終破壞,此階段往往很短暫。 由于第二階段占試件循環壽命的大部分,因此應重點關注棘輪失效行為的第二階段。 第二階段的棘輪應變率也是區分棘輪失效行為和疲勞失效行為的一個重要參數。

圖 6 典型的低溫燒結納米銀焊膏膜的棘輪演化曲線

對于傳統的錫鉛焊料,劉勝率領的課題組在 20 世紀 90 年代前后做了大量的系統性的研究工作。 CHEN 等對 63Sn37Pb 也進行了相關研究,在室溫下對 63Sn37Pb 進行了系列棘輪變形試驗,得到63Sn37Pb 在不同保持時間、平均應力、應力幅值和加載歷史下的棘輪和疲勞變形行為,還采用 Anand 模型預測 63Sn37Pb 的棘輪和疲勞變形行為。 隨后對用于替代錫鉛焊料的無鉛焊料和導電膠也不可避免的需要研究其棘輪和疲勞行為。 例如,AMALU等[55]研究了倒裝芯片封裝中無鉛焊料連接半導體器件時,其高溫可靠性及黏塑性行為。

針對有機膠復合黏連材料,MA 等采用動態熱力分析儀 (Dynamic thermomechanical analysis, DMA)研究了高溫下各向異性導電膠(Anisotropic conductive film, ACF)在應力控制下的單軸棘輪行為,討論了平均應力、應力幅值、環境溫度和加載歷史對其單軸棘輪行為的影響, 發現其楊氏模量隨溫度升高而降低,棘輪應變隨平均應力、應力幅值和溫度的升高而增大,并且加載歷史也對棘輪過程有重要的影響; TAN 等研究了采用 ACF 封裝連接器件在受溫度和濕度影響時的復雜力學行為,如剪切和循環疲勞。 研究發現器件互連在斷裂前的最大剪切力達到 465.0 N,循環疲勞極限強度為 143.5 N。

雖然納米銀焊膏作為一種性能優異的新型無鉛互連材料,已受到廣泛關注。 在被廣泛應用半導體器件封裝之前,研究其棘輪失效行為和疲勞失效行為是不可或缺的。 這對指導低溫燒結銀作為芯片互連材料在高溫應用中意義重大。

目前,針對電子器件的高溫封裝應用,芯片互連材料除物理性能,如 CTE、楊氏模量等之外、疲勞、蠕變特性及其與溫度的關系則是更關鍵因素。 因此,部分學者率先研究了納米銀焊膏材料的機械可靠性。 例如,CHEN 等研究了納米銀焊膏燒結銀膜在溫度區間為?60℃到 300℃的拉伸和棘輪特性,并且討論了在 150℃下加載速率、應力幅值和平均應力對燒結銀膜的棘輪特性的影響。 WANG 等討論了棘輪—疲勞的交互影響。

部分學者還針對低溫燒結納米銀材料作為封裝互連時的可靠性進行了研究。 例如,WANG 等研究了 1.1×1.1 mm****^2^**** 芯片連接的低溫燒結納米銀焊膏的可靠性。 他們通過對低溫燒結銀封裝互連器件開展?40~150℃的溫度循環試驗,發現在經歷 900 周期溫度循環老化后,燒結納米銀互連的微觀結構未出現明顯變化,但其芯片連接強度會出現小幅下降。 李欣設計了納米銀焊膏搭接剪切試樣,并對接頭在室溫和高溫下的力學性能進行了全面的試驗和理論研究。 采用了應力或應變控制方式,對搭接接頭進行了等溫循環剪切試驗,考察了平均應力、應力幅值以及環境溫度對接頭可靠性的影響。 齊昆等則結合 LED 應用需求,研究了燒結納米銀互連 1.1×1.1 mm****^2^**** LED 芯片的循環剪切疲勞行為,獲得了其疲勞壽命曲線族。

隨著應用場景的不斷拓展,燒結納米銀被逐漸用于封裝更大面積電子芯片,因此,研究人員探索了連接面積對封裝連接可靠性的影響,發現無壓燒結過程中,相同燒結工藝下連接面積越大,相應的燒結孔隙率越高,連接強度也隨之降低,無壓燒結工藝應被局限于連接面積小于 10 ×10 mm****^2^**** 的應用。 為克服無壓燒結納米銀工藝方法的這一局限性,隨后曹云嬌等提出了燒結時間短、效率高的電流輔助燒結工藝,實現了納米銀焊膏的快速燒結,并且研究了相應的電流燒結納米銀互連焊層的力學可靠性。 通過循環剪切試驗發現,平均應力和應力幅值對電流燒結納米銀互連焊層的棘輪行為影響明顯,電流燒結納米銀互連焊層的棘輪變形水平隨平均應力和應力幅值的增加而提高,壽命相應降低。 為了更好地預測電流燒結納米銀的優異抗疲勞可靠性,CHEN 等基于 Ohno-Wang 和 Armstrong-Fedrick (OW-AF) 非線性運動硬化準則的粘塑性模型和 Anand 模型嵌入 ABAQUS 商用有限元軟件中來預測電流燒結納米銀互連焊層的棘輪行為,證明了 OW-AF 模型的預測結果的準確性優于Anand 模型。 該預測方法可用于更好的指導電子封裝針對電-熱-機械可靠性設計與增強。

2 典型電子封裝領域可靠性研究

2.1 LED 封裝可靠性研究

LED 封裝可靠性是典型的光、熱、力耦合問題,因此其評價標準圍繞光學性能、熱學性能和力學性能等方向。 在 LED 性能及可靠性中涉及各種封裝材料和工藝主要包括:光轉換材料、封裝膠、固晶材料、封裝基板。

(1) 光轉換材料。?在大功率 LED 封裝中,熒光粉材料是最常用的光轉換材料。 其按材料分可分為稀土石榴石系、硅酸鹽系、含氮化合物系和硫化物系四大系列。 其中鉛酸鹽的釔鋁石榴石(Y3Al5O12)是目前使用最廣泛的熒光粉,俗稱 YAG 熒光粉。 該熒光粉的顆粒直徑通常在 5~35 μm,具有亮度高、發射峰寬、成本低的優點,但激發波段窄,光譜中缺乏紅光的成分,顯色指數不高。 國外研究學者研究了熒光粉顆粒直徑對 LED 出光的影響,通過試驗證實,當粒徑大約為 20 μm 時,LED 的光通量最大。

通常熒光粉和封裝膠混合后涂覆,封裝膠導熱性能較差,熒光粉光轉換過程中產熱無法有效散出,導致硅膠在高溫時性能變化,甚至“碳化”。 熒光粉溫度過高將導致光學和熱學性能的變差,也會使 LED 可靠性變差,甚至高溫時會不發光,產生“熱淬滅”現象。 LED 封裝中主要應用的涂覆方法有:點膠涂覆、保形涂覆和遠離涂覆。 點膠自由涂覆由于工藝簡單、成本低,是 LED 封裝中最常用的熒光粉涂覆方法,被廣泛使用。 其直接將熒光粉膠涂覆在芯片表面,通過其自由流動成型而得到熒光粉層。 這種方法得到的熒光粉層高度遠小于寬度,從而引起封裝 LED 中間區域色溫偏高而側邊區域偏黃,即產生“黃圈”,空間顏色均勻性差。

在芯片周圍均勻涂覆熒光粉薄層即為保形涂覆,具有優良的空間顏色均勻性和光效。 目前保形涂覆工藝研究很多,如電泳法、溶液蒸發法、晶圓級旋涂法、沉降法和粉漿法、噴涂法等。 但保形涂覆工藝復雜、成本高,熒光粉層的后向散射嚴重,芯片和支架對光能吸收嚴重,降低了封裝效率,同時芯片工作過程發熱會引起的熒光粉溫度升高,熒光粉效率隨著溫度的升高呈指數下降的趨勢并且過高的熒光粉層溫度引起明顯的光學性能下降。

遠離涂覆是將熒光粉層與芯片相隔離,芯片與熒光粉層并不直接接觸。 然而,遠離涂覆往往需要采用特殊結構的 LED 封裝支架,降低后續光學設計自由度。 美國研究學者研究發現,采用遠離涂覆,顯著減小了后向散射,可將光效提高 7%。 華中科技大學羅小兵課題組設計了基于點涂法的半球薄層熒光粉遠離涂覆方法,實現 LED 封裝高空間顏色均勻性。

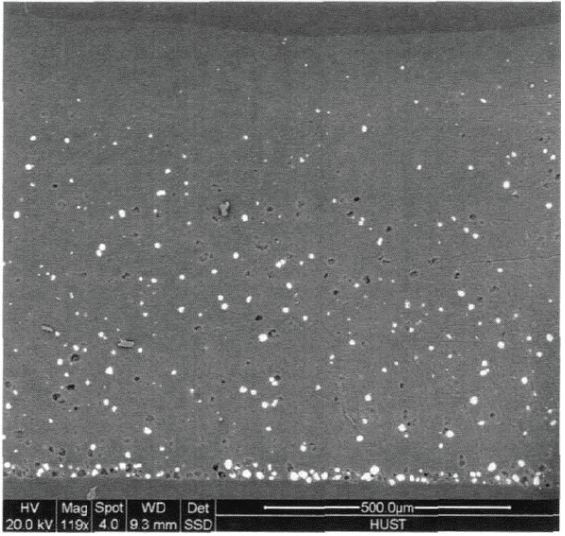

另外,在熒光粉膠中,熒光粉的密度遠遠大于硅膠密度,導致熒光粉在硅膠中會向下沉淀,分布不均勻,進而產生色溫升高、一致性變差等問題。 美國專家對其色溫漂移問題進行研究,證明熒光粉沉降會導致熒光粉層上下濃度變化,影響色溫和光通量等光學性能。 在沉降過程中,上部的濃度變化要明顯大于中間部。 芯片結構不同,熒光粉沉淀對光學性能的影響也不同。 華中科技大學羅小兵課題組通過試驗觀察證實了熒光粉沉淀,如圖 7 所示,硅膠固化后大顆粒基本停留在底層。

圖 7 熒光粉顆粒沉淀實物截面圖

近十幾年,量子點(Quantumdot,QD)材料,一種納米尺寸半導體材料,受到越來越多的企業和科研院所重視,得到了廣泛研究。 量子點是一種半導體納米顆粒,具有很強的量子限閾效果,使得連續的能帶變為分立能級,進而具有熒光效果。 相比于熒光粉,量子點的發光波長是可以隨著粒徑改變的,量子效率比較高。 因為是納米顆粒,所以光散射極低,發光半峰寬很窄,色彩飽和度很高。

由于量子點是納米級尺寸,納米顆粒較高的表面能和顆粒之間的庫侖力或范德華力使得量子點容易發生團聚。 此外,量子點表面配體常常與硅膠或環氧樹脂中基團不兼容,會導致非輻射能量轉移增大,引起量子點發光效率降低,光轉換效率下降和封裝劑難固化等不良問題。 在國內外的研究中,針對量子點團聚和與硅膠/環氧樹脂的不兼容問題,多數采用的是將量子點和與其兼容的聚合物混合制成薄膜,并通過遠離封裝的形式制備,量子點發光二極管(Quantum dot light emitting diode,QLED)。

另外,量子點在光吸收和光轉換方面具有一定閾值,當照射光強度或 LED 工作電流較大時,量子點發光性能往往呈現出“飽和效應”,具體表現為光轉換效率陣低,光通量下降,色溫升高和色坐標發生變化等。 隨著封裝密度的増加,工作功率的增加,飽和效應將更大的影響量子點在 LED 封裝的發展和應用。

(2) 封裝膠。?在 LED 封裝過程中,通常采用環氧樹脂或硅膠作為封裝膠。 但由于環氧樹脂容易出現老化變黃,嚴重影響出光效率,而硅膠具有更好的光-熱穩定性,透光率也很高,所以在封裝過程中常用硅膠作為封裝膠體。 硅膠對不同顏色的光透光率通常能達到 97%以上。 提高 LED 封裝膠折射率可有效減少芯片和封裝材料界面上的全反射,因此高折射率、高透光率的封裝材料對于提高取光效率也很重要。 目前主要產品來自美國道康寧公司,其推出的高折射率硅膠比傳統的環氧樹脂材料具有更好的光-熱穩定性,透光率也很高,因而能顯著改善 LED 的光學性能。

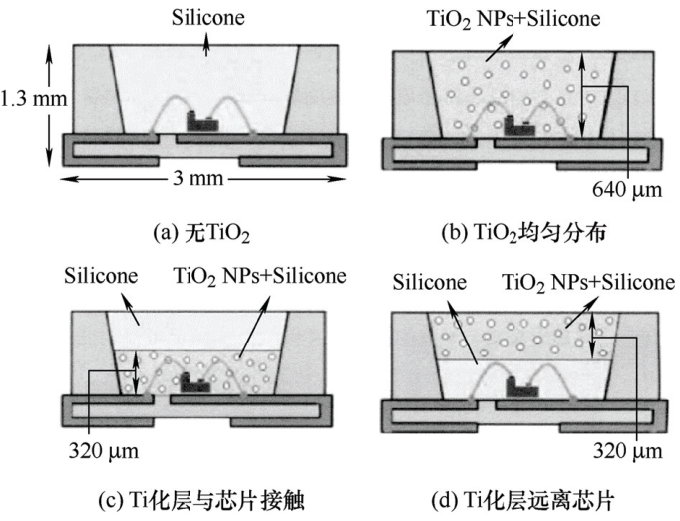

國內外學者通過開發或者改良工藝,也實現了硅膠質量的提升。 在封裝膠中摻雜高折射率的散射粒子,可以提升封裝膠的折射率,減少界面全反射,從而提升取光效率。 摻雜的粒子包括納米TiO2粒子、ZnO粒子。 WANG 等將二氧化鈦納米顆粒摻雜入硅膠中,如圖 8 所示。 結果表明將藍光 LED 芯片上硅膠分為兩層,接觸芯片的一層摻雜二氧化鈦顆粒,上層為純硅膠,在 20 mA 和 80 mA 工作電流時,可以將光通量分別提升 3%和 5%,在老化試驗中,發現光通量衰減情況得到一定程度抑制。

圖 8 納米 Ti 化摻雜硅膠的封裝結構

(3) 固晶材料。?良好的散熱對于大功率 LED 封裝至關重要,是保障 LED 能夠維持高光學性能的前提條件,是實現 LED 封裝高可靠性的重要內容。 解決 LED 封裝散熱的最主要的方法是利用高導熱的界面材料和基板材料降低芯片到外部環境的熱阻,將芯片的熱量快速傳導到外部的散熱器中。 LED 芯片產生的絕大部分熱量是通過固晶層向下傳導,因此固晶層不僅起到固定 LED 芯片的作用,而且是熱量傳遞的必經路徑,是散熱關鍵,因而需要降低固晶層熱阻。 目前采用的主流方法為采用高導熱率的固晶材料。

由于成本較低、工藝溫度較低,絕緣膠為早期應用產品; 隨著功率的增大,由于絕緣膠熱導率低,己經很少使用。 目前主流的固晶材料是導電銀膠和共晶焊料。 導電銀膠主要成份為銀粉和樹脂,具有一定的導電性,熱導率大于 2 W/m·K,但含有一定的有毒物質,比如鉛。 LED 封裝功率越來越大,固晶材料需要更高的熱導率,因此人們制造了金錫、錫銀銅等共晶焊料,將熱導率提升到 60 W/m·K 以上,而且共晶焊料已經成為目前市場上大功率 LED 主流固晶材料。 為了使得 LED 壽命延長,應用更加廣泛,大量學者將研究熱點集中于提升材料熱導率,主要為摻雜高熱導率材料,如摻雜金剛石、碳納米管、納米銀等。 國外學者將銀膠、錫銀銅焊料及加入碳納米管的焊料分別進行研究試驗,結果證實具有碳納米管的焊料熱導率更高,更能減小固晶層界面熱阻。 陳明祥老師課題組通過研究發現,當固晶材料熱導率提升時,固晶層界面熱阻降低,使得封裝總熱阻降低,可以增加 LED 的光輸出。

(4) 封裝基板。?芯片產生的熱量主要有三個導熱路徑,一是通過封裝膠向環境散熱,二是通過引線和引腳傳熱,三是通過固晶層和封裝基板向下傳熱。 其中絕大部分熱量通過固晶層和封裝基板傳導。 封裝基板的主要性能圍繞可靠性和散熱性,就需要考慮熱力學性能,因此要有高熱導率和適當的熱膨脹系數。

金屬芯印刷電路板(Metal core PCB, MCPCB)于20 世紀 60 年代在美國研發制造,其中金屬基板具有很好的散熱性能,但往往熱膨脹系數不滿足匹配性要求。 普通的 MCPCB 由于中間的絕緣層的熱導率很低,只有 2~10 W/m·K,因此,盡管基板中金屬的熱導率很高,但整體熱阻仍高達 50 K/W。 中國臺灣鉆石科技則采用類鉆碳涂層取代 MCPCB 中的有機絕緣層,大幅提高了熱導率和耐熱性。 韓國研究學者將鋁基板進行氧化試驗,使得一面產生了氧化鋁(Al2或3),從而使基板熱阻得到了有效降低。 陶瓷材料由于具有良好的絕緣性和熱導率,在制造封裝基板方面已經有了廣泛應用,其熱膨脹系數匹配性能也較好。 主要有低溫共燒陶瓷(Low temperature co-fired ceramic,LTCC)、覆銅陶瓷基板(Direct bonding copper, DBC)、直接鍍銅基板(Direct plate copper, DPC)等種類。 韓國學者通過在基板上制備銀過孔,增強了基板熱導率,同時有效減小了熱阻。 LTCC 基板在 21 世紀初由美國專家制造應用,由于結構簡單,熱界面少,大大提高了散熱性能。 美國 LORD 公司開發的 Anotherm 陽極氧化鋁基板己成功應用于大功率LED 封裝。

鋁基板與 Al2或3?陶瓷基板、AlN 陶瓷基板最大區別在于鋁基板中有一層熱導率低的絕緣層,嚴重影響了鋁基板的整體導熱性能。S.H.Shin 金屬鋁基板有選擇性地進行氧化,并在基板上面封裝微米級的功率型單片微波集成電路芯片(Monolithic microwave integrated circuit, MMIC),不僅具有良好的導熱性能,而且還降低了封裝成本,簡化了基板制造工藝。金屬基復合材料 (Metal matrix composite, MMC)基板具有更好的熱膨脹系數匹配性能。國外學者通過試驗制造了在 LED 封裝中可實用的 Al-SiC 復合基板,熱導率得到提升的同時,熱膨脹系數也可以調節。Al-SiC 熱膨脹系數與芯片相近,強度和硬度都超過了銅和鋁,但離大規模的產業化應用仍有一段距離。

硅材料熱導率更高,力學性能更好,中國臺灣的 LED 產品中己經將 DPC 工藝技術應用到了硅基板制備中。香港科技大學的研究學者通過刻蝕出硅通孔,提升了硅基板的散熱性能,同時與熒光粉涂覆工藝相結合,使得 LED 熱性能得到提升。

2.2 功率電子封裝可靠性研究

功率模塊用于電力控制,對高效的能量轉換起著關鍵作用。近年來,利用寬帶隙半導體(如 SiC 和 GaN)的功率電子模塊得到了關注與發展,其工作溫度預計在 200℃以上,功率模塊封裝在 200℃以上的高溫熱—機械疲勞老化挑戰極其嚴峻。因此,研究高可靠性、長壽命的功率模塊非常必要。

對功率器件的研究從 20 世紀 90 年代就開始了,功率模塊結構完整性研究主要集中在功率器件的狀態監測和剩余壽命估計。目前基于計算機輔助工程 (Computer aided engineering, CAE)的應力分析、斷裂力學和材料強度分析已被廣泛應用于確保功率電子器件封裝結構完整性。

例如,以往功率器件封裝的結構完整性的關鍵是芯片和鍵合線之間的連接(線鍵合位置)以及芯片和銅基板之間通過封裝互連材料實現連接。在功率模塊工作時,這些封裝互連受到周期性的溫度變化作用,由于功率模塊的封裝材料間 CTE 不匹配,從而導致其承受顯著的循環熱應力,極易導致熱-機械疲勞現象。熱-機械疲勞可能導致模塊封裝引線斷裂和封裝互連的裂紋產生與擴展。亟須發展功率電子模塊中鍵合引線和連接層的熱-機械疲勞壽命的估算方法,實現功率電子器件的封裝結構完整性設計。這就要求我們掌握失效原因,并開發準確的壽命預測方法。

近些年來,研究人員提出了一些基于溫度范圍的引線壽命預測模型。它們包含引線脫落壽命公式和連接層開裂壽命預測模型。但是該模型為了擬合試驗數據,需要確定與物理量有關的常數,而鑒于功率模塊復雜的工況,使得這種方法的模型使用僅限于某一功率模塊,不同的模塊和工況需要進行新的參數擬合和修正。隨后有學者就提出了基于非彈性應變范圍Δεin?的引線脫落和連接層裂紋的壽命預測模型,以及非線性斷裂力學參數 J 型積分范圍 ΔJ 和非線性斷裂力學參數 T型積分范圍 ΔT?的壽命預測模型。由于它們均是直接影響熱疲勞的物理參量,因此均比基于溫度范圍 ΔT 的壽命預測模型更簡單。

除壽命預測理論模型外,針對功率器件的封裝壽命預測還需要注意:①由于引線鍵合的焊點尺寸非常小,針對引線鍵合的壽命預測中,其裂紋擴展壽命常常忽略不計,但對于功率模塊的連接層十分必要考慮裂紋擴展的壽命。可以考慮采用基于 Paris 定律給出的疲勞裂紋擴展速率來準確預測連接層的開裂行為;②以 ANSYS 等為代表的商用有限元軟件目前不提供標準的基于連續損傷力學和共聚力模型的壽命預測方法函數調用,因此,急切需要在商業有限元軟件中增添這些方法函數或開發新的專用有限元軟件;③機械載荷試驗應更多的用于獲得 Coffin-Manson 定律型的疲勞特性以及 Paris 定律型的疲勞裂紋擴展特性,而不是耗時且不精確的熱循環試驗和功率循環試驗。這是因為在功率循環試驗中,由于從 VCE?獲得的溫度是半導體芯片的平均溫度,而不是失效位置的局部溫度,因此使用基于通過集電極-發射極電壓 VCE?評估的溫度范圍 ΔT 的故障模型不適合評估局部故障的壽命,而其局部溫度才是影響功率電子模塊中鍵合引線脫落失效的關鍵因素。

2.3 微電子芯片封裝可靠性研究

微電子封裝產品在生產制造、應用使用和存貯運輸過程中所承受的外在環境因素(如濕氣、溫度、振動、粉塵等)都會對影響到封裝產品的可靠性,使其遭受各種物理或化學的失效形式,主要失效機理包括:翹曲變形、剝離分層、疲勞斷裂、磨損腐蝕等。其中封裝中的濕氣問題一直是困擾電子封裝行業的難題之一,劉勝團隊最早開始針對封裝中的界面問題開展研究,LIU 等在 1995 年即開始界面濕氣問題的測試和建模。

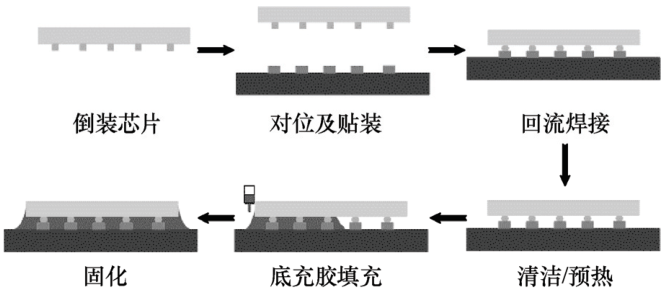

(1) 倒裝芯片封裝可靠性。?倒裝芯片(Flip-chip, FC)封裝技術最早是由 IBM 公司引入,具體的工藝步驟如圖 9 所示。當時,主要的設計目是為了克服手工引線鍵合成本高、可靠性差和生產效率低的缺點。目前,在計算機、通信等領域,倒裝芯片封裝技術已經獲得了相當程度的應用,并且呈高速增長的趨勢。

圖 9 倒裝芯片封裝工藝步驟

盡管倒裝芯片封裝有很多優點(如互連引線短、封裝密度高),但倒裝芯片封裝還有很多可靠性方面的問題待解決,如多種材料和多界面的存在使其更脆弱(界面分層、裂紋擴展等)、無鉛焊料的使用使其回流焊所需溫度更高而更易導致應力/應變集中以及無鉛焊料本構模型的選擇和壽命評估等。導致倒裝芯片封裝結構出現可靠性問題的其中一個主要原因就是:芯片與基板的 CTE 的失配(芯片:2.5~3 ppm/K,Al2O3?陶瓷基板:5~6 ppm/K,FR4 電路板:16~20 ppm/K )。1987 年,Nakano 提出,將環氧樹脂中摻入 SiO2?顆粒制成的底充膠,填充在芯片與基板之間的空隙,能夠使芯片與基板間的熱失配得到一定程度的緩解,而且可以大幅度提高焊點的熱疲勞壽命(能提高 10~100 倍)。TSUKADA 等使用有機材料印刷電路板作為基板,然后用環氧樹脂填充芯片與基板間的間隙,結果顯示其性能可以與昂貴的陶瓷基板相媲美。有分析計算指出,焊點間隙充膠后,焊點主要應力比沒有充膠時要減小 75% 到 90%。

底部填充膠的使用對倒裝芯片封裝可靠性的提高是顯而易見的,但是底部填充膠引入的同時又出現了另一個可靠性問題。在很多倒裝芯片封裝熱循環測試過程中,芯片和底部填充膠界面間往往會發生分層,這對倒裝芯片封裝的可靠性有著巨大的影響。而且有文獻已經指出,底部填充膠與芯片間的界面分層成為倒裝芯片封裝主要失效模式之一。所以,隨著倒裝焊技術的快速廣泛應用,對不同界面分層的萌生及其擴展行為進行深入的研究是有必要的。

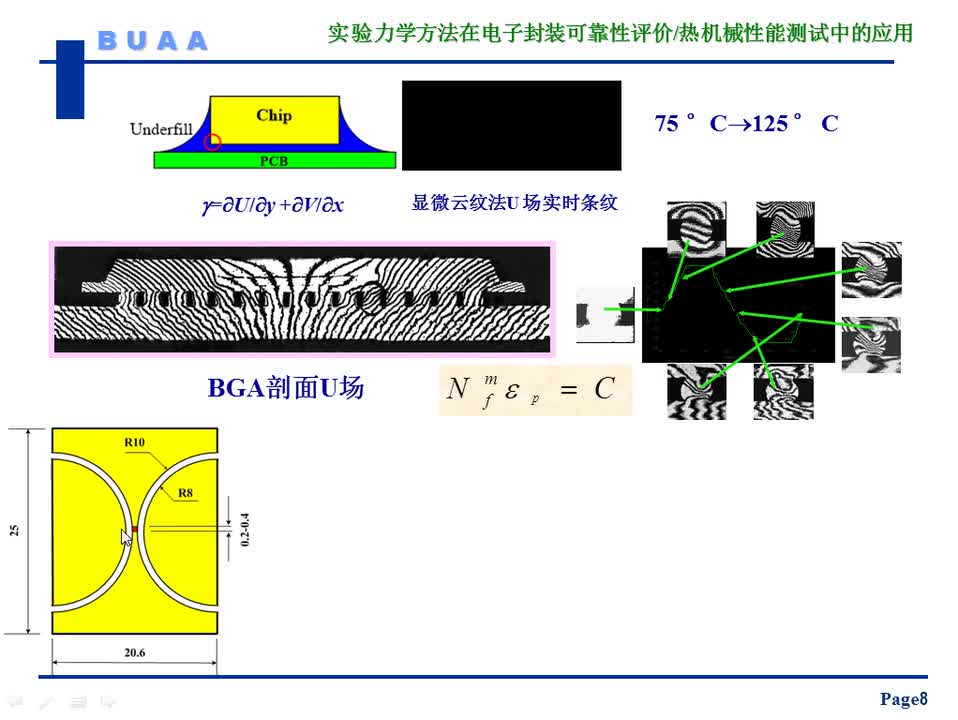

多層結構和多個界面是倒裝芯片封裝乃至高密度封裝中普遍存在的現象。界面分層失效得到越來越多的重視并逐漸成為整個產品性能和可靠性方面關心的重要問題之一。劉勝課題組通過三點彎曲試驗,測定了倒裝芯片封裝中底部填充膠和芯片界面間的斷裂韌度和相對應的相角,并將高溫摩爾紋測試和有限單元法相結合,找到了一種評估電子封裝界面分層長度的新方法。1998 年,TSUKADA 等利用光學傳感器試驗測得熱循環加載條件下膠/金屬片界面間的熱疲勞分層擴展速率。2000 年,LAU 等利用有限元模擬仿真技術,進一步研究了倒裝芯片封裝中的典型界面分層裂紋的傳播方式。芯片與底部填充膠界面間分層擴展機理仍值得做進一步研究。

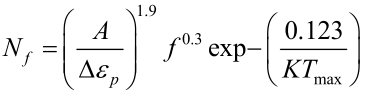

有文獻表明,在電子封裝所有可能的失效式中,焊點失效是其中的一個主要原因,所以焊點的可靠性在整個電子封裝可靠性中都占有重要地位。目前,焊點壽命預測模型多種多樣,按照焊點變形機制和失效模式的不同,大致可分為四類:基于塑性應變的模型、基于蠕變的模型、基于能量的模型以及基于斷裂參量的模型。由于便捷性、易操作性和合理性,以基于塑性變形的 Coffin-Manson 公式為代表的壽命預測模型被廣泛使用;之后,Norris 和 Landzberg 用熱循環加載頻率因子 f 和最大溫度因子Tmax?對傳統的 Coffin-Manson 方程進行了修正,得到了焊點壽命預測的經驗模型

對于這四種壽命預測模型,到底哪一種模型能更準確地對焊點壽命予以預測,目前為止業內還沒有達成一致。因此,針對倒裝芯片封裝,找到一種能夠相對準確預測焊點壽命的模型并揭示電子器件正常工作時焊點的變形機制是十分有意義的。

對于倒裝芯片封裝,在底部填充膠填充工藝中,難免會引入雜質或者在芯片與焊點連接的角點處難免出現未填滿(空洞)的現象,這會對焊點壽命產生巨大影響,如劉勝的文章指出,空洞的產生會使錫鉛焊點的疲勞壽命降低 20%左右。同時,失穩擴展至焊點的芯片/底部填充膠界面分層裂紋對無鉛焊點疲勞壽命的影響,以及界面分層和空洞對無鉛焊點壽命的影響大小比較都還有待做進一步研究。

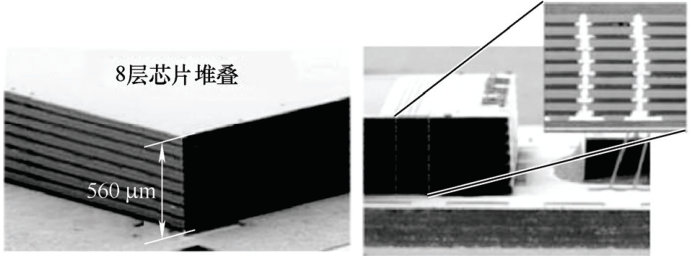

(2) 硅通孔可靠性。?隨著電子封裝更高密度、更大集成度的要求的出現,系統級集成封裝便應運而生,三維異質集成可以將電子、流體、光學等器件集成在一個模塊里,以滿足其多功能性。但集成封裝技術仍帶來一些信號延遲、噪聲等問題。利用硅通孔(Through silicon via, TSV)技術實現芯片的三維堆疊,可以避免由于引線鍵合帶來的一系列問題。同時,通過芯片與基板之間的中介層,可以實現三維系統級封裝。硅通孔三維封裝技術通過在芯片之間制作垂直通孔,實現不同芯片的信號傳遞,大大改善了芯片的轉化速度;減小信號傳輸過程中的寄生損失,能夠實現更低功耗和更短的互連長度,滿足電子器件的多功能和小型化要求。如圖 10 為所示為 8 層三維閃存芯片堆疊封裝結構。

圖 10 基于硅通孔技術的芯片三維堆疊封裝

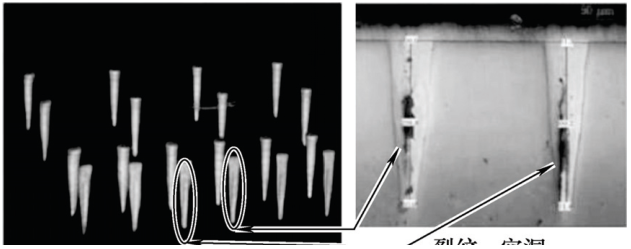

由于硅通孔需要特殊的制造工藝和結構,隨之而來也有一系列可靠性問題。比如硅片的減薄技術也尚未完全成熟。在對硅片進行刻蝕通孔之后填充金屬,孔的深寬比直接影響著電鍍效果,高深寬比會帶來一些制造缺陷,如果深孔電鍍的工藝參數選擇不當,就會導致電鍍后的銅柱中存在缺陷。如圖 11 所示,硅通孔電鍍銅柱的 X 射線圖和截面光學圖中顯示銅柱存在一些裂紋,也有部分空洞散落其中。這些缺陷會對硅通孔的長期可靠性產生直接影響,最終導致硅通孔的性能不能滿足工作要求。也有一些工藝過程中導致界面剝離缺陷等,將影響硅通孔結構以及三維封裝整體的可靠性。

圖 11 TSV 深孔電鍍的工藝缺陷

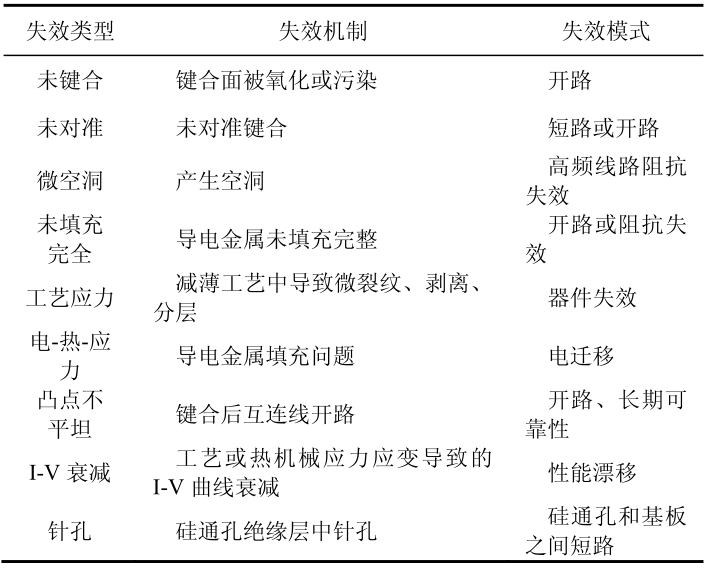

不僅制作工藝過程中會有一些不利因素,當半導體器件暴露在一定的高溫環境下,材料的熱失配現象出現,引起熱應力分布不均,也影響器件工作的穩定性。在器件工作階段中,過高的溫度差也會引發嚴重的封裝器件可靠性問題。目前,基于三維封裝分析以及可靠性試驗等仍處于不斷摸索的研究階段,相關的可靠性加速試驗方法和可靠性標準尚未完全建立起來。常見的失效模式和失效機制如表 2 所示。而失效機制和模式與硅通孔的制作工藝過程也密切相關。在制作 TSV 工藝過程中,如果出現操作不當,則會導致填充金屬銅中出現空洞,且在熱膨脹系數失配引起的熱應力作用下,分層現象很容易出現,甚至會在不同材料的界面上出現裂紋等缺陷,而這些缺陷會影響封裝的長期可靠性。

表 2 硅通孔可能出現的失效模式和失效機制

**3 **展望

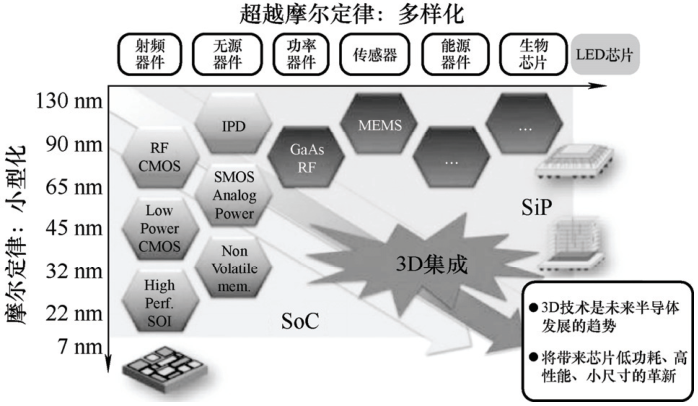

隨著市場對電子器件更強功能和更小尺寸的不斷追求,未來電子制造技術將主要朝著兩個方向發展,如圖 12 所示。

圖 12 電子封裝技術未來發展趨勢(修改自 ITRS 路線圖)

(1) 深度摩爾定律(More Moore)。?在這一技術路線上,電子制造技術將延續 CMOS 器件小型化的發展方向,通過器件結構、溝道材料、互連引線、高介質金屬柵、光刻工藝等各方面持續發展,以延續摩爾定律繼續發展。但是,隨著特征尺寸的不斷下降,柵極氧化層的厚度逼近原子尺度,器件級的量子效應也愈發明顯,漏電更加嚴重,導致晶體管的特性更加難以控制。因此,業界普遍認為摩爾定律正在接近物理極限,制造工藝進步的代價也越來越高。

(2) 超越摩爾定律(More than Moore)。?超越摩爾定律則更加強調功能的多樣化,是由應用需求驅動的。深度摩爾定律(More Moore)主要滿足了用戶對于計算和存儲的需求。而超越摩爾定律則更加注重功能的多樣化和集成化,如射頻電路、MEMS 傳感器、電源管理等功能。因此,超越摩爾定律主要有以下內涵:①隨著時代的發展,芯片價值的提升除了傳統的更高性能以外,新的功能更加重要。用戶除了傳統的計算和存儲需求,還有傳輸、參數感知、智能化等,以滿足對物聯網、生物醫療電子等多方面的需求;②芯片集成度的提高也可以通過封裝技術來實現,而不一定需要通過同一種先進制程把更多的模塊集成到統一芯片上。如模擬/射頻/混合信號等模塊并不需要最先進的芯片制程工藝,可通過更加成熟的工藝實現最佳性能。而數字模塊則可以應用先進工藝。

不同工藝路線制造的模塊通過封裝技術集成到一起,同樣可以實現強大的綜合性能和優異的集成度,這種集成方式即異質集成。異質集成技術目前已逐漸成為工業界和學術界的重點發展方向之一。同時其潛在的失效機理和模式也更加復雜,呈現出多尺度、多積累復合失效的特征。為應對這一問題,發展電子器件、模塊、系統的在線監測技術顯得更加重要。同時,在器件可靠性設計優化過程中,跨階段協作的、復合場可靠性預測及試驗分析也是電子器件未來發展的重要方向。

來源:?半導體在線

作者:?陳志文、梅云輝、劉勝等

審核編輯:湯梓紅

電子發燒友App

電子發燒友App

評論