半導(dǎo)體制造的工藝過(guò)程由晶圓制造(Wafer Fabr ication)、晶圓測(cè)試(wafer Probe/Sorting)、芯片封裝(Assemble)、測(cè)試(Test)以及后期的成品(Finish Goods)入庫(kù)所組成。 ?

半導(dǎo)體器件制作工藝分為前道和后道工序,晶圓制造和測(cè)試被稱為前道(Front End)工序,而芯片的封裝、測(cè)試及成品入庫(kù)則被稱為后道(Back End)工序,前道和后道一般在不同的工廠分開(kāi)處理。

前道工序是從整塊硅圓片入手經(jīng)多次重復(fù)的制膜、氧化、擴(kuò)散,包括照相制版和光刻等工序,制成三極管、集成電路等半導(dǎo)體元件及電極等,開(kāi)發(fā)材料的電子功能,以實(shí)現(xiàn)所要求的元器件特性。

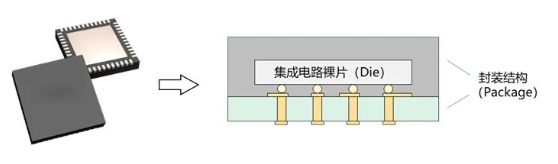

后道工序是從由硅圓片分切好的一個(gè)一個(gè)的芯片入手,進(jìn)行裝片、固定、鍵合聯(lián)接、塑料灌封、引出接線端子、按印檢查等工序,完成作為器件、部件的封裝體,以確保元器件的可靠性,并便于與外電路聯(lián)接。

一、半導(dǎo)體制造工藝和流程

晶圓制造

晶圓制造主要是在晶圓上制作電路與鑲嵌電子元件(如電晶體、電容、邏輯閘等),是所需技術(shù)最復(fù)雜且資金投入最多的過(guò)程。以微處理器為例,其所需處理步驟可達(dá)數(shù)百道,而且所需加工機(jī)器先進(jìn)且昂貴。雖然詳細(xì)的處理程序是隨著產(chǎn)品種類和使用技術(shù)的變化而不斷變化,但其基本處理步驟通常是晶圓先經(jīng)過(guò)適當(dāng)?shù)那逑粗螅又M(jìn)行氧化及沉積處理,最后進(jìn)行微影、蝕刻及離子植入等反復(fù)步驟,最終完成晶圓上電路的加工與制作。

晶圓測(cè)試

晶圓經(jīng)過(guò)劃片工藝后,表面上會(huì)形成一道一道小格,每個(gè)小格就是一個(gè)晶片或晶粒(Die),即一個(gè)獨(dú)立的集成電路。在一般情況下,一個(gè)晶圓上制作的晶片具有相同的規(guī)格,但是也有可能在同一個(gè)晶圓上制作規(guī)格等級(jí)不同的晶片。晶圓測(cè)試要完成兩個(gè)工作:一是對(duì)每一個(gè)晶片進(jìn)行驗(yàn)收測(cè)試,通過(guò)針測(cè)儀器(Probe)檢測(cè)每個(gè)晶片是否合格,不合格的晶片會(huì)被標(biāo)上記號(hào),以便在切割晶圓的時(shí)候?qū)⒉缓细窬Y選出來(lái);二是對(duì)每個(gè)晶片進(jìn)行電氣特性(如功率等)檢測(cè)和分組,并作相應(yīng)的區(qū)分標(biāo)記。

芯片封裝

首先,將切割好的晶片用膠水貼裝到框架襯墊(Substrate)上;其次,利用超細(xì)的金屬導(dǎo)線或者導(dǎo)電性樹(shù)脂將晶片的接合焊盤(pán)連接到框架襯墊的引腳,使晶片與外部電路相連,構(gòu)成特定規(guī)格的集成電路芯片(Bin);最后對(duì)獨(dú)立的芯片用塑料外殼加以封裝保護(hù),以保護(hù)芯片元件免受外力損壞。塑封之后,還要進(jìn)行一系列操作,如后固化(Post Mold Cure)、切筋(Trim)、成型(Form)和電鍍(Plating)等工藝。

封裝好的芯片成功經(jīng)過(guò)烤機(jī)(Burn In)后需要進(jìn)行深度測(cè)試,測(cè)試包括初始測(cè)試(Initial Test)和最后測(cè)試(Final Test)。初始測(cè)試就是把封裝好的芯片放在各種環(huán)境下測(cè)試其電氣特性(如運(yùn)行速度、功耗、頻率等),挑選出失效的芯片,把正常工作的芯片按照電氣特性分為不同的級(jí)別。最后測(cè)試是對(duì)初始測(cè)試后的芯片進(jìn)行級(jí)別之間的轉(zhuǎn)換等操作。

成品入庫(kù)

測(cè)試好的芯片經(jīng)過(guò)半成品倉(cāng)庫(kù)后進(jìn)入最后的終加工,包括激光印字、出廠質(zhì)檢、成品封裝等,最后入庫(kù)。

二、封裝的基本定義和內(nèi)涵

封裝(packaging,PKG):主要是在半導(dǎo)體制造的后道工程中完成的。即利用膜技術(shù)及微細(xì)連接技術(shù),將半導(dǎo)體元器件及其他構(gòu)成要素在框架或基板上布置、固定及連接,引出接線端子,并通過(guò)塑性絕緣介質(zhì)灌封固定,構(gòu)成整體主體結(jié)構(gòu)的工藝。

封裝工程:是封裝與實(shí)裝工程及基板技術(shù)的總和。即將半導(dǎo)體、電子元器件所具有的電子的、物理的功能,轉(zhuǎn)變?yōu)檫m用于機(jī)器或系統(tǒng)的形式,并使之為人類社會(huì)服務(wù)的科學(xué)技術(shù),統(tǒng)稱為電子封裝工程。

封裝一詞用于電子工程的歷史并不長(zhǎng)。在真空電子管時(shí)代,將電子管等器件安裝在管座上構(gòu)成電路設(shè)備一般稱為組裝或裝配,當(dāng)時(shí)還沒(méi)有封裝這一概念。自從三極管、IC等半導(dǎo)體元件的出現(xiàn),改變了電子工程的歷史。一方面,這些半導(dǎo)體元件細(xì)小柔嫩;另一方面,其性能又高,而且多功能、多規(guī)格。為了充分發(fā)揮其功能,需要補(bǔ)強(qiáng)、密封、擴(kuò)大,以便與外電路實(shí)現(xiàn)可靠地電氣聯(lián)接,并得到有效地機(jī)械支撐、絕緣、信號(hào)傳輸?shù)确矫娴谋Wo(hù)作用。“封裝”的概念正是在此基礎(chǔ)上出現(xiàn)的。

封裝的功能

封裝最基本的功能是保護(hù)電路芯片免受周?chē)h(huán)境的影響(包括物理、化學(xué)的影響)。所以,在最初的微電子封裝中,是用金屬罐(Metal Can)作為外殼,用與外界完全隔離的、氣密的方法,來(lái)保護(hù)脆弱的電子元件。但是,隨著集成電路技術(shù)的發(fā)展,尤其是芯片鈍化層技術(shù)的不斷改進(jìn),封裝的功能也在慢慢異化。

一般來(lái)說(shuō)顧客所需要的并不是芯片,而是由芯片和PKG構(gòu)成的半導(dǎo)體器件。PKG是半導(dǎo)體器件的外緣,是芯片與實(shí)裝基板間的界面。因此無(wú)論P(yáng)KG的形式如何,封裝最主要的功能應(yīng)是芯片電氣特性的保持功能。

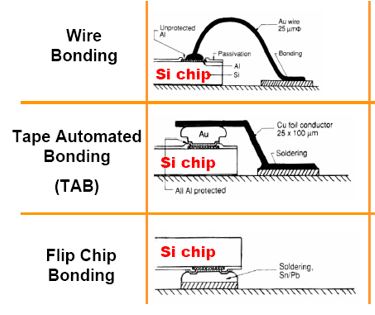

通常認(rèn)為,半導(dǎo)體封裝主要有電氣特性的保持、芯片保護(hù)、應(yīng)力緩和及尺寸調(diào)整配合四大功能,它的作用是實(shí)現(xiàn)和保持從集成電路器件到系統(tǒng)之間的連接,包括電學(xué)連接和物理連接。目前,集成電路芯片的I/0線越來(lái)越多,它們的電源供應(yīng)和信號(hào)傳送都是要通過(guò)封裝來(lái)實(shí)現(xiàn)與系統(tǒng)的連接。芯片的速度越來(lái)越快,功率也越來(lái)越大,使得芯片的散熱問(wèn)題日趨嚴(yán)重,由于芯片鈍化層質(zhì)量的提高,封裝用以保護(hù)電路功能的作用其重要性正在下降。

芯片電氣特性的保持功能

通過(guò)PKG的進(jìn)步,滿足不斷發(fā)展的高性能、小型化、高頻化等方面的要求,確保其功能性。

芯片保護(hù)功能

PKG的芯片保護(hù)功能很直觀,保護(hù)芯片表面以及連接引線等,使在電氣或物理等方面相當(dāng)柔嫩的芯片免受外力損害及外部環(huán)境的影響。保證可靠性。

應(yīng)力緩和功能

由于熱等外部環(huán)境的影響或者芯片自身發(fā)熱等都會(huì)產(chǎn)生應(yīng)力,PKG緩解應(yīng)力,防止發(fā)生損壞失效,保證可靠性。

尺寸調(diào)整配合(間距變化)功能

由芯片的微細(xì)引線間距調(diào)整到實(shí)裝基板的尺寸間距,從而便于實(shí)裝操作。例如,從亞微米(目前已小于 0.13μm)為特征尺寸的芯片到以10μm為單位的芯片電極凸點(diǎn),再到以100μm為單位的外部引線端子,最后到以mm為單位的實(shí)裝基板,都是通過(guò)PKG來(lái)實(shí)現(xiàn)的。在這里PKG起著由小到大、由難到易、由復(fù)雜到簡(jiǎn)單的變換作用。從而可使操作費(fèi)用及資材費(fèi)用降低,而且提高工作效率和可靠性。保證實(shí)用性或通用性。

三、封裝的范圍

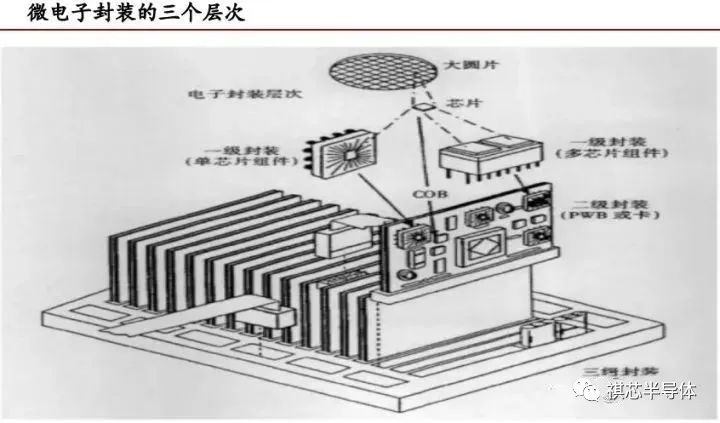

微電子封裝的三個(gè)層次

通常,從FAB廠制造的晶圓開(kāi)始,可以將電子封裝,按照制造的時(shí)間先后順序分為三個(gè)層次。

微電子封裝的三個(gè)層次

一級(jí)封裝

一級(jí)封裝是用封裝外殼將芯片封裝成單芯片組件(SCM)和多芯片組件(MCM)。半導(dǎo)體芯片和封裝體的電學(xué)互聯(lián),通常有三種實(shí)現(xiàn)途徑,引線鍵合(WB)、載帶自動(dòng)焊(TAB)和倒裝焊(Flip Chip),一級(jí)封裝的可以使用金屬、陶瓷,塑料(聚合物)等包封材料。封裝工藝設(shè)計(jì)需要考慮到單芯片或者多芯片之間的布線,與PCB節(jié)距的匹配,封裝體的散熱情況等。

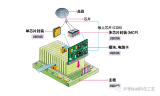

二級(jí)封裝

二級(jí)封裝是印刷電路板的封裝和裝配,將一級(jí)封裝的元器件組裝到印刷電路板(PCB)上,包括板上封裝單元和器件的互連,包括阻抗的控制、連線的精細(xì)程度和低介電常數(shù)材料的應(yīng)用。除了特別要求外,這一級(jí)封裝一般不單獨(dú)加封裝體,具體產(chǎn)品如計(jì)算機(jī)的顯卡,PCI數(shù)據(jù)采集卡等都屬于這一級(jí)封裝。如果這一級(jí)封裝能實(shí)現(xiàn)某些完整的功能,需要將其安裝在同一的殼體中,例如Ni公司的USB數(shù)據(jù)采集卡,創(chuàng)新的外置USB聲卡等。

三級(jí)封裝

三級(jí)封裝是將二級(jí)封裝的組件插到同一塊母板上,也就是關(guān)于插件接口、主板及組件的互連。這一級(jí)封裝可以實(shí)現(xiàn)密度更高,功能更全組裝,通常是一種立體組裝技術(shù)。例如一臺(tái)PC的主機(jī),一個(gè)NI公司的PXI數(shù)據(jù)采集系統(tǒng),汽車(chē)的GPS導(dǎo)航儀,這些都屬于三級(jí)微電子封裝的產(chǎn)品。

四:微電子封裝工程和電子基板

微電子封裝是一個(gè)復(fù)雜的系統(tǒng)工程,類型多、范圍廣,涉及各種各樣材料和工藝。可按幾何維數(shù)將電子封裝分解為簡(jiǎn)單的“點(diǎn)、線、面、體、塊、板”等。

電子基板是半導(dǎo)體芯片封裝的載體,搭載電子元器件的支撐,構(gòu)成電子電路的基盤(pán),按其結(jié)構(gòu)可分為普通基板、印制電路板、模塊基板等幾大類。其中PCB在原有雙面板、多層板的基礎(chǔ)上,近年來(lái)又出現(xiàn)積層(build-up)多層板。模塊基板是指新興發(fā)展起來(lái)的可以搭載在PCB之上,以BGA、CSP、TAB、MCM為代表的封裝基板(Package Substrate,簡(jiǎn)稱PKG基板)。小到芯片、電子元器件,大到電路系統(tǒng)、電子設(shè)備整機(jī),都離不開(kāi)電子基板。近年來(lái)在電子基板中,高密度多層基板所占比例越來(lái)越大。

微電子封裝所涉及的各個(gè)方面幾乎都是在基板上進(jìn)行或與基板相關(guān)。在電子封裝工程所涉及的四大基礎(chǔ)技術(shù),即薄厚膜技術(shù)、微互連技術(shù)、基板技術(shù)、封接與封裝技術(shù)中,基板技術(shù)處于關(guān)鍵與核心地位。隨著新型高密度封裝形式的出現(xiàn),電子封裝的許多功能,如電氣連接,物理保護(hù),應(yīng)力緩和,散熱防潮,尺寸過(guò)渡,規(guī)格化、標(biāo)準(zhǔn)化等,正逐漸部分或全部的由封裝基板來(lái)承擔(dān)。

微電子封裝的范圍涉及從半導(dǎo)體芯片到整機(jī),在這些系統(tǒng)中,生產(chǎn)電子設(shè)備包括6個(gè)層次,也即裝配的6個(gè)階段。我們從電子封裝工程的角度,按習(xí)慣一般稱層次1為零級(jí)封裝;層次2為一級(jí)封裝;層次3為二級(jí)封裝;層次4、5、6為三級(jí)封裝。

電子封裝的工程的六個(gè)階段

層次1(裸芯片)

它是特指半導(dǎo)體集成電路元件(IC芯片)的封裝,芯片由半導(dǎo)體廠商生產(chǎn),分為兩類,一類是系列標(biāo)準(zhǔn)芯片,另一類是針對(duì)系統(tǒng)用戶特殊要求的專用芯片,即未加封裝的裸芯片(電極的制作、引線的連接等均在硅片之上完成)。

層次2(封裝后的芯片即集成塊)

分為單芯片封裝和多芯片封裝兩大類。前者是對(duì)單個(gè)裸芯片進(jìn)行封裝,后者是將多個(gè)裸芯片裝載在多層基板(陶瓷或有機(jī))上進(jìn)行氣密性封裝構(gòu)成MCM。

層次3(板或卡)

它是指構(gòu)成板或卡的裝配工序。將多個(gè)完成層次2的單芯片封裝和MCM,實(shí)裝在PCB板等多層基板上,基板周邊設(shè)有插接端子,用于與母板及其它板或卡的電氣連接。

層次4(單元組件)

將多個(gè)完成層次3的板或卡,通過(guò)其上的插接端子搭載在稱為母板的大型PCB板上,構(gòu)成單元組件。

層次5(框架件)

它是將多個(gè)單元構(gòu)成(框)架,單元與單元之間用布線或電纜相連接。

層次6(總裝、整機(jī)或系統(tǒng))

它是將多個(gè)架并排,架與架之間由布線或電纜相連接,由此構(gòu)成大型電子設(shè)備或電子系統(tǒng)。

封裝基板和封裝分級(jí)

從硅圓片制作開(kāi)始,微電子封裝可分為0、1、2、3四個(gè)等級(jí),涉及上述六個(gè)層次,封裝基板(PKG基板或Substrate)技術(shù)現(xiàn)涉及1、2、3三個(gè)等級(jí)和2~5的四個(gè)層次。

封裝基板主要研究前3個(gè)級(jí)別的半導(dǎo)體封裝(1、2、3級(jí)封裝),0級(jí)封裝暫與封裝基板無(wú)關(guān),因此封裝基板一般是指用于1級(jí)2級(jí)封裝的基板材料,母板(或載板)、剛撓結(jié)合板等用于三級(jí)封裝。

封裝基板和三級(jí)封裝

零級(jí)封裝

裸芯片電極的制作、引線的連接等均在硅片之上完成,暫與基板無(wú)關(guān)。

一級(jí)封裝

一級(jí)封裝經(jīng)0級(jí)封裝的單芯片或多芯片在封裝基板(普通基板、多層基板、HDI基板)上的封裝,構(gòu)成集成電路模塊(或元件)。即芯片在各類基板(或中介板)上的裝載方式。

二級(jí)封裝

二級(jí)封裝集成電路(IC元件或IC塊)片在封裝基板(普通基板、多層基板、HDI基板)上的封裝,構(gòu)成板或卡。即各種實(shí)裝方式(二級(jí)封裝或一級(jí)加二級(jí)封裝)。后續(xù)談到的的DIP、PGA屬于DIP封型,GFP、BGA、CSP等屬于SMT實(shí)裝型,這些都屬于二級(jí)封裝。

三級(jí)封裝

三級(jí)封裝包含4、5、6三個(gè)層次。即將多個(gè)完成層次3的板或卡,通過(guò)其上的插接端子搭載在稱為母板(或載板)的大型PCB板上,構(gòu)成單元組件(此層次也是實(shí)裝方式之一);或是將多個(gè)單元構(gòu)成架,單元與單元之間用布線(剛撓PCB)或電纜相連接;或是將多個(gè)架并排,架與架之間由布線(剛撓PCB)或電纜相連接,由此構(gòu)成大型電子設(shè)備或系統(tǒng)(此兩個(gè)層次稱為裝聯(lián))。

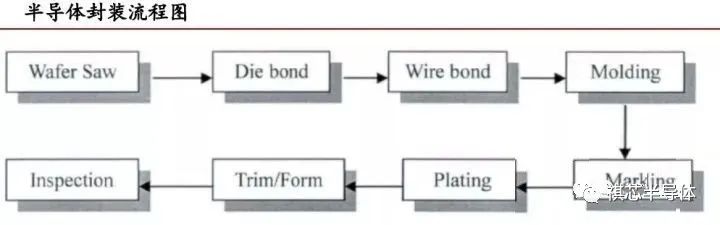

五、傳統(tǒng)集成電路(IC)封裝的主要生產(chǎn)過(guò)程

IC的封裝工藝流程可分為晶圓切割、晶圓粘貼、金線鍵合、塑封、激光打印、切筋打彎、檢驗(yàn)檢測(cè)等步驟。

傳統(tǒng)半導(dǎo)體封裝的七道工序 ? 晶圓切割 ?

首先將晶片用薄膜固定在支架環(huán)上,這是為了確保晶片在切割時(shí)被固定住,然后把晶圓根據(jù)已有的單元格式被切割成一個(gè)一個(gè)很微小的顆粒,切割時(shí)需要用去離子水冷卻切割所產(chǎn)生的溫度,而本身是防靜電的。

晶圓粘貼

晶圓粘貼的目的將切割好的晶圓顆粒用銀膏粘貼在引線框架的晶圓上,用粘合劑將已切下來(lái)的芯片貼裝到引線框架的中間焊盤(pán)上。通常是環(huán)氧(或聚酰亞胺)用作為填充物以增加粘合劑的導(dǎo)熱性。

金線鍵合

金線鍵合的目的是將晶圓上的鍵合壓點(diǎn)用極細(xì)的金線連接到引線框架上的內(nèi)引腳上,使得晶圓的電路連接到引腳。通常使用的金線的一端燒成小球,再將小球鍵合在第一焊點(diǎn)。然后按照設(shè)置好的程序拉金線,將金線鍵合在第二焊點(diǎn)上。

塑封

將完成引線鍵合的芯片與引線框架置于模腔中,再注入塑封化合物環(huán)氧樹(shù)脂用于包裹住晶圓和引線框架上的金線。這是為了保護(hù)晶圓元件和金線。塑封的過(guò)程分為加熱注塑,成型二個(gè)階段。塑封的目的主要是:保護(hù)元件不受損壞;防止氣體氧化內(nèi)部芯片;保證產(chǎn)品使用安全和穩(wěn)定。

激光打印

激光打印是用激光射線的方式在塑封膠表面打印標(biāo)識(shí)和數(shù)碼。包括制造商的信息,器件代碼,封裝日期,可以作為識(shí)別和可追溯性。

切筋打彎

將原來(lái)連接在一起的引線框架外管腳切斷分離,并將其彎曲成設(shè)計(jì)的形狀,但不能破壞環(huán)氧樹(shù)脂密封狀態(tài),并避免引腳扭曲變形,將切割好的產(chǎn)品裝入料管或托盤(pán)便于轉(zhuǎn)運(yùn)。

檢驗(yàn)

檢驗(yàn)檢查產(chǎn)品的外觀是否能符合設(shè)計(jì)和標(biāo)準(zhǔn)。常見(jiàn)的的測(cè)試項(xiàng)目包括:打印字符是否清晰、正確,引腳平整性、共面行,引腳間的腳距,塑封體是否損傷、電性能及其它功能測(cè)試等。

六、半導(dǎo)體封裝技術(shù)

芯片封裝的實(shí)質(zhì):

傳統(tǒng)意義的芯片封裝一般指安放集成電路芯片所用的封裝殼體,它同時(shí)可包含將晶圓切片與不同類型的芯片管腳架及封裝材料形成不同外形的封裝體的過(guò)程。從物理層面看,它的基本作用為:為集成電路芯片提供穩(wěn)定的安放環(huán)境,保護(hù)芯片不受外部惡劣條件(例如灰塵,水氣)的影響。從電性層面看,芯片封裝同時(shí)也是芯片與外界電路進(jìn)行信息交互的鏈路,它需要在芯片與外界電路間建立低噪聲、低延遲的信號(hào)回路。

然而不論封裝技術(shù)如何發(fā)展,歸根到底,芯片封裝技術(shù)都是采用某種連接方式把晶圓切片上的管腳與引線框架以及封裝殼或者封裝基板上的管腳相連構(gòu)成芯片。而封裝的本質(zhì)就是規(guī)避外界負(fù)面因素對(duì)芯片內(nèi)部電路的影響,同時(shí)將芯片與外部電路連接,當(dāng)然也同樣為了使芯片易于使用和運(yùn)輸。

芯片封裝技術(shù)越來(lái)越先進(jìn),管角間距越來(lái)越小,管腳密度卻越來(lái)越高,芯片封裝對(duì)溫度變化的耐受性越來(lái)越好,可靠性越來(lái)越高。另外一個(gè)重要的指標(biāo)就是看芯片與封裝面積的比例。

此外,封裝技術(shù)中的一個(gè)主要問(wèn)題是芯片占用面積,即芯片占用的印刷電路板(PCB)的面積。從早期的DIP封裝,當(dāng)前主流的CSP封裝,芯片與封裝的面積比可達(dá)1:1.14,已經(jīng)十分接近1:1的理想值。而更先進(jìn)MCM到SiP封裝,從平面堆疊到垂直堆疊,芯片與封裝的面積相同的情況下進(jìn)一步提高性能。

七、各種常用封裝管殼

八、封裝技術(shù)工藝發(fā)展歷程:

半導(dǎo)體封裝技術(shù)的發(fā)展歷史可劃分為三個(gè)階段。

第一階段(20世紀(jì)70年代之前)

以通孔插裝型封裝為主;典型的封裝形式包括最初的金屬圓形(TO型)封裝,以及后來(lái)的陶瓷雙列直插封裝(CDIP)、陶瓷-玻璃雙列直插封裝(Cer DIP)和塑料雙列直插封裝(PDIP)等;其中的PDIP,由于其性能優(yōu)良、成本低廉,同時(shí)又適于大批量生產(chǎn)而成為這一階段的主流產(chǎn)品。

第二階段(20世紀(jì)80年代以后)

從通孔插裝型封裝向表面貼裝型封裝的轉(zhuǎn)變,從平面兩邊引線型封裝向平面四邊引線型封裝發(fā)展。表面貼裝技術(shù)被稱為電子封裝領(lǐng)域的一場(chǎng)革命,得到迅猛發(fā)展。與之相適應(yīng),一些適應(yīng)表面貼裝技術(shù)的封裝形式,如塑料有引線片式裁體(PLCC)、塑料四邊引線扁平封裝(PQFP)、塑料小外形封裝(PSOP)以及無(wú)引線四邊扁平封裝(PQFN)等封裝形式應(yīng)運(yùn)而生,迅速發(fā)展。其中的PQFP,由于密度高、引線節(jié)距小、成本低并適于表面安裝,成為這一時(shí)期的主導(dǎo)產(chǎn)品。

第三階段(20世紀(jì)90年代以后)

半導(dǎo)體發(fā)展進(jìn)入超大規(guī)模半導(dǎo)體時(shí)代,特征尺寸達(dá)到0.18-0.25μm,要求半導(dǎo)體封裝向更高密度和更高速度方向發(fā)展。因此,半導(dǎo)體封裝的引線方式從平面四邊引線型向平面球柵陣列型封裝發(fā)展,引線技術(shù)從金屬引線向微型焊球方向發(fā)展。

在此背景下,焊球陣列封裝(BGA)獲得迅猛發(fā)展,并成為主流產(chǎn)品。BGA按封裝基板不同可分為塑料焊球陣列封裝(PBGA),陶瓷焊球陣列封裝(CBGA),載帶焊球陣列封裝(TBGA),帶散熱器焊球陣列封裝(EBGA),以及倒裝芯片焊球陣列封裝(FC-BGA)等。

為適應(yīng)手機(jī)、筆記本電腦等便攜式電子產(chǎn)品小、輕、薄、低成本等需求,在BGA的基礎(chǔ)上又發(fā)展了芯片級(jí)封裝(CSP);CSP又包括引線框架型CSP、柔性插入板CSP、剛性插入板CSP、園片級(jí)CSP等各種形式,目前處于快速發(fā)展階段。

同時(shí),多芯片組件(MCM)和系統(tǒng)封裝(SiP)也在蓬勃發(fā)展,這可能孕育著電子封裝的下一場(chǎng)革命性變革。MCM按照基板材料的不同分為多層陶瓷基板MCM(MCM-C)、多層薄膜基板MCM(MCM-D)、多層印制板MCM(MCM-L)和厚薄膜混合基板MCM(MCM-C/D)等多種形式。SiP是為整機(jī)系統(tǒng)小型化的需要,提高半導(dǎo)體功能和密度而發(fā)展起來(lái)的。SiP使用成熟的組裝和互連技術(shù),把各種集成電路如CMOS電路、GaAs電路、SiGe電路或者光電子器件、MEMS器件以及各類無(wú)源元件如電阻、電容、電感等集成到一個(gè)封裝體內(nèi),實(shí)現(xiàn)整機(jī)系統(tǒng)的功能。

目前,半導(dǎo)體封裝處于第三階段的成熟期與快速增長(zhǎng)期,以BGA/CSP等主要封裝形式開(kāi)始進(jìn)入規(guī)模化生產(chǎn)階段。同時(shí),以SiP和MCM為主要發(fā)展方向的第四次技術(shù)變革處于孕育階段。

九、半導(dǎo)體封裝材料

半導(dǎo)體元件的封接或封裝方式分為氣密性封裝和樹(shù)脂封裝兩大類,氣密性封裝又可分為金屬封裝、陶瓷封裝和玻璃封裝。封接和封裝的目的是與外部溫度、濕度、氣氛等環(huán)境隔絕,除了起保護(hù)和電氣絕緣作用外,同時(shí)還起向外散熱及應(yīng)力緩和作用。一般來(lái)說(shuō),氣密性封裝可靠性高,但價(jià)格也高。目前由于封裝技術(shù)及材料的改進(jìn),樹(shù)脂封裝已占絕對(duì)優(yōu)勢(shì),但在有些特殊領(lǐng)域(軍工、航空、航天、航海等),氣密性封裝是必不可少的。

按封裝材料可劃分為:金屬封裝、陶瓷封裝(C)、塑料封裝(P)。采用前兩種封裝的半導(dǎo)體產(chǎn)品主要用于航天、航空及軍事領(lǐng)域,而塑料封裝的半導(dǎo)體產(chǎn)品在民用領(lǐng)域得到了廣泛的應(yīng)用。目前樹(shù)脂封裝已占世界集成電路封裝市場(chǎng)的98%,97%以上的半導(dǎo)體器件的封裝都采用樹(shù)脂封裝,在消費(fèi)類電路和器件領(lǐng)域基本上是樹(shù)脂封裝一統(tǒng)天下,而90%以上的塑封料是環(huán)氧樹(shù)脂塑封料和環(huán)氧液體灌封料。

十、芯片電學(xué)(零級(jí)封裝)互連

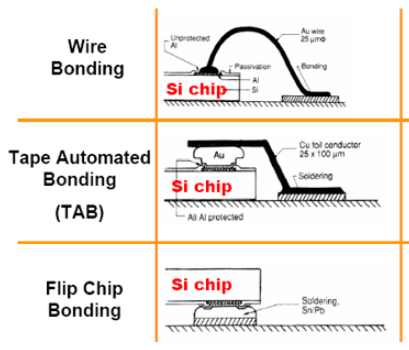

在一級(jí)封裝中,有個(gè)很重要的步驟就是將芯片和封裝體(進(jìn)行電學(xué)互連的過(guò)程,通常稱為芯片互連技術(shù)或者芯片組裝。為了凸顯其重要性,有些教科書(shū)也將其列為零級(jí)封裝。也就是將芯片上的焊盤(pán)或凸點(diǎn)與封裝體通常是引線框架用金屬連接起來(lái))。在微電子封裝中,半導(dǎo)體器件的失效約有一是由于芯片互連引起的,其中包括芯片互連處的引線的短路和開(kāi)路等,所以芯片互連對(duì)器件的可靠性非常重要。

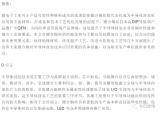

常見(jiàn)的芯片電學(xué)互連有三種方式,分別是引線鍵合,載帶自動(dòng)焊和倒裝焊。

通常,TAB和FC雖然互連的電學(xué)性能要比好,但是都需要額外的設(shè)備。因此,對(duì)于I/O數(shù)目較少的芯片,TAB和FC成本很高,另外,在3D封裝中,由于芯片堆疊,堆疊的芯片不能都倒扣在封裝體上,只能通過(guò)WB與封裝體之間進(jìn)行互連。基于這些原因,到目前為止,WB一直是芯片互連的主流技術(shù),在芯片電學(xué)互連中占據(jù)非常重要的地位。

芯片電學(xué)互連(零級(jí)封裝)的三種方式

引線鍵合(WB)

引線鍵合(WB)是將芯片焊盤(pán)和對(duì)應(yīng)的封裝體上焊盤(pán)用細(xì)金屬絲一一連接起來(lái),每次連接一根,是最簡(jiǎn)單的一種芯片電學(xué)互連技術(shù),按照電氣連接方式來(lái)看屬于有線鍵合。

載帶自動(dòng)焊(TAB)

載帶自動(dòng)焊(TAB)是一種將IC安裝和互連到柔性金屬化聚合物載帶上的IC組裝技術(shù)。載帶內(nèi)引線鍵合到IC上,外引線鍵合到常規(guī)封裝或者PCB上,整個(gè)過(guò)程均自動(dòng)完成,因此,效率比要高。按照電氣連接方式來(lái)看屬于無(wú)線鍵合方法。

倒裝焊(FC)

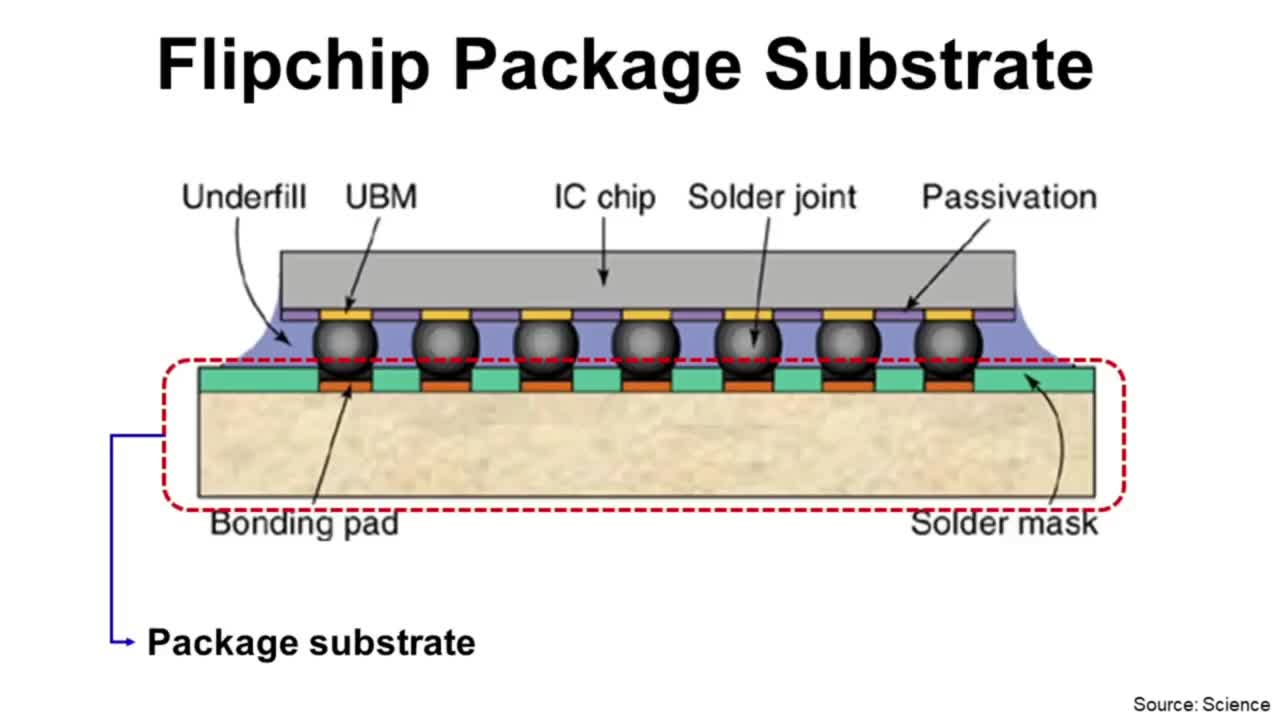

倒裝焊(FC)是指集成電路芯片的有源面朝下與載體或基板進(jìn)行連接。芯片和基板之間的互連通過(guò)芯片上的凸點(diǎn)結(jié)構(gòu)和基板上的鍵合材料來(lái)實(shí)現(xiàn)。這樣可以同時(shí)實(shí)現(xiàn)機(jī)械互連和電學(xué)互連。同時(shí)為了提高互連的可靠性,在芯片和基板之間加上底部填料。對(duì)于高密度的芯片,倒裝焊不論在成本還是性能上都有很強(qiáng)的優(yōu)勢(shì),是芯片電學(xué)互連的發(fā)展趨勢(shì)。按照電氣連接方式來(lái)看屬于無(wú)線鍵合方法。

十一、半導(dǎo)體封裝的典型封裝工藝簡(jiǎn)介

依據(jù)封裝管腳的排布方式、芯片與PCB板連接方式以及發(fā)展的時(shí)間先后順序,半導(dǎo)體封裝可劃分為PTH封裝(Pin-Through-Hole)和SMT封裝(Surface-Mount-Technology)二大類,即通常所稱的插孔式(或通孔式)和表面貼裝式。

針腳插裝技術(shù)(PTH):

針腳插裝封裝,顧名思義即在芯片與目標(biāo)板的連接過(guò)程中使用插裝方式,古老而經(jīng)典DIP封裝即屬于該種封裝形式。在早期集成電路中由于芯片集成度不高,芯片工作所需的輸入/輸出管腳數(shù)較少,所以多采用該種封裝形式。DIP封裝有兩種衍生封裝形式,即為:SiP和ZIP,只是為適應(yīng)不同的應(yīng)用領(lǐng)域,對(duì)傳統(tǒng)DIP封裝在封裝殼管腳排布和形狀上略有改進(jìn)。

表面貼裝封裝(SMT):

PTH封裝在機(jī)械連接強(qiáng)度上的優(yōu)勢(shì)毋庸質(zhì)疑,但同時(shí)也帶來(lái)一些負(fù)面效應(yīng)。PTH封裝中使用的貫通孔將大量占用PCB板有效布線面積,因此目前主流的PCB板設(shè)計(jì)中多使用表面貼片封裝。

表面貼片封裝有很多種類,常用的封裝形式有:

小型塑封晶體管(Small Outline Transistor,SOT)

小引出線封裝(Smal lOutline Package,SOP)

四方扁平無(wú)引線封裝(Quad Flat No-lead Package,QFN)

薄小縮小外形封裝(Thin Small Shrink Outline Package,TSSOP)

方型扁平式封裝(Quad Flat Package,QFP)

方形扁平無(wú)引腳封裝(QFN)

從SOT到QFN,芯片封裝殼支持的管腳數(shù)越來(lái)越多,芯片封裝殼的管角間距越來(lái)越小。

表面貼片封裝方式的優(yōu)點(diǎn)在于芯片封裝的尺寸大大下降,芯片封裝的管腳密度大大提升,與PTH封裝具有相同管腳數(shù)量時(shí),表面貼片封裝的封裝尺寸將遠(yuǎn)小于PTH封裝。表面貼片封裝只占用PCB板表層布線空間,在使用多層布線工藝時(shí),封裝占用的有效布線面積大大下降,可以大大提高PCB板布線密度和利用率。

十二、芯片級(jí)(CSP)封裝技術(shù)

CSP定義

根據(jù)J-STD-012標(biāo)準(zhǔn)的定義,CSP是指封裝尺不超過(guò)裸芯片1.2倍的一種先進(jìn)的封裝形式。一般認(rèn)為CSP技術(shù)是在對(duì)現(xiàn)有的芯片封裝技術(shù),尤其是對(duì)成熟的BGA封裝技術(shù)做進(jìn)一步技術(shù)提升的過(guò)程中,不斷將各種封裝尺寸進(jìn)一步小型化而產(chǎn)生的一種封裝技術(shù)。

CSP技術(shù)可以確保超大規(guī)模集成電路在高性能、高可靠性的前提下,以最低廉的成本實(shí)現(xiàn)封裝的尺寸最接近裸芯片尺寸。與QFP封裝相比,CSP封裝尺寸小于管腳間距為0.5mm的QFP封裝的1/10;與BGA封裝相比,CSP封裝尺寸約為BGA封裝的1/3。

當(dāng)封裝尺寸固定時(shí),若想進(jìn)一步提升管腳數(shù),則需縮小管腳間距。受制于現(xiàn)有工藝,不同封裝形式存在工藝極限值。如BGA封裝矩陣式值球最高可達(dá)1000個(gè),但CSP封裝可支持超出2000的管腳。

CSP的主要結(jié)構(gòu)有內(nèi)芯芯片、互連層、焊球(或凸點(diǎn)、焊柱)、保護(hù)層等幾大部分,芯片與封裝殼是在互連層實(shí)現(xiàn)機(jī)械連接和電性連接。其中,互連層是通過(guò)載帶自動(dòng)焊接或引線鍵合、倒裝芯片等方法,來(lái)實(shí)現(xiàn)芯片與焊球之間的內(nèi)部連接,是CSP關(guān)鍵組成部分。

目前有多種符合CSP定義的封裝結(jié)構(gòu)形式,其特點(diǎn)有:

CSP的芯片面積與封裝面積之比與1:1的理想狀況非常接近,絕對(duì)尺寸為32mm2,相當(dāng)于BGA的三分之一和TSOP的六分之一,即CSP可將內(nèi)存容量提高3~6倍之多。

測(cè)試結(jié)果顯示,CSP可使芯片88.4%的工作熱量傳導(dǎo)至PCB,熱阻為35℃/W-1,而TSOP僅能傳導(dǎo)總熱量的71.3%,熱阻為40℃/W-1。

CSP所采用的中心球形引腳形式能有效地縮短信號(hào)的傳導(dǎo)距離,信號(hào)衰減也隨之減少,芯片的抗干擾、抗噪性能更強(qiáng),存取時(shí)間比BGA減少15%~20%,完全能適應(yīng)DDRⅡ,DRDRAM等超高頻率內(nèi)存芯片的實(shí)際需要。

CSP可容易地制造出超過(guò)1000根信號(hào)引腳數(shù),即使最復(fù)雜的內(nèi)存芯片都能封裝,在引腳數(shù)相同的情況下,CSP的組裝遠(yuǎn)比BGA容易。CSP還可進(jìn)行全面老化、篩選、測(cè)試,且操作、修整方便,能獲得真正的KGD(Known GoodDie已知合格芯片)芯片。

CSP封裝形式主要有如下分類 ?

芯片級(jí)封裝的主要類型:

柔性基片CSP

顧名思義是采用柔性材料制成芯片載體基片,在塑料薄膜上制作金屬線路,然后將芯片與之連接。柔性基片CSP產(chǎn)品,芯片焊盤(pán)與基片焊盤(pán)間的連接方式可以是倒裝鍵合、TAB鍵合、引線鍵合等多種方式,不同連接方式封裝工藝略有差異。

硬質(zhì)基片CSP

其芯片封裝載體基材為多層線路板制成,基板材質(zhì)可為陶瓷或?qū)訅簶?shù)脂板。

引線框架CSP

技術(shù)是由日本的Fujitsu公司首先研發(fā)成功,使用與傳統(tǒng)封裝相類似的引線框架來(lái)完成CSP封裝。引線框架CSP技術(shù)使用的引線框架與傳統(tǒng)封裝引線框架的區(qū)別在于該技術(shù)使用的引線框架尺寸稍小,厚度稍薄。

微小模塑型CSP

是由日本三菱電機(jī)公司提出的一種CSP封裝形式。芯片管腳通過(guò)金屬導(dǎo)線與外部焊球連接,整個(gè)封裝過(guò)程中不需使用額外引線框架,封裝內(nèi)芯片與焊球連接線很短,信號(hào)品質(zhì)較好。

晶圓級(jí)CSP

由ChipScale公司開(kāi)發(fā)。其技術(shù)特點(diǎn)在于直接使用晶圓制程完成芯片封裝。與其他各類CSP相比,晶圓級(jí)CSP所有工藝使用相同制程完成,工藝穩(wěn)定。基于上述優(yōu)點(diǎn),晶圓級(jí)CSP封裝有望成為未來(lái)的CSP封裝的主流方式。

十三、先進(jìn)封裝

堆疊封裝

堆疊封裝技術(shù)是一種對(duì)兩個(gè)以上芯片(片芯、籽芯)、封裝器件或電路卡進(jìn)行機(jī)械和電氣組裝的方法,在有限的空間內(nèi)成倍提高存儲(chǔ)器容量,或?qū)崿F(xiàn)電子設(shè)計(jì)功能,解決空間、互連受限問(wèn)題。

堆疊封裝分為定制堆疊和標(biāo)準(zhǔn)商業(yè)堆疊兩大類型:前者是通過(guò)芯片層次工藝高密度化,其設(shè)計(jì)和制造成本相對(duì)較高;后者采用板卡堆疊、柔性電路連接器聯(lián)接、封裝后堆疊、芯片堆疊式封裝等方式,其成本比采用單芯片封裝器件的存儲(chǔ)器模塊高平均15%~20%。應(yīng)該看到,芯片堆疊式封裝的成本效率最高,在一個(gè)封裝體內(nèi)有2~5層芯片堆疊,從而能在封裝面積不變的前提下,有效利用立體空間提高存儲(chǔ)容量,主要用于DRAM、閃存和SRAM。另外,通過(guò)堆疊TSOP可分別節(jié)約50%或77%的板級(jí)面積。

芯片堆疊封裝主要強(qiáng)調(diào)用于堆疊的基本“元素”是晶圓切片。

多芯片封裝、堆疊芯片尺寸封裝、超薄堆疊芯片尺寸封裝等均屬于芯片堆疊封裝的范疇。芯片堆疊封裝技術(shù)優(yōu)勢(shì)在于采用減薄后的晶圓切片可使封裝的高度更低。

堆疊封裝有兩種不同的表現(xiàn)形式,即PoP堆疊(Package on Package,PoP)和PiP堆疊(Package in Package Stacking,PiP)。

PoP堆疊使用經(jīng)過(guò)完整測(cè)試且封裝完整的芯片,其制作方式是將完整的單芯片或堆疊芯片堆疊到另外一片完整單芯片或堆疊芯片的上部。其優(yōu)勢(shì)在于參與堆疊的基本“元素”為成品芯片,所以該技術(shù)理論上可將符合堆疊要求的任意芯片進(jìn)行堆疊。

PiP堆疊使用經(jīng)過(guò)簡(jiǎn)單測(cè)試的內(nèi)部堆疊模塊和基本組裝封裝作為基本堆疊模塊,但受限于內(nèi)部堆疊模塊和基本組裝封裝的低良率,PiP堆疊成品良率較差。但PiP的優(yōu)勢(shì)也十分明顯,即在堆疊中可使用焊接工藝實(shí)現(xiàn)堆疊連接,成本較為低廉。

PoP封裝外形高度高于PiP封裝,但是裝配前各個(gè)器件可以單獨(dú)完整測(cè)試,封裝后的成品良率較好。

堆疊封裝技術(shù)中封裝后成品體積最小的應(yīng)屬3D封裝技術(shù)。

3D封裝可以在更小,更薄的封裝殼內(nèi)封裝更多的芯片。按照結(jié)構(gòu)3D封裝可分為芯片堆疊封裝和封裝堆疊封裝。

晶圓級(jí)封裝(WLP)

WLP的優(yōu)勢(shì):

晶圓級(jí)封裝(WLP)就是在封裝過(guò)程中大部分工藝過(guò)程都是對(duì)晶圓(大圓片)進(jìn)行操作,對(duì)晶圓級(jí)封裝(WLP)的需求不僅受到更小封裝尺寸和高度的要求,還必須滿足簡(jiǎn)化供應(yīng)鏈和降低總體成本,并提高整體性能的要求。

晶圓級(jí)封裝提供了倒裝芯片這一具有極大優(yōu)勢(shì)的技術(shù),倒裝芯片中芯片面朝下對(duì)著印刷電路板(PCB),可以實(shí)現(xiàn)最短的電路徑,這也保證了更高的速度,降低成本是晶圓級(jí)封裝的另一個(gè)推動(dòng)力量。

器件采用批量封裝,整個(gè)晶圓能夠?qū)崿F(xiàn)一次全部封裝。在給定晶片上封裝器件的成本不會(huì)隨著每片晶片的裸片數(shù)量而改變,因?yàn)樗泄に嚩际怯醚谀9に囘M(jìn)行的加成和減法的步驟。

WLP技術(shù)的兩種類型:

總體來(lái)說(shuō),WLP技術(shù)有兩種類型:“扇入式”(fan-in)和“扇出式”(fan-out)晶圓級(jí)封裝。

傳統(tǒng)扇入WLP在晶圓未切割時(shí)就已經(jīng)形成。在裸片上,最終的封裝器件的二維平面尺寸與芯片本身尺寸相同。器件完全封裝后可以實(shí)現(xiàn)器件的單一化分離(singulation)。因此,扇入式WLP是一種獨(dú)特的封裝形式,并具有真正裸片尺寸的顯著特點(diǎn)。具有扇入設(shè)計(jì)的WLP通常用于低輸入/輸出(I/O)數(shù)量(一般小于400)和較小裸片尺寸的工藝當(dāng)中。

另一方面,隨著封裝技術(shù)的發(fā)展,逐漸出現(xiàn)了扇出式WLP。扇出WLP初始用于將獨(dú)立的裸片重新組裝或重新配置到晶圓工藝中,并以此為基礎(chǔ),通過(guò)批量處理、構(gòu)建和金屬化結(jié)構(gòu),如傳統(tǒng)的扇入式WLP后端處理,以形成最終封裝。

扇出式WLP可根據(jù)工藝過(guò)程分為芯片先上(Die First)和芯片后上(Die Last),芯片先上工藝,簡(jiǎn)單地說(shuō)就是先把芯片放上,再做布線(RDL),芯片后上就是先做布線,測(cè)試合格的單元再把芯片放上去,芯片后上工藝的優(yōu)點(diǎn)就是可以提高合格芯片的利用率以提高成品率,但工藝相對(duì)復(fù)雜。eWLB就是典型的芯片先上的Fan out工藝,長(zhǎng)電科技星科金朋的Fan-out,安靠(Amkor)的葡萄牙工廠均采用的芯片先上的工藝。TSMC的INFO也是芯片先上的Fan-out產(chǎn)品。安靠和ASE也都有自己成熟的芯片后上的Fan-out工藝。

在電子設(shè)備的發(fā)展歷史中,WLP封裝技術(shù)的推廣產(chǎn)生了很多全新的產(chǎn)品。

例如得益于WLP的使用,摩托羅拉能夠推出其RAZR手機(jī),該手機(jī)也是其推出時(shí)最薄的手機(jī)。最新型號(hào)的iPhone采用了超過(guò)50顆WLP,智能手機(jī)是WLP發(fā)展的最大推動(dòng)力。

隨著金線價(jià)格的上漲,一些公司也正在考慮采用WLP作為低成本替代方案,而不是采用引線鍵合封裝,尤其是針對(duì)更高引腳數(shù)的器件。最近幾年中,WLP也已經(jīng)被廣泛用于圖像傳感器的應(yīng)用中。目前,硅通孔(TSV)技術(shù)已被納入用于封裝圖像傳感器的WLP解決方案。其他更新的封裝技術(shù)也在逐漸發(fā)展,并與現(xiàn)有的WLP技術(shù)進(jìn)行整合,例如三維(3D)集成技術(shù)。

2.5D/3D先進(jìn)封裝集成工藝

新興的2.5D和3D技術(shù)有望擴(kuò)展到倒裝芯片和晶圓級(jí)封裝工藝中。通過(guò)使用硅中介層(Interposers)和硅通孔(TSV)技術(shù),可以將多個(gè)芯片進(jìn)行垂直堆疊。TSV堆疊技術(shù)實(shí)現(xiàn)了在不增加IC平面尺寸的情況下,融合更多的功能到IC中,允許將更大量的功能封裝到IC中而不必增加其平面尺寸,并且硅中介層用于縮短通過(guò)集成電路中的一些關(guān)鍵電通路來(lái)實(shí)現(xiàn)更快的輸入和輸出。因此,使用先進(jìn)封裝技術(shù)封裝的應(yīng)用處理器和內(nèi)存芯片將比使用舊技術(shù)封裝的芯片小約30%或40%,比使用舊技術(shù)封裝的芯片快2~3倍,并且可以節(jié)省高達(dá)40%或者更多的功率。

2.5D和3D技術(shù)的復(fù)雜性以及生產(chǎn)這些芯片的IC制造商(Fab)和外包封裝/測(cè)試廠商的經(jīng)濟(jì)性意味著IDM和代工廠仍需要處理前端工作,而外包封裝/測(cè)試廠商仍然最適合處理后端過(guò)程,比如通過(guò)露出、凸點(diǎn)、堆疊和測(cè)試。外包封裝/測(cè)試廠商的工藝與生產(chǎn)主要依賴于內(nèi)插件的制造,這是一種對(duì)技術(shù)要求較低的成本敏感型工藝。

三維封裝可以更高效地利用硅片,達(dá)到更高的“硅片效率”。硅片效率是指堆疊中的總基板面積與占地面積的比率。因此,與其他2D封裝技術(shù)相比,3D技術(shù)的硅效率超過(guò)了100%。而在延遲方面,需要通過(guò)縮短互連長(zhǎng)度來(lái)減少互連相關(guān)的寄生電容和電感,從而來(lái)減少信號(hào)傳播延遲。而在3D技術(shù)中,電子元件相互靠得很近,所以延遲會(huì)更少。相類似,3D技術(shù)在降低噪聲和降低功耗方面的作用在于減少互連長(zhǎng)度,從而減少相關(guān)寄生效應(yīng),從而轉(zhuǎn)化為性能改進(jìn),并更大程度的降低成本。此外,采用3D技術(shù)在降低功耗的同時(shí),可以使3D器件以更高的頻率運(yùn)行,而3D器件的寄生效應(yīng)、尺寸和噪聲的降低可實(shí)現(xiàn)更高的每秒轉(zhuǎn)換速率,從而提高整體系統(tǒng)性能。

3D集成技術(shù)作為2010年以來(lái)得到重點(diǎn)關(guān)注和廣泛應(yīng)用的封裝技術(shù),通過(guò)用3D設(shè)備取代單芯片封裝,可以實(shí)現(xiàn)相當(dāng)大的尺寸和重量降低。這些減少量的大小部分取決于垂直互連密度和可獲取性(accessibility)和熱特性等。據(jù)報(bào)道,與傳統(tǒng)封裝相比,使用3D技術(shù)可以實(shí)現(xiàn)40~50倍的尺寸和重量減少。

舉例來(lái)說(shuō),德州儀器(TI)的3D裸片封裝與離散和平面封裝(MCM)之間的體積和重量相比,可以減少5~6倍的體積,并且在分立封裝技術(shù)上可以減少10~20倍。此外,與MCM技術(shù)相比,重量減少2~13倍,與分立元件相比,重量減少3~19倍。此外,封裝技術(shù)中的一個(gè)主要問(wèn)題是芯片占用面積,即芯片占用的印刷電路板(PCB)的面積。在采用MCM的情況下,芯片占用面積減少20%~90%,這主要是因?yàn)槁闫氖褂谩?/p>

十四、系統(tǒng)級(jí)封裝SiP技術(shù)

SiP是半導(dǎo)體封裝領(lǐng)域的最高端的一種新型封裝技術(shù),將一個(gè)或多個(gè)IC芯片及被動(dòng)元件整合在一個(gè)封裝中,綜合了現(xiàn)有的芯核資源和半導(dǎo)體生產(chǎn)工藝的優(yōu)勢(shì)。SiP是為整機(jī)系統(tǒng)小型化的需要,提高半導(dǎo)體功能和密度而發(fā)展起來(lái)的。SiP使用成熟的組裝和互連技術(shù),把各種集成電路如CMOS電路、GaAs電路、SiGe電路或者光電子器件、MEMS器件以及各類無(wú)源元件如電阻、電容、電感等集成到一個(gè)封裝體內(nèi)。

自從1960年代以來(lái),集成電路的封裝形式經(jīng)歷了從雙列直插、四周扁平封裝、焊球陣列封裝和圓片級(jí)封裝、芯片尺寸封裝等階段。而小型化、輕量化、高性能、多功能、高可靠性和低成本的電子產(chǎn)品的總體發(fā)展趨勢(shì)使得單一芯片上的晶體管數(shù)目不再是面臨的主要挑戰(zhàn),而是要發(fā)展更先進(jìn)的封裝及時(shí)來(lái)滿足產(chǎn)品輕、薄、短、小以及與系統(tǒng)整合的需求,這也使得在獨(dú)立的系統(tǒng)(芯片或者模塊)內(nèi)充分實(shí)現(xiàn)芯片的功能成為需要克服的障礙。這樣的背景是SiP逐漸成為近年來(lái)集成電路研發(fā)機(jī)構(gòu)和半導(dǎo)體廠商的重點(diǎn)研究對(duì)象。SiP作為一種全新的集成方法和封裝技術(shù),具有一系列獨(dú)特的技術(shù)優(yōu)勢(shì),滿足了當(dāng)今電子產(chǎn)品更輕、更小和更薄的發(fā)展需求,在微電子領(lǐng)域具有廣闊的應(yīng)用市場(chǎng)和發(fā)展前景。

SiP/SoP

近年來(lái),隨著消費(fèi)類電子產(chǎn)品(尤其是移動(dòng)通信電子產(chǎn)品)的飛速發(fā)展,使得三維高密度系統(tǒng)級(jí)封裝(3D SiP,System in Package/SoP,System on Package)成為了實(shí)現(xiàn)高性能、低功耗、小型化、異質(zhì)工藝集成、低成本的系統(tǒng)集成電子產(chǎn)品的重要技術(shù)方案,國(guó)際半導(dǎo)體技術(shù)路線(ITRS)已經(jīng)明確SiP/SoP將是未來(lái)超越摩爾(More than Moore)定律的主要技術(shù)。SiP從結(jié)構(gòu)方向上可以分為兩類基本的形式,一類是多塊芯片平面排布的二維封裝結(jié)構(gòu)(2D SiP),另一類是芯片垂直疊裝的三維封裝/集成結(jié)構(gòu)(3D SiP)。

在2D SiP結(jié)構(gòu)中,芯片并排水平貼裝在基板上的,貼裝不受芯片尺寸大小的限制,工藝相對(duì)簡(jiǎn)單和成熟,但其封裝面積相應(yīng)地比較大,封裝效率比較低。3DSiP可實(shí)現(xiàn)較高的封裝效率,能最大限度地發(fā)揮SiP的技術(shù)優(yōu)勢(shì),是實(shí)現(xiàn)系統(tǒng)集成的最為有效的技術(shù)途徑,實(shí)際上涉及多種先進(jìn)的封裝技術(shù),包括封裝堆疊(PoP)、芯片堆疊(CoC)、硅通孔(TSV)、埋入式基板(Embedded Substrate)等,也涉及引線鍵合、倒裝芯片、微凸點(diǎn)等其他封裝工藝。3DSiP的基本概念正是將可能實(shí)現(xiàn)的多種功能集成于一個(gè)系統(tǒng)中,包括微處理器、存儲(chǔ)器、模擬電路、電源轉(zhuǎn)化模塊、光電器件等,還可能將散熱通道等部件也集成在封裝中,最大程度的體現(xiàn)SiP的技術(shù)優(yōu)勢(shì)。

系統(tǒng)級(jí)封裝技術(shù)可以解決目前我們遇到的很多問(wèn)題,其優(yōu)勢(shì)也是越來(lái)越明顯,如產(chǎn)品設(shè)計(jì)的小型化、功能豐富化、產(chǎn)品可靠性等,產(chǎn)品制造也越來(lái)越極致,尤為重要的是,提高了生產(chǎn)效率,并大幅降低了生產(chǎn)成本。當(dāng)然,難點(diǎn)也是存在的,系統(tǒng)級(jí)封裝的實(shí)現(xiàn),需要各節(jié)點(diǎn)所有技術(shù),而不是某一技術(shù)所能實(shí)現(xiàn)的,這對(duì)封裝企業(yè)來(lái)說(shuō),就需要有足夠的封裝技術(shù)積累及可靠的封裝平臺(tái)支撐,如高密度模組技術(shù)、晶圓級(jí)封裝技術(shù)等。

多芯片組件(MCM)

多芯片組件(MCM)屬于系統(tǒng)級(jí)封裝,是電子封裝技術(shù)層面的大突破。MCM是指一個(gè)封裝體中包含通過(guò)基板互連起來(lái),共同構(gòu)成整個(gè)系統(tǒng)的封裝形式的兩個(gè)或兩個(gè)以上的芯片。并為組件中的所有芯片提供信號(hào)互連、I/O管理、熱控制、機(jī)械支撐和環(huán)境保護(hù)等條件。根據(jù)所用多層布線基板的類型不同,MCM可分為疊層多芯片組件(MCM-L)、陶瓷多芯片組件(MCM-C)、淀積多芯片組件(MCM-D)以及混合多芯片組件(MCM–C/D)等。

多芯片封裝技術(shù)從某種程度上而言可以減少由芯片功能過(guò)于復(fù)雜帶來(lái)的研發(fā)壓力。由于多芯片方案可以使用完全獨(dú)立的成熟芯片搭建系統(tǒng),無(wú)論從成本角度還是從技術(shù)角度考慮,單芯片方案的研發(fā)難度遠(yuǎn)大于多芯片方案。現(xiàn)階段產(chǎn)品發(fā)展的趨勢(shì)為小型化便攜式產(chǎn)品,產(chǎn)品外部尺寸的縮小將壓縮芯片可用布線空間,這就迫使封裝技術(shù)改善封裝的尺寸來(lái)適應(yīng)更小型的產(chǎn)品。

審核編輯:湯梓紅

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論