作為半導體從業(yè)者的我們或許都應該知道:

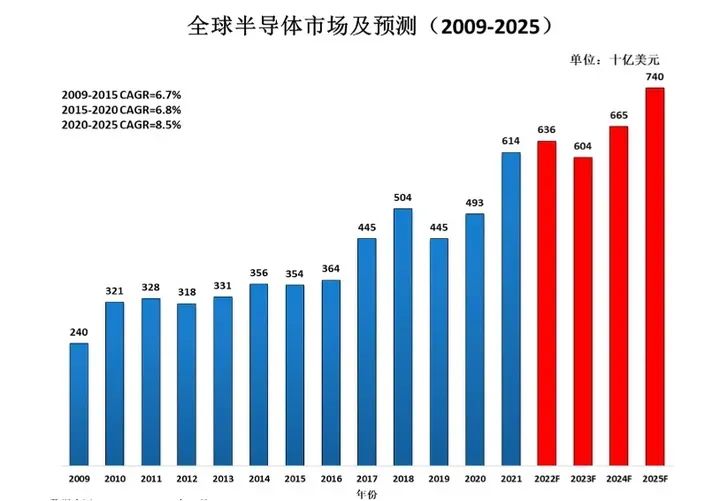

隨著疫情放開后經(jīng)濟回暖,全球半導體產(chǎn)業(yè)鏈向國內(nèi)轉(zhuǎn)移,封測產(chǎn)業(yè)已成為我國半導體的強勢產(chǎn)業(yè),市場規(guī)模持續(xù)向上突破。

在此期間,封測行業(yè)景氣再度修復,2023年半導體市場將實現(xiàn)復蘇,封測環(huán)節(jié)有望充分受益。

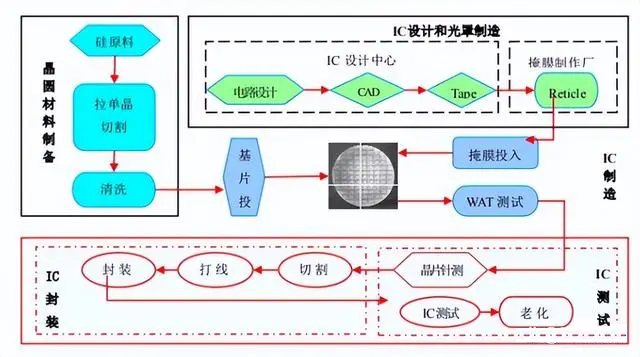

對于芯片而言,從設計到生產(chǎn)的流程特別復雜;具體可分為:設計、制造和封測三大環(huán)節(jié),其中封測是集成電路產(chǎn)品制造的后道工序。

可以說:半導體封測是在晶圓設計、制造完成之后,對測試合格的晶圓進行封裝檢測得到獨立芯片的過程。

封測主要包括了封裝和測試兩個環(huán)節(jié),從價值占比上來看,集成電路封裝環(huán)節(jié)價值占比約為80%,測試環(huán)節(jié)價值占比約為15%。

其中,封裝測試是將生產(chǎn)出來的合格晶圓進行切割、焊線、塑封,使芯片電路與外部器件實現(xiàn)電氣連接,為芯片提供機械物理保護;并利用集成電路設計企業(yè)提供的測試工具,對封裝完畢的芯片進行功能和性能測試。

其次,只有經(jīng)過封測的芯片,才能夠在實際應用中發(fā)揮其性能,為各種電子設備提供計算、通信和控制功能。

圖片來自:Google

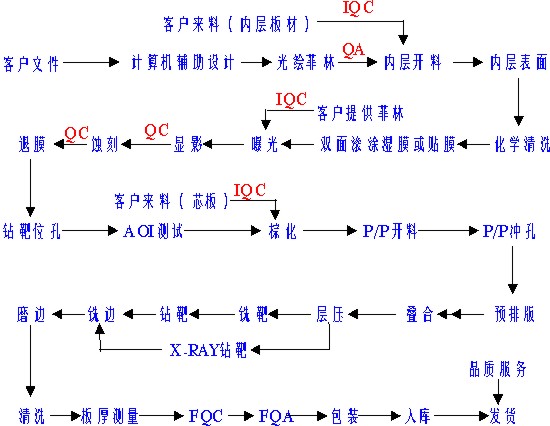

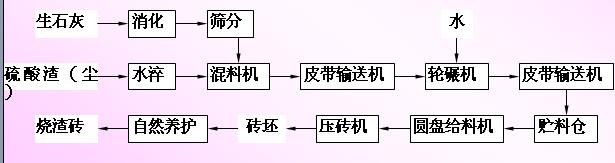

首先,我們要知道封測的主要工藝流程有哪些:

晶圓減薄(wafer grinding):剛出廠的晶圓(wafer)需要進行背面減薄,至封裝需要的厚度。在背面磨片時,要在正面粘貼膠帶來保護電路區(qū)域。研磨之后,再去除膠帶。

晶圓切割(wafer Saw):將晶圓粘貼在藍膜上,再將晶圓切割成一個個獨立的Dice,再對Dice進行清洗。

光檢查:檢查是否出現(xiàn)殘次品。

芯片貼裝(Die Attach):將芯片粘接在基板上,銀漿固化以防止氧化,再引線焊接。

因此,芯片半導體封測測試是確保芯片品質(zhì)和性能的重要步驟:

功能測試(Functional Test):對芯片的功能進行測試,驗證芯片是否符合設計要求,包括數(shù)字、模擬、混合信號電路的測試等。

可靠性測試(Reliability Test):對芯片的可靠性進行測試,驗證芯片在各種工作條件下的可靠性,包括溫度循環(huán)測試、熱老化測試、高溫高濕測試等

外觀檢查(Visual Inspection):對芯片的外觀進行檢查,驗證芯片的封裝是否完好、引腳是否損壞等。

焊點可靠性測試(Solder Joint Reliability Test):對芯片焊點的可靠性進行測試,驗證焊點的可靠性和連接強度。

熱分析測試(Thermal Analysis Test):對芯片的散熱性能進行測試,驗證芯片的散熱效果和散熱結(jié)構(gòu)的可靠性。

電氣特性測試(Electrical Characterization Test):對芯片的電氣特性進行測試,驗證芯片的電氣性能,包括電壓、電流、功率等。

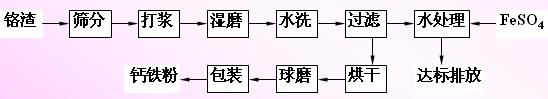

其核心點在于:

半導體封裝測試需要使用專業(yè)的設備,如貼片機、焊接機、測試儀器等;這些設備需要具備高精度、高速度和高穩(wěn)定性的特點,以滿足封裝工藝的要求。

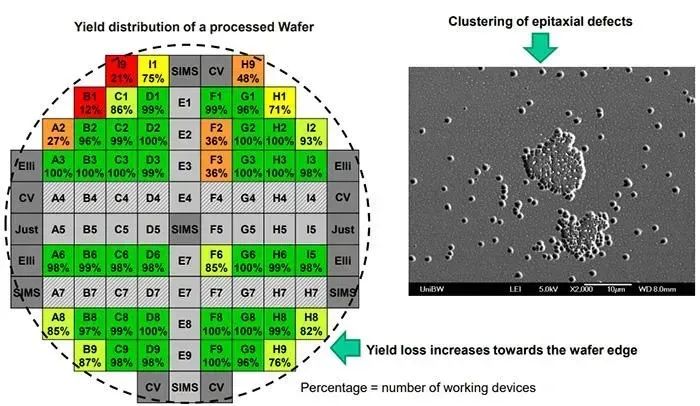

圖片來自:Google

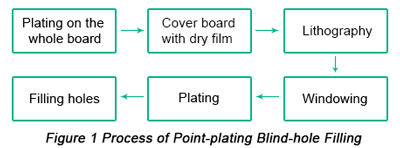

講到這,我們不難發(fā)現(xiàn):隨著半導體封測技術(shù)的不斷發(fā)展,芯片引腳數(shù)量的增多和密度的增強是一個普遍的趨勢。

這是由于現(xiàn)代芯片需要支持更多的功能和更復雜的系統(tǒng)架構(gòu),因此需要更多的引腳來實現(xiàn)信號傳輸、電源供應、地線連接、調(diào)試測試等功能。

同時,由于芯片尺寸的縮小和集成度的提高,芯片引腳的間距也越來越小,密度也越來越高。

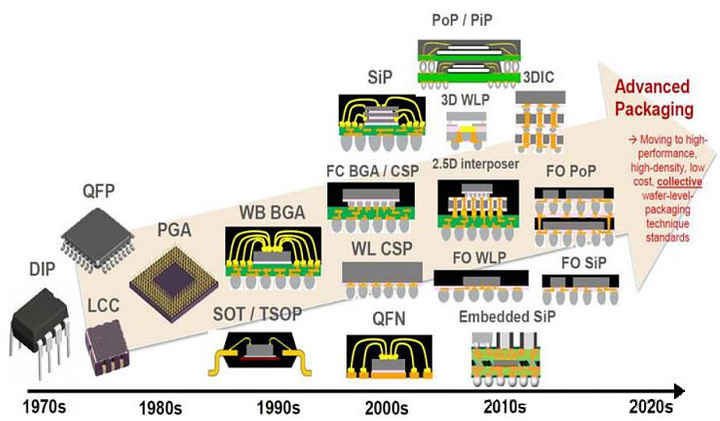

再者,為了滿足高引腳數(shù)量和高密度的封裝需求,半導體封測技術(shù)不斷進行創(chuàng)新和發(fā)展。

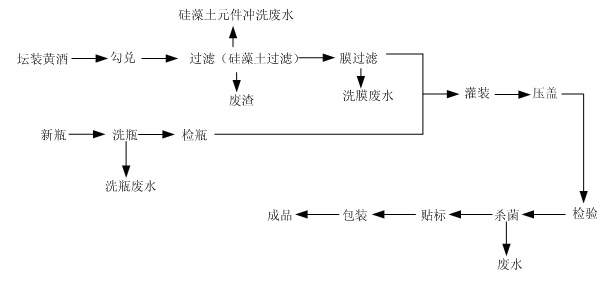

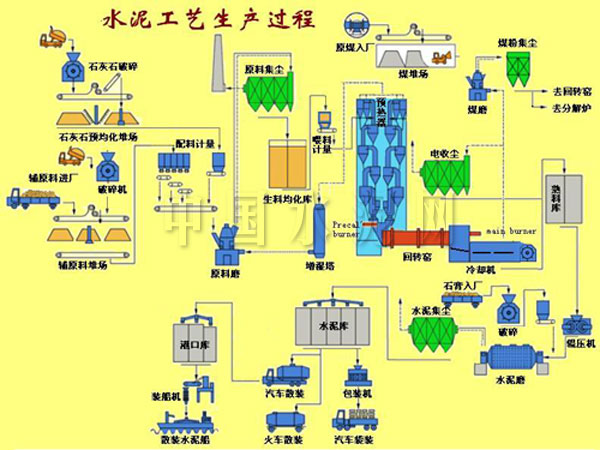

其中,封測技術(shù)運用功不可沒:

其一,新型封裝技術(shù)能夠?qū)崿F(xiàn)更高密度的引腳布局,如球柵陣列(BGA)、無引腳封裝(WLP)、芯片尺寸縮小等,可以有效提高芯片的集成度和性能。

其二,高精度焊接技術(shù)能夠?qū)崿F(xiàn)更高密度的焊點布局,如微觀焊點、超細焊點等,可以提高芯片的可靠性和性能。

其三,高密度線路板技術(shù)能夠?qū)崿F(xiàn)更高密度的引腳布局和更復雜的電路結(jié)構(gòu),如多層線路板、高階互連等,可以滿足更高性能和更復雜的系統(tǒng)需求。

圖片為:封測技術(shù)發(fā)展路徑

與此同時,在后摩爾時代,Chiplet 設計方案與先進封裝技術(shù)互為依托,因此成為封測行業(yè)未來主要增量。

隨著半導體產(chǎn)業(yè)鏈正向中國大陸遷移,亞太地區(qū)封測新產(chǎn)能不斷擴張。

封測已成為我國半導體領(lǐng)域的強勢產(chǎn)業(yè),長電與通富強勢布局 Chiplet 先進封裝高端賽道,目前均可實現(xiàn)量產(chǎn)。

需要注意的是,20世紀70年代半導體產(chǎn)業(yè)在美國形成規(guī)模,美國一直保持著全球半導體產(chǎn)業(yè)第一的地位,而后重心向日本遷移;20世紀90年代到21世紀初,半導體產(chǎn)業(yè)重心向中國臺灣和韓國遷移。

目前全球正經(jīng)歷半導體產(chǎn)業(yè)鏈重心轉(zhuǎn)移至中國大陸的第三次遷移,將為我國集成電路實現(xiàn)國產(chǎn)替代提供良好機遇。

尤其,應對封測市場波動期,Chiplet或?qū)⒊申P(guān)鍵:

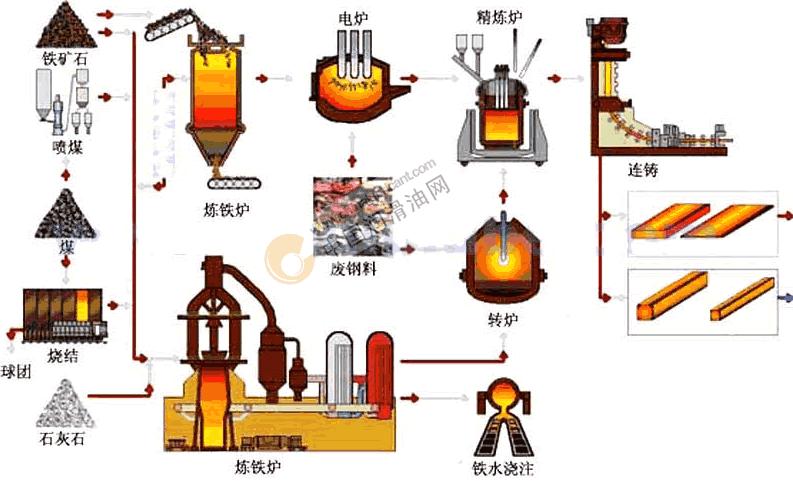

由于封測處于半導體產(chǎn)業(yè)鏈的后端,在市場波動期中也會有滯后性。

因此,業(yè)內(nèi)普遍認為,2023年或許才是封測產(chǎn)業(yè)正式迎來波動期的一年。

據(jù)IC Insight數(shù)據(jù)顯示,2023年全球封測市場將下降到6040億美元,同比2022年下降約5%。

圖片來自:IC Insight

但,當下可知的事:先進封裝技術(shù)亦成為國內(nèi)芯片廠商突破先進制程升級受阻逆境的重要途徑。國內(nèi)領(lǐng)先封測企業(yè)長電科技與通富微電積極布局Chiplet 先進封裝平臺研發(fā),目前均可實現(xiàn)量產(chǎn)。

寫在文章最后:

放眼未來,半導體技術(shù)不斷發(fā)展,芯片封測領(lǐng)域正面臨著諸多挑戰(zhàn)和機遇。

新型封裝技術(shù)如3D封裝、多芯片封裝等不斷涌現(xiàn),為提高產(chǎn)品性能和降低成本提供了新的可能;當然,測試技術(shù)的進步也在助力提高芯片的可靠性和性能。

其次,封測產(chǎn)業(yè)的智能化、自動化、綠色化等趨勢也將推動半導體封測進入新的發(fā)展階段;

編輯:黃飛

?

電子發(fā)燒友App

電子發(fā)燒友App

評論