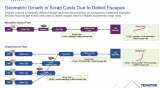

盡管整體經濟不景氣,但先進封裝市場繼續保持彈性。

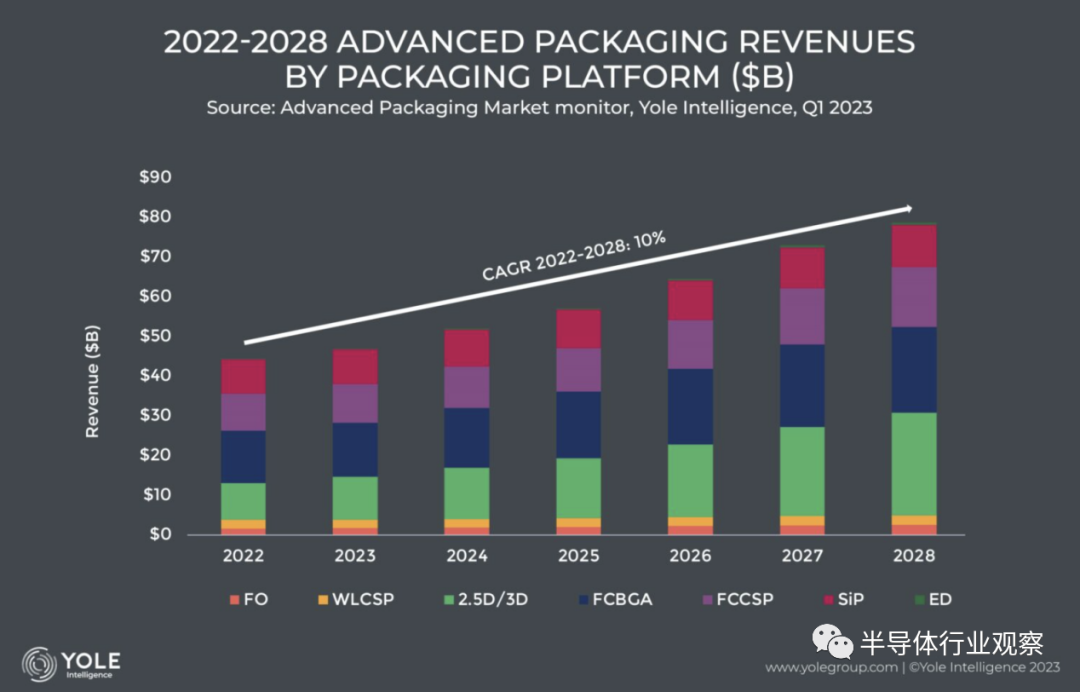

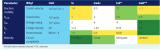

根據Yole Group最新的報道,與上一年相比,2022 年的收入增長了約 10%。2022年價值443億美元,預計2022-2028年復合年增長率(CAGR)為10.6%,到2028年達到786億美元。

報告進一步指出,用于將芯片與更先進節點集成的高端性能封裝預計到2028年將超過160億美元,占先進封裝領域的20%以上。在不同的先進封裝平臺中,2.5D/3D 增長最快,2022 年至 2028 年的 CAGR 接近 40%。它是分析和開發最多的技術之一,收入占比較大。

在日前舉辦的 ECTC(電子元件和技術會議)上,Yole的分析師分享了對先進封裝未來發展的一些看法。

Chiplet和異構集成徹底改變了先進封裝

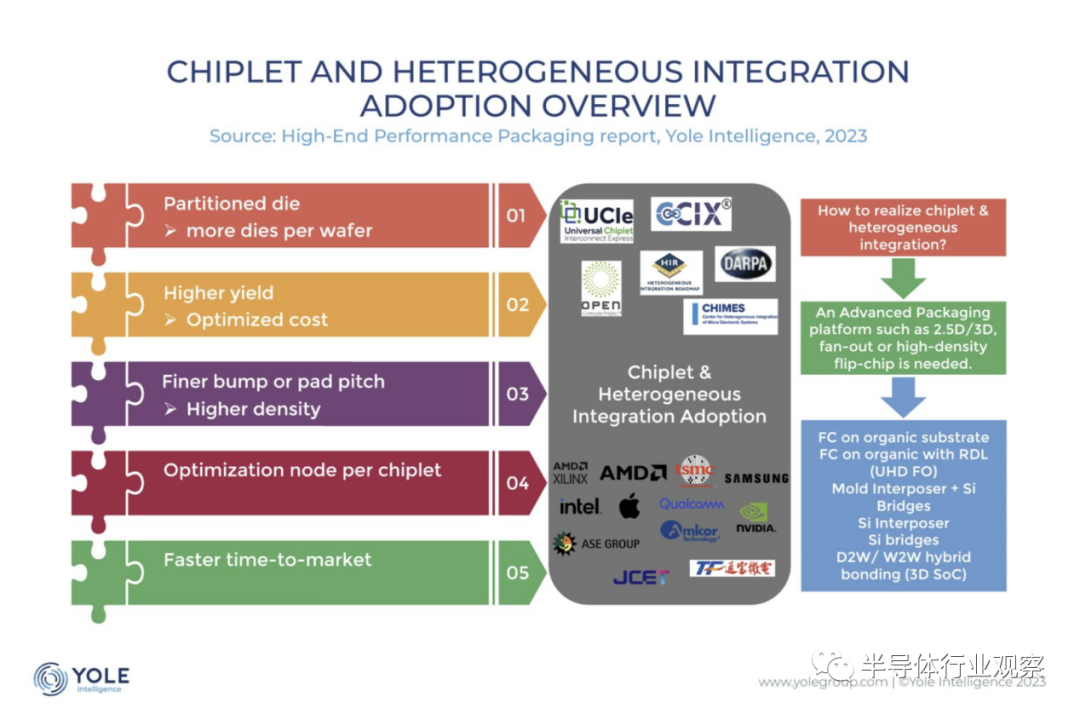

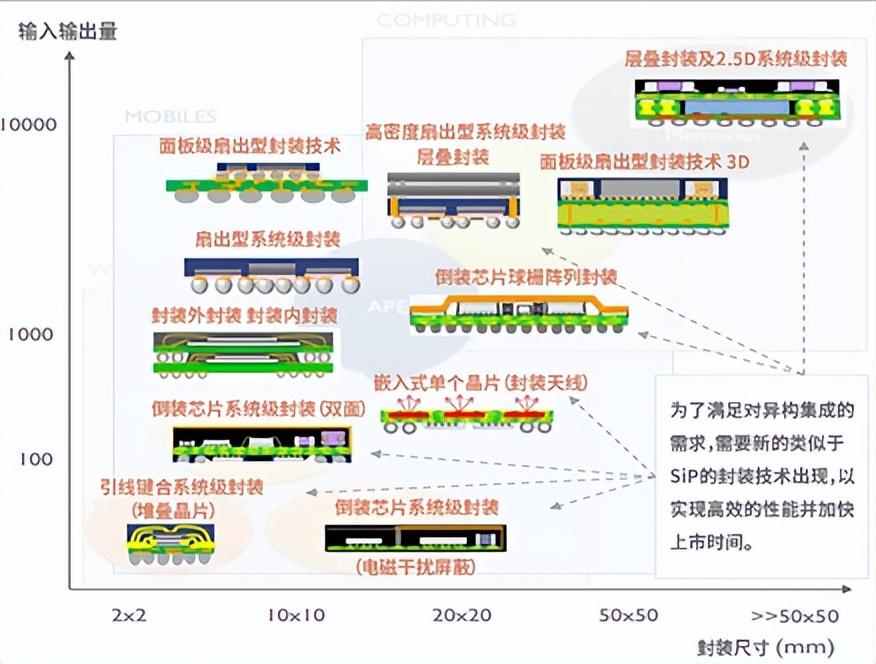

在Yole看來,隨著摩爾定律的放緩以及前沿節點復雜性和成本的增加,先進封裝正在成為將多個裸片集成到單個封裝中的關鍵解決方案,并有可能結合成熟和先進的節點。異構集成和基于小芯片的方法在人工智能、網絡、自動駕駛、高端 PC 和高端游戲等細分市場中變得必不可少。通過先進封裝技術實現的異構集成可在緊湊的平面中實現具有成本效益的多芯片集成,與傳統封裝相比也可實現更卓越的性能。

在封裝內集成更多數量的有源電路是一種通過密集互連將不同功能分配到集成到同一封裝中的不同芯片的方法。上市時間也縮短了,因為芯片可以來自不同的制造商并進行組裝。

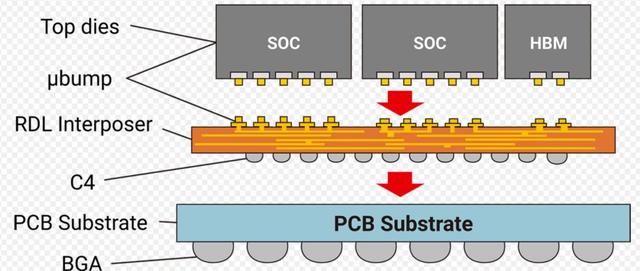

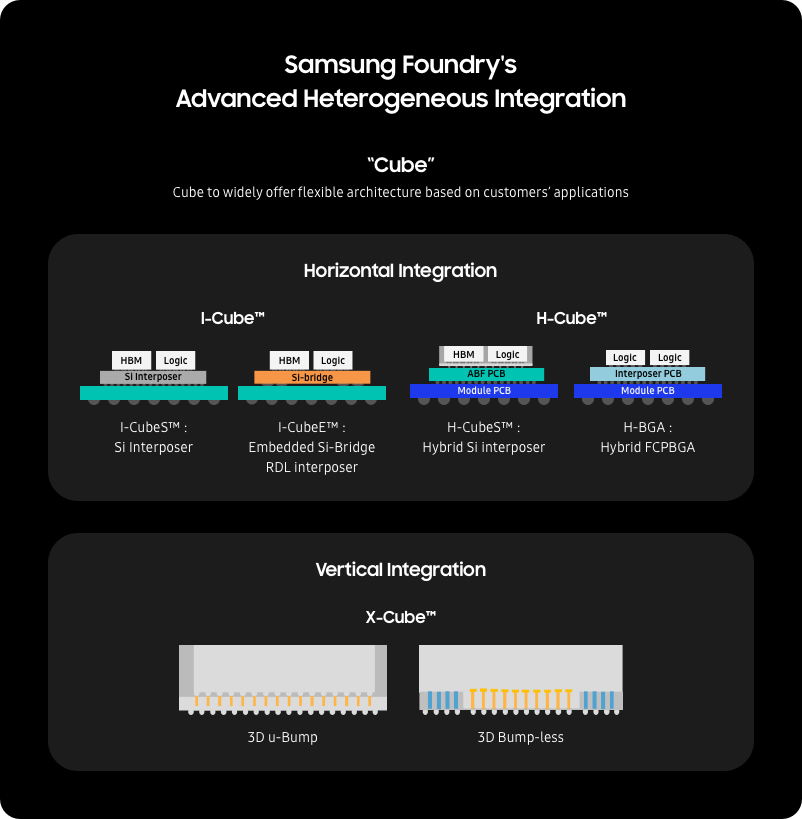

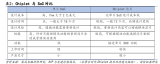

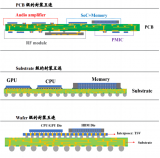

Octopart在一篇文章中則透露,要制造基于小芯片的產品,您需要設計技能、裸片、裸片之間的連接以及生產策略。chiplet封裝技術的性能、價格和成熟度對chiplet的應用有著實質性的影響。根據連接介質和方式的不同,用于chiplet互連的封裝技術可分為三類:基板封裝(Substrate packaging)、硅中介層封裝(Silicon-interposer packaging)、再分布層 (RDL:Redistribution-layer ) 封裝以及嵌入式多芯片互連橋 (EMIB:Embedded multi-die interconnect bridge )。

首先看基板封裝。流行的基板選擇是有機材料,因為這些材料很容易獲得。與傳統 PCB 類似,布線連接是通過蝕刻工藝完成的,該工藝獨立于半導體制造中使用的其他工藝。這是最著名的 2D 異構集成的最早化身。

通過倒裝芯片設計或堆疊,可以輕松地將多個裸片高密度地連接到基板上。此外,與之相關的材料和制造成本極低,因為該技術不依賴于芯片制造工藝。使用這種技術的主要缺點是 I/O 引腳密度低,從而限制了這些封裝中互連的帶寬。

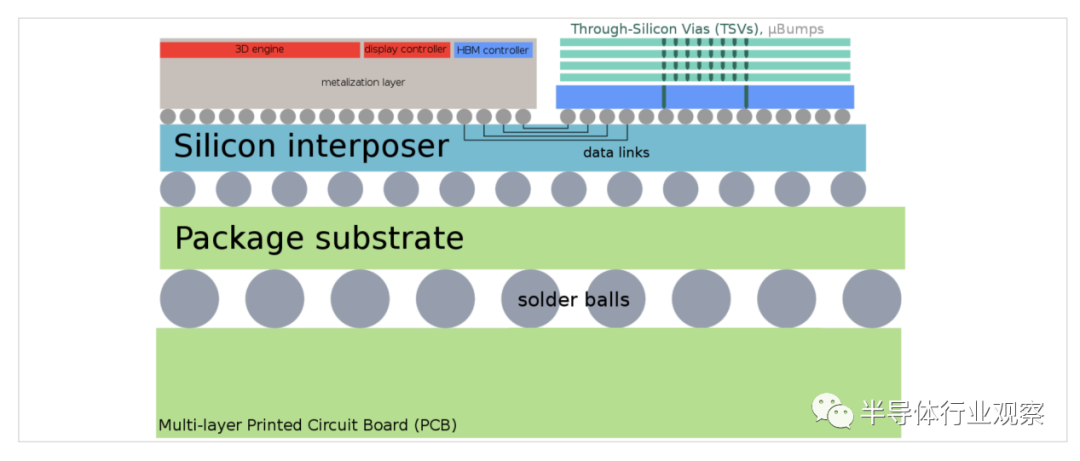

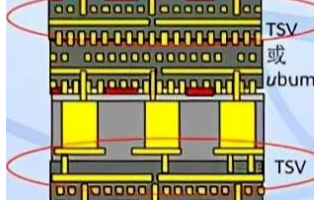

其次看硅中介層封裝,該技術涵蓋 2.5D 和 3D 封裝技術,芯片在中介層上橫向構建 (2.5D) 或垂直堆疊 (3D)。為了實現裸片之間的互連和通信,將硅中介層放置在基板和裸片之間。中介層就像一個微型印刷電路板,本質上是為小芯片之間的電連接提供基板。互連結構由金屬觸點(稱為微凸塊)和在封裝內部運行的硅通孔 (TSV) 構成。這些用于將裸片連接到中介層,并將中介層連接器連接到具有 BGA 焊盤圖案的封裝基板。

這些產品具有更高的 I/O 密度、更低的功耗和更低的傳輸延遲。這是通過微凸塊和 TSV 之間更小的走線長度和間距實現的。該技術的唯一顯著缺點是制造成本增加。

再看RDL封裝技術,再分布層 (RDL) 封裝技術不使用基板,而是將電介質和金屬直接沉積在晶圓的頂面上。該技術也稱為“扇出”技術。為了承載線路設計,構建了一個重新分布層,使得每個小Chiplet上的 I/O 端口圍繞設備成形。通過縮短電路的長度,RDL 提供更高的信號完整性(更低的損耗和失真)。

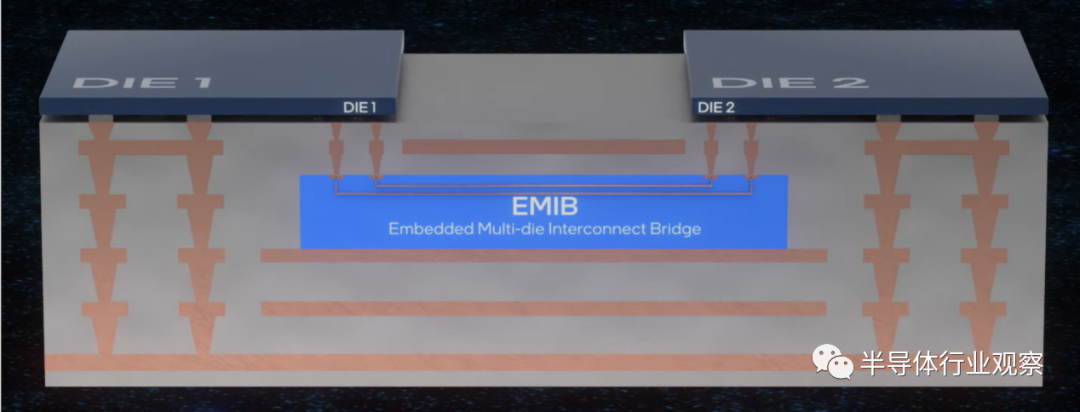

至于EMIB ,則是一種使用嵌入有機材料中的薄硅晶片部分作為芯片到芯片互連基板的技術。高級產品成本較高的問題可以通過使用具有不同Chplet的橋接封裝來解決。這種混合封裝技術是基于基板和基于中介層的封裝的組合。通常小于 75 微米的薄硅層被涂在基板上并用于形成芯片間連接,這些層嵌入有機基板層中。

該概念遵循 HDI PCB 中使用的 ELIC 中的相同想法,其中每層互連結構將多個芯片連接到絕緣(有機)基板中的內層。封裝的 EMIB 部分是一個硅橋,可在小芯片之間提供高帶寬連接。

混合鍵合無處不在

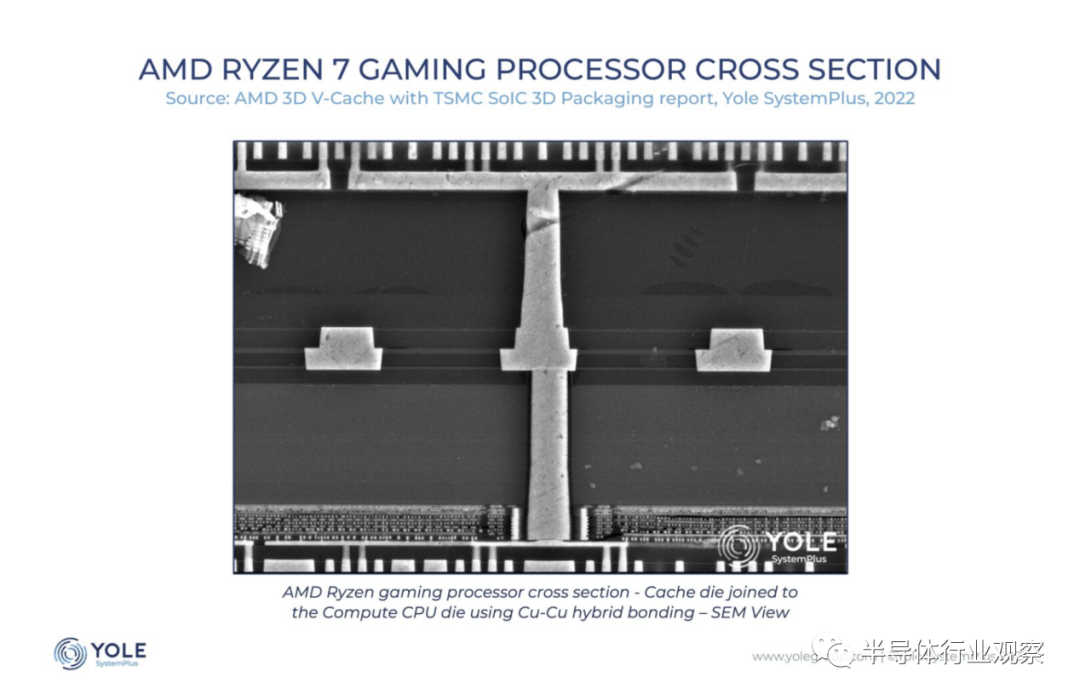

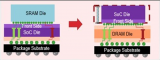

Yole在文章中強調,ECTC 的幾個會議專門討論了混合鍵合(hybrid bonding)。在他們看來,該技術正在成為異構集成和小芯片空間內組裝技術進步的關鍵,因為它允許在封裝內高密度垂直堆疊不同的芯片。

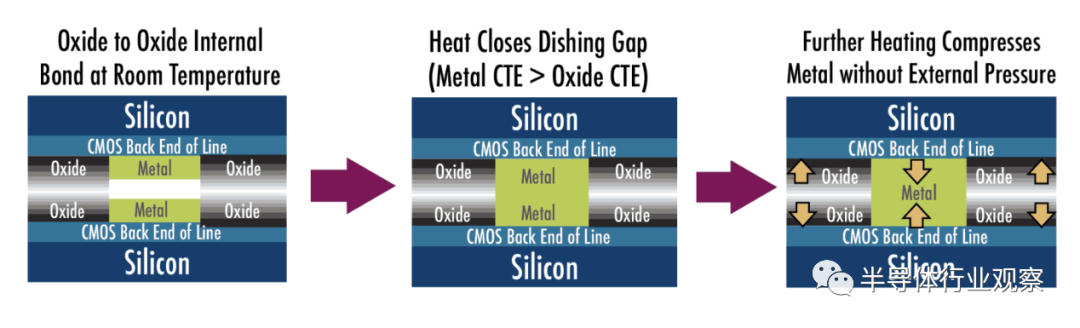

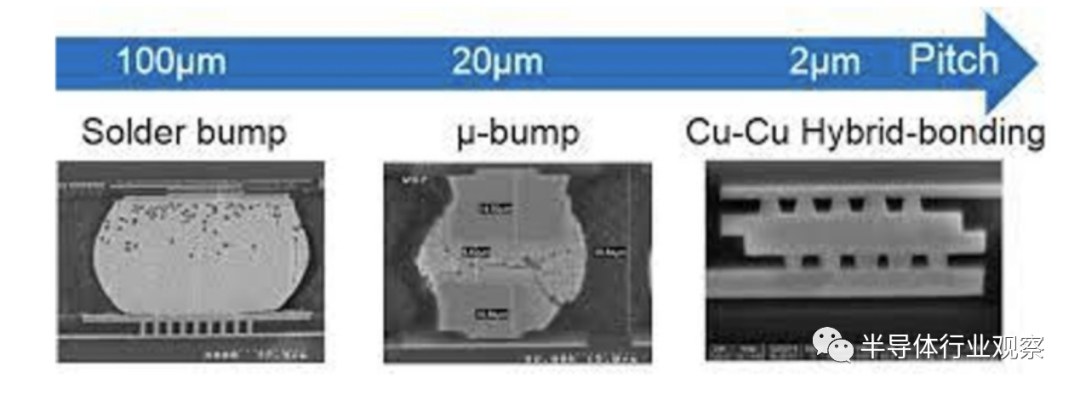

混合鍵合可以是晶圓到晶圓(wafer-to-wafer)、裸片到晶圓(die-to-wafer)或裸片到裸片(die-to-die)。其主要優勢在于,它允許 3D 器件堆疊以實現垂直縮放和比其他芯片堆疊技術更高的互連密度。它的另一個特點是細間距鍵合導致更高的互連密度。這也增加了系統帶寬和功率效率。速度也有所提高,因為傳統的凸點被消除,而是使用直接的銅對銅鍵合。這形成了非常緊密的互連,并且由于焊盤是芯片結構的一部分,因此提高了鍵合強度和可靠性。

在BrewerScience看來,混合鍵合是開創先進封裝創新未來的關鍵。因為混合鍵合提供了一種解決方案,可以實現更高的帶寬以及更高的功率和信號完整性。由于業界正在尋求通過擴展系統級互連來提高最終設備的性能,因此混合鍵合提供了最有前途的解決方案,能夠將多個裸片與小于 10 μm 的小互連間距集成在一起。

而要了解混合鍵合的基礎知識,則需要問三個基本問題:什么是混合鍵合、為什么要使用混合鍵合以及哪種材料最適合您的應用?

BrewerScience表示,當電子封裝行業發展到三維封裝時,微凸塊通過使用裸片上的小銅凸塊作為晶圓級封裝的一種形式來提供芯片之間的垂直互連。凸塊的尺寸范圍從 40 μm 間距到最終縮小到 20 μm 或 10 μm 間距。但是,這就是問題所在;縮小超過 10μm 變得非常具有挑戰性,工程師們正在轉向一種新的解決方案來繼續縮小尺寸。混合鍵合通過完全避免使用凸塊為 10 μm 及以下間距提供解決方案,而是使用小型銅對銅連接來連接封裝中的裸片。它提供卓越的互連密度,支持類似 3D 的封裝和高級內存立方體。

“混合鍵合是一種永久性鍵合,它將介電鍵合 (SiOx) 與嵌入金屬 (Cu) 相結合以形成互連。它在整個行業被稱為直接鍵合互連 (DBI) 。混合鍵合擴展了在鍵合界面中嵌入金屬焊盤的融合鍵合,允許晶圓的面對面連接。”BrewerScience強調。

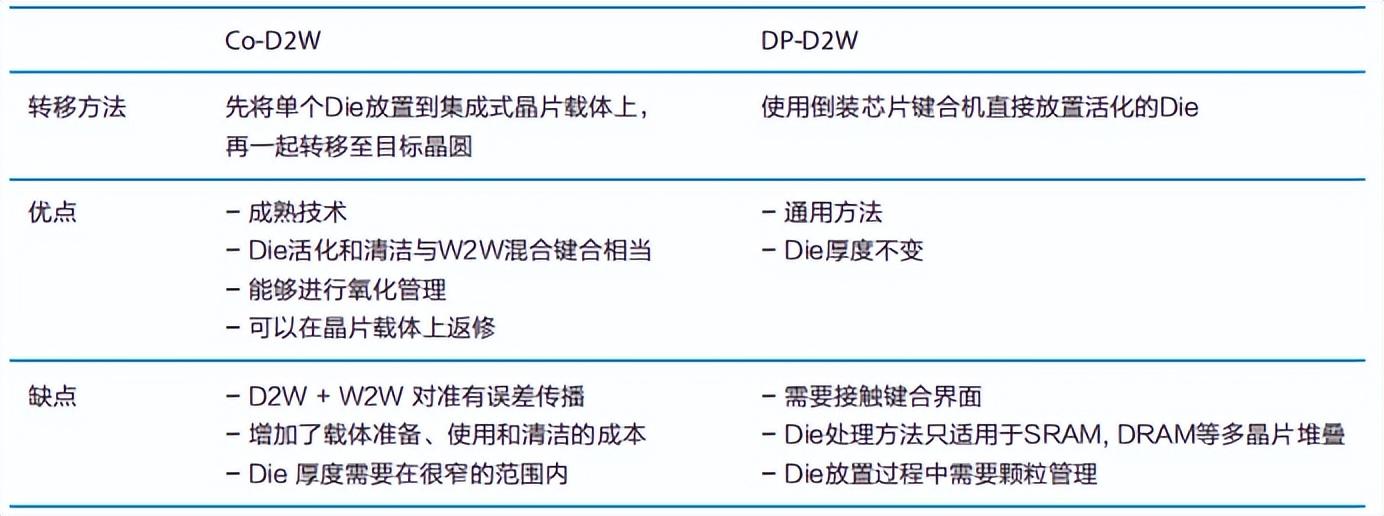

因為混合鍵合通過緊密間隔的銅焊盤垂直連接裸片到晶圓(D2W) 或晶圓到晶圓 (W2W)。雖然 W2W 混合鍵合已在圖像傳感領域投入生產多年,但業界仍大力推動 D2W 混合鍵合的發展。這種發展將進一步實現異構集成,它提供了一種強大而靈活的方式來直接連接不同功能、尺寸和設計規則的芯片。

與其他鍵合技術相比,混合鍵合具有許多優勢,包括:允許高級 3D 設備堆疊、最高 I/O實現10 μm以下的鍵合間距、更高的內存密度、擴展帶寬、增加功率、提高速度效率、消除顛簸的需要,在沒有功率和信號損失的情況下提高性能。

不過ECTC上的一些發言者則談到了可以改進混合鍵合技術的發展,例如提高鍵合強度。良品率也有提升空間。污染問題也會影響混合鍵合;雖然污染風險并不比其他技術高,但由于間距小,顆粒阻止傳播的影響更大。

玻璃,正在成為封裝材料新選擇

除了新技術,ECTC 還討論了新材料。其中,玻璃正在成為可用于封裝的關鍵材料之一。它具有許多優點,例如高導熱性、機械強度、低介電常數和低介電損耗。它還能夠創建細線和空間,允許小間距,并且 CTE(熱膨脹系數)比通常用于封裝的其他有機材料更接近硅。

這種材料也已經在 RF、HPC、光子學和 CPO(共同封裝光學)應用中變得流行起來。

ECTC 與會者看到了圍繞玻璃基板和玻璃中介層的發展,包括佐治亞理工學院與玻璃供應商和 IC 基板供應商密切合作以開發可靠和高性能的解決方案。正在開發的一個領域是玻璃芯基板( glass core substrates),以取代傳統 IC 基板的有機芯(organic core)。這主要可用于 HPC 和 RF 應用程序。

除了與硅相比成本更低之外,玻璃還有許多優點。它允許將芯片集成到大型封裝中,同時提供更好的平整度,這對于 HPC 和 AI 應用程序至關重要。當頻率超過 5G 時,其低介電常數將至關重要,屆時 6G 和 7G 將再次提高頻率。

使用玻璃芯構建 IC 基板和用玻璃替代硅中介層的挑戰與玻璃的重量以及核心周圍的玻璃和有機層之間的 CTE 差異有關,這可能會影響封裝的可靠性。另一個問題是,構建跡線( build traces)的金屬化工藝比硅更難。然而,這是一個相對較小的問題,而且很可能會得到解決。

日本材料供商 Hoya 以及美國的 Corning 和 Schott 等公司都有興趣進入該領域。

據一篇題為《Leveraging Glass Properties for Advanced Packaging》的論文介紹,玻璃為先進封裝提供了許多機會。最明顯的優勢是材料特性。作為絕緣體,玻璃具有低電損耗,尤其是在高頻下。相對較高的剛度和調整熱膨脹系數的能力為管理玻璃芯基板和玻璃通孔 (TGV) 和載體應用的粘合堆疊中的翹曲提供了優勢。玻璃還為開發具有成本效益的解決方案提供了優勢。玻璃成型工藝有可能形成面板格式以及低至 100 微米的厚度,從而有機會優化或消除當前的制造方法。

玻璃具有許多特性,使其成為各種包裝應用中令人興奮的材料。相對于硅,玻璃的電氣性能降低了電損耗。這在高頻下變得更加重要,這是下一代移動技術可能采用的路徑。重要的意義在于能夠在保持電池壽命的同時增加智能手機的功能。

調整材料屬性(如 CTE)極大地促進了使用玻璃作為多種形式的 2.5D 和 3D 應用的 TGV 基板。此外,以薄而大的高質量玻璃板形成玻璃的能力使許多機會能夠實現成本效益。正在展示為有效加工超薄玻璃提供手段的處理技術。

良好成型的通孔和盲孔的形成已經得到證明,并且可以利用現有的金屬化技術在晶圓和面板形式的玻璃中產生非常好的 Cu 填充性能。玻璃中銅填充通孔的可靠性能已得到證明。這些發展使玻璃成為下一代包裝應用的令人興奮的材料。

但是,迄今為止,還沒有大批量生產,玻璃在封裝中的集成在未來幾年內不太可能,因為一些持續存在的挑戰仍需要解決。不過,據報道,玻璃基板供應商 Absolics 有望開始小批量生產今年晚些時候或 2024 年初生產玻璃芯 IC 基板。

共同封裝光學 (CPO) ,正在成為現實

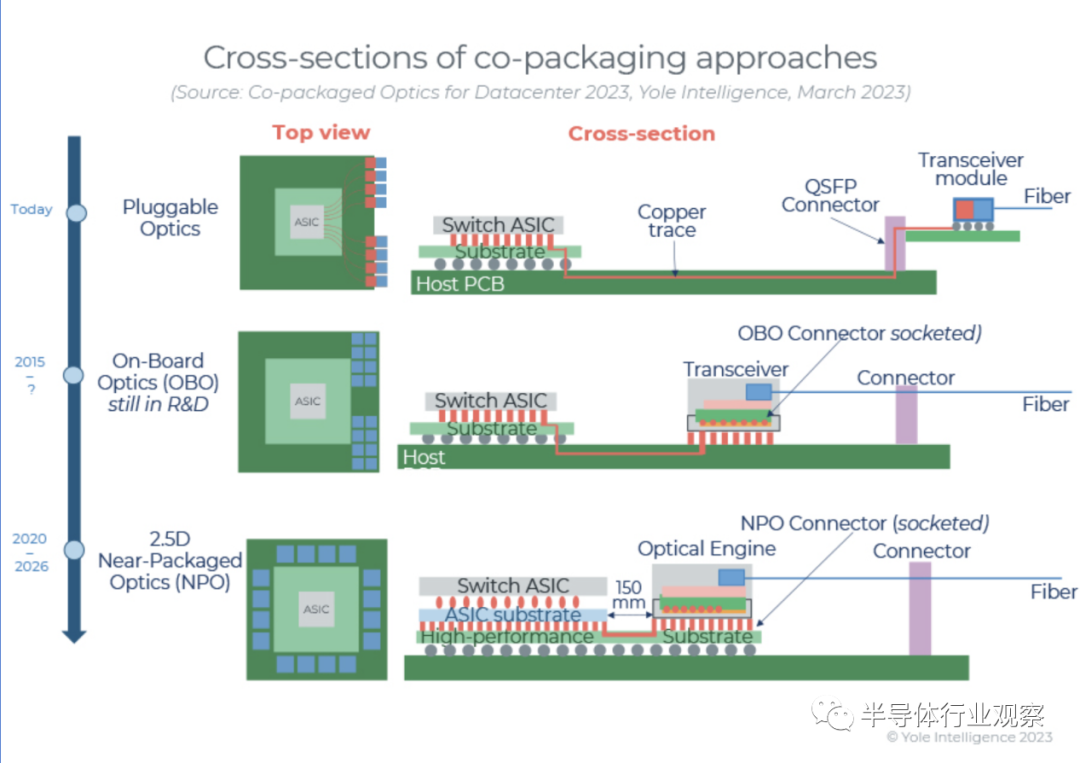

據Yole報道,在封裝領域,大家關注的另一個趨勢 CPO 與網絡和數據中心市場相關,在這些市場中,對帶寬增加的需求正在推動光子互連的發展,以提高速度和降低功耗。

CPO 是封裝電子產品和光子芯片,例如與光子芯片互連的 ASIC 或 CMOS 芯片。在這一領域,公司進行了合作:ECTC 上有來自網絡和數據中心、芯片供應商、代工廠、OSAT、研發機構和材料供應商的演示。許多人正在關注先進的基板,其中兩個芯片之間的互連是通過 IC 基板實現的。

Yole表示,在過去的 50 年里,移動技術創新每十年推出一次。移動帶寬需求已從語音通話和短信發展到超高清 (UHD) 視頻和各種增強現實/虛擬現實 (AR/VR) 應用。盡管 COVID-19 爆發對電信基礎設施供應鏈產生了深遠影響,但全球消費者和企業用戶繼續創造對網絡和云服務的新需求。社交網絡、商務會議、超高清視頻流、電子商務和游戲應用程序將繼續推動增長。

每個家庭和人均連接到互聯網的設備的平均數量正在增加。隨著具有更高功能和智能的新數字設備的出現,Yole觀察到每年都有更高的采用率。此外,智能電表、視頻監控、醫療保健監控、連接驅動器和自動化物流等機器對機器應用的擴展顯著促進了設備和連接的增長,并推動了數據中心基礎設施的擴展。

由于預算削減,共同封裝光學 (CPO) 社區面臨困難時期,因為可插拔器件(pluggables)已經可以實現 CPO 承諾的成本節約和低功耗。CPO 的全面部署只會在可插拔功能用盡時才會發生。至少在接下來的兩代開關系統中,很難與可插拔模塊競爭,而可插拔模塊在很長一段時間內仍將是首選。CPO 最近因其在數據中心 (DC) 中的網絡能效而受到廣泛關注。Yole的分析表明,與 DC 的總功耗相比,網絡節省的功耗可以忽略不計。只有 Broadcom、Intel、Marvell 和其他一些 CPO 參與者會將專有解決方案推向市場。為了滿足市場需求并讓最終用戶相信 CPO 的可行性,

隨著 6.4T 光模塊的到來,CPO 和可插拔光學器件之間的激烈競爭可能會在 2029 年到來。屆時 CPO 系統中的多個技術障礙有望得到解決。然而,收發器行業不斷致力于創新以推動可插拔光學市場。在 CPO 系統實現網絡應用的批量出貨之前,可插拔將采用聯合封裝方式,光學引擎將在高性能計算和未來分解系統中獲得更多普及。圍繞機器學習 (ML) 系統供應商 Nvidia 和 HPE 的包括 Ayar Labs、Intel、Ranovus、Lightmatter、AMD、GlobalFoundries 等在內的工業生態系統取得了不錯的進展,計劃在 2024 年至 2026 年之間實現產品的批量出貨.

Yole預計, 800G 和 1.6T 可插拔模塊會很受歡迎,因為它們利用 100G 和 200G 單波長光學器件,因此可以在 QSFP-DD 和 OSFP-XD 外形規格中以技術和成本效益的方式實施。就所需的電氣和光學密度、熱管理和能源效率而言,可插拔外形規格支持 6.4T 和 12.8 容量的能力將受到限制。由于采用分立式電氣設備,功耗和熱管理正成為未來可插拔光學器件的限制因素。使用硅光子技術平臺的共同封裝旨在克服上述挑戰。

Yole進一步指出,如今,光可插拔模塊市場供應鏈已經完善。它包括分立或集成組件供應商、生產發射器和接收器光學子組件(TOSA 和 ROSA)的光學公司、多路復用器、數字信號處理器 (DSP) 和 PCB,以及組裝/測試集成商。在這樣的多供應商市場模型中,涉及許多不同的供應商。此外,一個開關盒中多個不同可插拔模塊的互操作性有助于行業的靈活性。這些是目前優于 CPO 的主要優勢,后者將嚴重依賴硅光子學。憑借高度集成的光學和硅芯片,將非常需要新的工程能力和代工廠,這對于傳統的中型企業來說是無法接受的。

但Yole也直言,盡管高端CPO解決方案的主流部署主要針對大型云運營商,但仍有大量規模較小的企業數據中心尚未采用最新的互連技術,因此技術交流較多慢點。這意味著,即使 CPO 成為主流技術,可插拔模塊在 CPO 在技術上或經濟上不可行的幾個應用中仍將有很高的需求,例如長途應用和邊緣數據中心。為此Yole預計可插拔技術在未來 10 年內不會被淘汰。然而,可插拔光學行業可能會整合,而 CPO 市場將形成多供應商商業模式。

未來的努力和挑戰

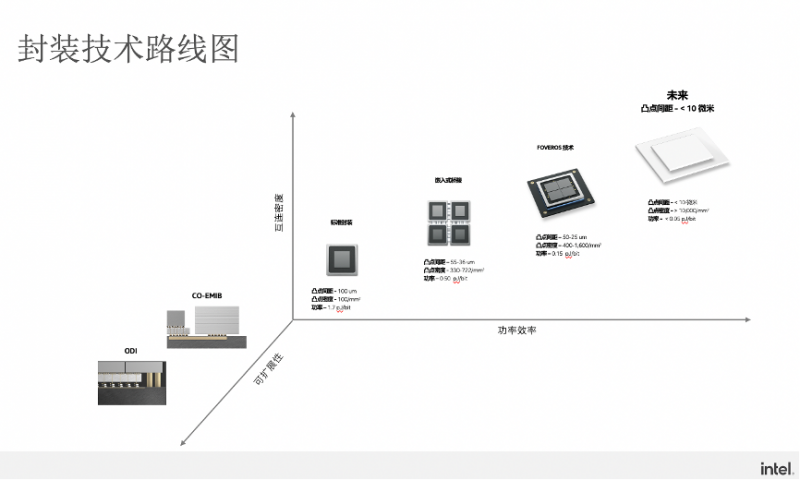

據Yole介紹,在ECTC上,大家還談論了一些介紹涉及扇出型封裝方法,而其他人則研究了玻璃基板。此外,還討論了多種互連技術。微凸塊、TSV、RDL、硅橋和硅中介層都在經歷技術改進。

Yole重申,在過去幾年中,半導體供應鏈受到了 Covid-19、芯片和材料短缺等情況打擊。這在各個方面造成了破壞,并開始促使地方政府投資于本土半導體生產。

在 ECTC,他們討論了 CHIPS 法案將先進封裝引入北美的努力。觀察到本土供應鏈不同要素之間的強大協作和伙伴關系,其中包括設計、設備制造商、材料和設備供應商、研發機構甚至 OSAT。

除了在美國開展更先進的包裝研發活動外,目標之一是支持從研發到制造和商業化的遷移,但公司一致認為需要更多的潔凈室空間,這需要基礎設施投資。這也需要時間。在美國,高昂的勞動力成本、技能短缺和資金需求仍然阻礙著國內供應鏈的發展。在歐洲,同樣的因素也適用。

高級封裝支持的異構集成是由于當今生產高級前端節點成本更高、難度更大這一事實所驅動的。從歷史上看,封裝是一個 OSAT 業務,它們在這個領域仍然非常重要,但是臺積電和 IDM(例如三星和英特爾),在過去十年中提出了先進的后端解決方案,并利用它們的前端能力來實現2.5D 或 3D 解決方案,例如硅中介層、硅橋和混合鍵合。

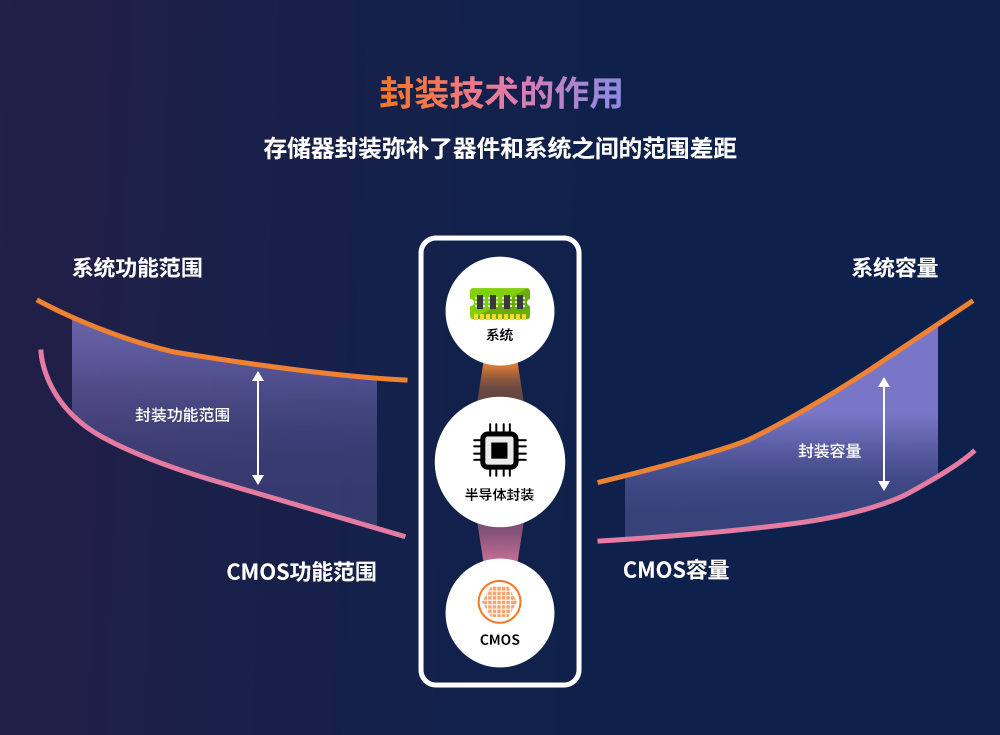

滿足數字化、AI 興起以及網絡、5G 和自動駕駛汽車日益增長的需求的系統要求的性能水平不能僅通過減少硅節點來滿足,因為相關的成本和產量損失。因此,注意力集中在高級封裝上,以將來自高級或成熟節點的管芯集成在一起,以降低系統成本。

先進封裝,特別是高端性能封裝將依賴于克服將多個裸片放置在同一封裝中、提高裸片之間的間距、互連密度和帶寬方面的挑戰。因此,該行業正在尋求異質集成和混合鍵合,同時也在研究具有成本效益和改進性能的新材料以及 CPO 等新技術,以將先進封裝提升到一個新的水平,以滿足下一代的性能需求。

編輯:黃飛

電子發燒友App

電子發燒友App

評論