CEA -Leti和英特爾今天宣布了一項(xiàng)聯(lián)合研究項(xiàng)目,旨在開發(fā) 300 毫米晶圓上二維過渡金屬二硫化物 (2D TMD) 的層轉(zhuǎn)移技術(shù),目標(biāo)是將摩爾定律擴(kuò)展到 2030 年以后。

二維層狀半導(dǎo)體,例如基于鉬和鎢的 TMD,有望擴(kuò)展摩爾定律并確保 MOSFET 晶體管的最終縮放,因?yàn)?2D-FET 提供了固有的亞 1nm 晶體管溝道厚度。由于其良好的載流子傳輸和移動(dòng)性,即使對(duì)于原子級(jí)薄層,它們也適用于高性能和低功耗平臺(tái)。此外,它們的器件主體厚度和適度的能帶隙導(dǎo)致增強(qiáng)的靜電控制,從而導(dǎo)致低斷態(tài)電流。

這些特性將 2D-FET 堆疊納米片器件定位為 2030 年后晶體管縮放的有前途的解決方案,這將需要高質(zhì)量的 2D 通道生長、適應(yīng)性轉(zhuǎn)移和穩(wěn)健的工藝模塊。為此,這個(gè)多年期項(xiàng)目將開發(fā)一種可行的層轉(zhuǎn)移技術(shù),將高質(zhì)量二維材料(生長在 300 毫米首選基板上)轉(zhuǎn)移到另一個(gè)用于晶體管工藝集成的器件基板。英特爾為該項(xiàng)目帶來了數(shù)十年的研發(fā)和制造專業(yè)知識(shí),CEA-Leti 還提供了鍵合和傳輸層專業(yè)知識(shí)以及大規(guī)模表征。

英特爾技術(shù)開發(fā)高級(jí)研究員兼英特爾歐洲研究總監(jiān) Robert Chau 表示:“隨著我們不懈地推動(dòng)摩爾定律,2D TMD 材料是一種很有前途的選擇,可以在未來擴(kuò)展晶體管的縮放極限。” “該研究計(jì)劃的重點(diǎn)是開發(fā)一種可行的基于 2D TMD 的 300mm 技術(shù),用于未來的摩爾定律晶體管縮放。”

英特爾將其在半導(dǎo)體和封裝研究與技術(shù)方面的實(shí)力和專業(yè)知識(shí)與歐洲合作伙伴合作,以開發(fā)摩爾定律創(chuàng)新并推動(dòng)歐洲的微電子技術(shù)發(fā)展。2022 年,Chau 從美國調(diào)往歐洲,領(lǐng)導(dǎo)英特爾歐洲研究院,并與歐洲大陸的合作伙伴一起推動(dòng)英特爾的研發(fā)。英特爾和 CEA-Leti 在半導(dǎo)體設(shè)計(jì)、工藝和封裝技術(shù)方面有著長期的密切合作。

最近,他們宣布在 2022 年 6 月使用自組裝工藝實(shí)現(xiàn)未來芯片集成的新型芯片到晶圓鍵合技術(shù)的研究取得突破。Chau 于 6 月 16 日訪問了 CEA-Leti 的格勒諾布爾總部,以強(qiáng)調(diào)其重要性他們的合作和項(xiàng)目的啟動(dòng),一直是兩個(gè)實(shí)體之間多年研究合作的有力支持者。

CEA-Leti 首席執(zhí)行官 Sebastien Dauvé 表示,行業(yè)路線圖表明,二維材料將集成到未來的微電子設(shè)備中,而 300 毫米晶圓的轉(zhuǎn)移能力將是這種集成的關(guān)鍵。

“由于其超過 700°C 的高生長溫度和在首選基板上的高質(zhì)量生長,很難堆疊 2D 材料,很難像通常的薄層一樣沉積在堆疊上。因此,轉(zhuǎn)移最有希望將它們集成到未來的設(shè)備中,而 CEA-Leti 在這方面的優(yōu)勢(shì)在于其在轉(zhuǎn)移開發(fā)和表征方面的專業(yè)知識(shí)和技術(shù)訣竅,”Dauvé 說。

除了二維晶體管外,CFET 晶體管也是大家關(guān)注的一個(gè)方向,imec也在其上取得了新進(jìn)展。

邁向單片 CFET 晶體管

imec 主要技術(shù)成員 Hans Mertens表示:“今天,半導(dǎo)體行業(yè)正處于從 FinFET 到 Nanosheet 的過渡期,Nanosheet 是一種器件架構(gòu),將通過多代邏輯技術(shù)擴(kuò)展路線圖。在此過程中,我們可能會(huì)介紹 Forksheet,這是imec幾年前提出的一種先進(jìn)的納米片架構(gòu),它減少了相鄰器件之間的間隔,與傳統(tǒng)的納米片相比,提供了縮放和性能優(yōu)勢(shì)。到本世紀(jì)末,imec預(yù)計(jì) complementary FET (CFET) 將進(jìn)入路線圖。在該器件架構(gòu)中,n- 和 pMOS 器件相互堆疊,首次從標(biāo)準(zhǔn)單元高度考慮中消除了 np 分離。當(dāng)輔以先進(jìn)的技術(shù)來接觸晶體管時(shí),CFET允許逐漸推動(dòng)track高度從5T走向4T,有效地大幅縮小標(biāo)準(zhǔn)單元尺寸。

從工藝的角度來看,由于 nMOS-pMOS 垂直堆疊結(jié)構(gòu),CFET 制造具有挑戰(zhàn)性,我們正處于尋路的早期階段。已經(jīng)提出了幾種 CFET,包括單片(monolithic )和順序(sequential )工藝流程。在順序工藝流程中,頂層器件在底層器件頂部通過晶圓鍵合轉(zhuǎn)移覆蓋半導(dǎo)體層后按順序進(jìn)行處理。相反,單片集成涉及在單個(gè)基板上構(gòu)建垂直設(shè)備架構(gòu)。”

單片 CFET:引入 CFET 的最快途徑

imec 技術(shù)人員主要成員 Anne Vandooren 表示:“在我們的邏輯計(jì)劃中,imec 及其合作伙伴專注于單片 CFET 集成,因?yàn)榕c現(xiàn)有的納米片型工藝流程相比,這種集成方案的破壞性最小。因此,它被認(rèn)為是在行業(yè)相關(guān)維度上引入 CFET 的最快途徑。盡管如此,制造這兩種器件的層的垂直堆疊推動(dòng)了對(duì)高縱橫比圖案化、材料的選擇性沉積和去除以及高質(zhì)量(epi-)膜沉積的需求。此外,還需要引入一些 CFET 專用工藝模塊,以實(shí)現(xiàn)橫截面的柵極和接觸部分的垂直隔離。

我們通過將單片 CFET 集成挑戰(zhàn)劃分為不同的子項(xiàng)目來應(yīng)對(duì)這些挑戰(zhàn),并逐漸增加集成復(fù)雜性。每個(gè)子項(xiàng)目都建立在不同的測(cè)試工具上。我們首先關(guān)注單極單片 CFET,n 和 p 頂部和底部器件在不同晶圓上加工。其他測(cè)試車輛將在同一晶圓上加工單片 CMOS CFET 器件。它們的主要區(qū)別在于 CFET 器件的接觸方式,最終致力于實(shí)現(xiàn)先進(jìn)的中線 (MOL) 和背面連接選項(xiàng)。對(duì)于每個(gè)test vehicles,我們探索了各種工藝和集成選項(xiàng),權(quán)衡功率性能區(qū)域收益與復(fù)雜性。在每輛車上獲得的知識(shí)將轉(zhuǎn)移到下一輛車上。”

48nm 柵極間距的單極單片 CFET 演示

Hans Mertens:“在 VLSI 2020 上,imec 率先在 300mm 晶圓上展示了單片 CFET 器件,盡管采用的是 90nm 的‘relaxed’柵極間距(即接觸多晶硅間距 (CPP))。在 VLSI 2023 上,imec 展示了通過單片集成以行業(yè)相關(guān)的 48nm 柵極間距構(gòu)建的單極 CFET 器件。該作品入選 2023 VLSI 技術(shù)研討會(huì)亮點(diǎn)環(huán)節(jié)。我們的功能器件分別為 n- 和 pMOS 的底部和頂部器件顯示出出色的開關(guān)特性。我們目前正在探索以更小的柵極間距進(jìn)行單極單片 CFET 集成。

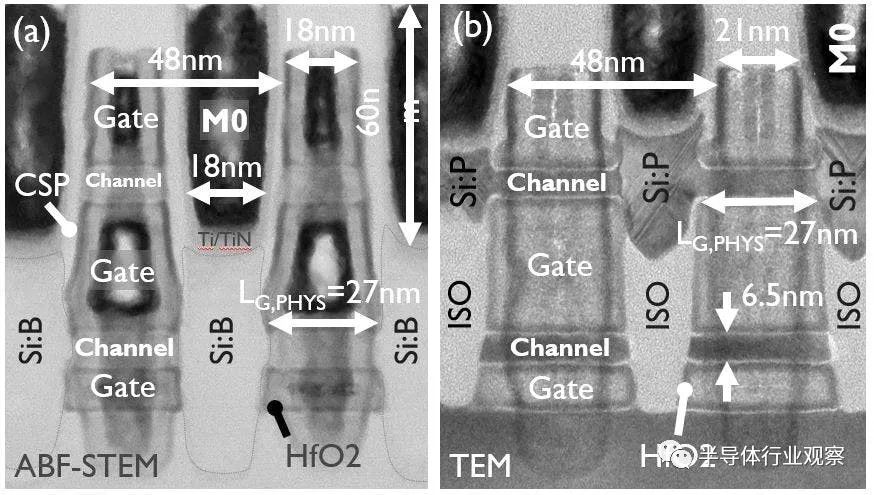

(a)底部 pFET 和 (b) 頂部 nFET (LG,PHYS=27nm)(在 VLSI 2023 上展示)的工藝結(jié)束橫截面圖像。

在此演示中,評(píng)估了底部或頂部器件的源極-漏極外延結(jié)構(gòu)(源極-漏極外延)和源極-漏極接觸。此外,為了限制縱橫比并加快開發(fā)速度,結(jié)構(gòu)的活性部分僅限于底部的一個(gè)納米片和頂部器件的一個(gè)。然而,這項(xiàng)工作的意義在于表明,在頂層和底層之間的垂直間距僅為 30 納米的情況下,我們找到了一種獨(dú)立接觸頂層和底層設(shè)備的方法。它是在縮放維度上進(jìn)行高級(jí) CFET 集成的墊腳石。”

單片 CMOS CFET:具有挑戰(zhàn)性的工藝步驟和模塊

imec 科學(xué)總監(jiān) Steven Demuynck:“此外,我們繼續(xù)努力實(shí)現(xiàn)單片 CMOS CFET 器件演示,這是 imec 的一個(gè)戰(zhàn)略項(xiàng)目,通過與我們的合作伙伴的密切合作實(shí)現(xiàn)。與單極 CFET 器件不同,堆疊式 p 底部和 n 頂部器件現(xiàn)在將在同一晶圓上實(shí)現(xiàn)并獨(dú)立接觸。此外,集成流程應(yīng)允許區(qū)分共享公共柵極的兩個(gè)器件上的閾值電壓 (Vt) 設(shè)置——所有器件均采用行業(yè)相關(guān)的 50nm 柵極間距。這種垂直架構(gòu)具有重大意義。它不僅需要開發(fā)三個(gè)新的、特定于 CFET 的工藝模塊,還需要調(diào)整工藝流程中的其他模塊以適應(yīng)這些特定于 CFET 的模塊的存在。

第一個(gè)特定于 CFET 的工藝模塊,我們稱為中間電介質(zhì)隔離 (MDI:middle dielectric isolation),源于在頂部和底部柵極之間創(chuàng)建垂直電介質(zhì)隔離以區(qū)分頂部和底部器件之間的 Vt 設(shè)置的需要。為實(shí)現(xiàn)這一點(diǎn),我們的團(tuán)隊(duì)提出了一個(gè)從一開始就影響工藝流程的獨(dú)特解決方案:為創(chuàng)建 CFET 的有源部分而形成的 Si/SiGe 疊層轉(zhuǎn)變?yōu)楦叩?Si/SiGe1/SiGe2 多層疊層,具有更高的SiGe2 的 Ge% 高于 SiGe1。當(dāng)犧牲 SiGe1 層被設(shè)置 Vt 的功函數(shù)金屬取代時(shí),富含 Ge 的犧牲層被轉(zhuǎn)化為 MDI 電介質(zhì),在柵極內(nèi)形成 np WF 金屬分離。該堆棧允許在堆棧中的 Ge 缺陷層上形成內(nèi)部間隔物——這是一個(gè)關(guān)鍵的納米片特定特征,可將柵極與源極-漏極隔離。尋找最有效的方法來共同集成底部源漏、新的 MDI 模塊和內(nèi)部墊片,在這種緊密間距和高縱橫比幾何形狀下,是我們目前研發(fā)工作的重點(diǎn)。

頂部和底部器件的源極-漏極接觸金屬之間需要第二個(gè)垂直隔離。探索了各種選項(xiàng)來構(gòu)建和隔離底部和頂部觸點(diǎn)——在兩個(gè)高柵極之間的深處——并隨后路由底部和頂部晶體管。在 VLSI 2023 上共享了一個(gè)形態(tài)學(xué)概念驗(yàn)證流程,展示了制造堆疊式 MOL 的能力。

最后,在底部器件上生長源漏外延時(shí),我們需要封裝頂部通道。這將有效地在底部和頂部器件上實(shí)現(xiàn)不同摻雜的外延生長。”

從背面連接 CFET 器件

Anne Vandooren:“從長遠(yuǎn)來看,我們正在探索先進(jìn)的集成選項(xiàng),以從背面連接有源設(shè)備。這些發(fā)展是由進(jìn)一步降低標(biāo)準(zhǔn)單元高度和避免晶圓正面后端生產(chǎn)線中的布線擁塞的需求推動(dòng)的。

背面接觸引入了額外的工藝步驟,包括晶圓鍵合和從背面減薄基板。這些步驟挑戰(zhàn)了非常緊密的覆蓋層,以將背面層與正面已經(jīng)存在的小特征對(duì)齊。這更具挑戰(zhàn)性,因?yàn)樵阪I合過程中會(huì)發(fā)生晶圓變形,需要使用特定的光刻覆蓋校正方法。此外,還需要一個(gè)額外的工藝模塊來在背面金屬 1 和 CFET 器件的活性納米片部分之間提供適當(dāng)?shù)母綦x。”

CFET 支持:行業(yè)協(xié)作努力

Steven Demuynck:“自從我們開始 CFET 開發(fā)以來,我們發(fā)現(xiàn)與設(shè)備供應(yīng)商的合作強(qiáng)度有所增加。一方面,這些供應(yīng)商希望參與到開發(fā)的早期階段,以便能夠確定他們的工具、流程和材料在該路線圖中的位置。他們還想了解這些需要運(yùn)行的環(huán)境,以了解流程中上游和下游的交互。Imec 在為這些公司提供具有 CFET 相關(guān)拓?fù)浜蛶缀涡螤畹木A方面發(fā)揮著關(guān)鍵作用。在 IDM 開始開發(fā)之前,他們通常不容易獲得此類材料。另一方面,這些合作也為 imec 帶來了好處。與我們的工具供應(yīng)商的合作有助于我們利用合作伙伴的最先進(jìn)功能。

與此同時(shí),我們的邏輯核心合作伙伴有興趣通過評(píng)估各種流程風(fēng)格來確定我們遇到的關(guān)鍵挑戰(zhàn)和潛在障礙。在早期階段了解硬件和流程支持什么,可以讓他們?cè)陂_始自己的研發(fā)工作時(shí)搶先一步。”

編輯:黃飛

?

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論