作者:方志丹,于中堯,武曉萌,王啟東

單位:中國科學院微電子研究所

摘要:倒裝芯片球柵格陣列(FCBGA)基板作為人工智能、5G、大數據、高性能計算、智能汽車和數據中心等新興需求應用的CPU、圖形處理器(GPU)、FPGA等高端數字芯片的重要載體,業界對其的需求量快速增長。對FCBGA基板的關鍵技術進行了介紹,包括精細線路技術、翹曲控制技術和局部增強技術。同時,對FCBGA基板技術的發展趨勢及應用前景進行了展望。

01

引? 言

基板又稱集成芯片載板,為芯片提供電氣互連、保護、支撐、散熱、組裝等功效,作為連接裸芯片與PCB的橋梁,是集成電路產業中封裝產品的關鍵原材料之一。基板和芯片有多種封裝形式,其中倒裝芯片球柵格陣列(FCBGA)基板是針對AI、5G、大數據、高性能計算(HPC)、智能汽車和數據中心等新興需求應用的CPU、圖形處理器(GPU)、FPGA等高端數字芯片的重要載體,具有高算力、高速度、高帶寬、低延遲、低功耗、多功能和系統級集成等許多優點。

以柵格陣列形式倒裝的基板包含針腳柵格陣列(PGA)、平面柵格陣列(LGA)、球柵格陣列(BGA)3種類型。Prismark預測的2011—2026年封裝基板市場形勢如圖1所示,從2011年至2026年,FCPGA/LGA/BGA基板在封裝基板市場中的占比一直是最多的,均在45%以上,在2026年將達到57%;2026年基板市場規模將達到214億美元,2021至2026年這5年的預計年均復合增長率達到8.3%,其中FCBGA市場規模達到121億美元,占比在一半以上,年復合增長率在基板市場中最高,達到11.5%。可見,未來封裝基板市場中最為活躍的就是FCBGA基板市場。目前我國大陸基板廠已經具備引線鍵合球柵格陣列(WBBGA)、倒裝芯片級封裝(FCCSP)等中低端基板制造能力,但高端的FCBGA基板量產市場仍被日韓及中國臺灣地區企業所壟斷。

近些年,我國相關行業也在該領域進行大量投入,其中深南電路、興森快捷、安捷利美維等基板廠已在存儲、射頻等FCBGA基板方向進行大額資金投入和先進技術研發,中國科學院微電子研究所建立了國內唯一的先進基板研發線,在FCBGA基板方面已實現精細線路與埋入式功能基板成套技術,形成支撐AI、HPC系統封裝集成應用的大尺寸基板(70 mm×70 mm以上)、大尺寸芯片(25 mm×25 mm以上)、大功率(1000 W以上)以及大功率密度(1.5 W/mm2)的樣品。

02

FCBGA 基板關鍵技術

FCBGA基板技術不同于普通基板。首先,隨著數據處理芯片的尺寸增加到70 mm×70 mm,配套的FCBGA基板從80 mm×80 mm向110 mm×110 mm的更大尺寸過渡。其次,面向高密度互連的需求,基板增層[指在芯板(Core)兩側的增層布線層,不包含芯板上的兩層線路]的數量將從10層增加到18層甚至更多。同時,為實現高密度布線,線寬/線間距將減小到5 μm/5 μm以下。綜上,FCBGA基板具有超大尺寸、高疊層和精細線路3個方面的特點。超大尺寸和高疊層在基板工藝上的突出表現為翹曲增加,同時線路節距減少,需要新的基板材料、新工藝和新結構形式的引入,所以FCBGA基板關鍵技術的研究主要包括精細線路技術、翹曲控制技術和局部增強技術3個方面。

2.1 精細線路技術

精細線路的主要載體為具有低粗糙度表面的絕緣介質,常規選用工藝為半加成工藝(SAP),該工藝主要考察介質材料與金屬種子層間結合力的控制問題,結合力的強弱對精細線路的附著起到決定性作用。因此,針對上述關鍵因素進行重點介紹,包括增層介質材料、工藝方法和結合力控制技術3個方面。

2.1.1 增層介質材料

基板的增層介質材料有多種,包括雙馬來酰亞胺三嗪(BT)樹脂、半固化片(PP)、涂樹脂銅箔(RCC)、光敏絕緣材料和味之素增層膜(ABF)等。PP由玻纖布和樹脂構成,其表面的粗糙度來自壓合時的銅箔毛牙,超低粗糙度的銅箔表面平均粗糙度在0.5 μm以上,通常在改良半加成工藝(MSAP)中用于制作15 μm以上的線路。受到玻纖束經緯交織的影響,盲孔的成孔直徑在65 μm以上。RCC是在銅箔表面涂覆樹脂,其粗糙度同樣來源于銅箔,因其不含玻纖或填料,受溫濕度影響的漲縮比較大,不適合用于大尺寸、高疊層基板的制作;光敏絕緣材料由樹脂、填料和感光溶劑等組成,通過光刻工藝可實現小于25 μm的超小盲孔,但在使用中其表面的種子層通常需要通過半導體工藝沉積,工藝兼容性相對較差。ABF是一種由高分子樹脂、硅微粉和溶劑等物質混合形成的復合薄膜材料,通過除膠工藝控制其表面粗糙度(通常小于0.4 μm),采用常規基板工藝即可以直接鍍銅,形成線寬/線間距不大于15 μm/15μm的精細線路。因為填料采用均勻分布的平均直徑不大于0.5 μm的硅微粉,可以實現孔徑為25~30 μm的高密度盲孔。總的來說,相比于其他增層介質,ABF具有易于加工和較高的工藝兼容性等特點,因此被廣泛用作FCBGA基板的增層介質材料。

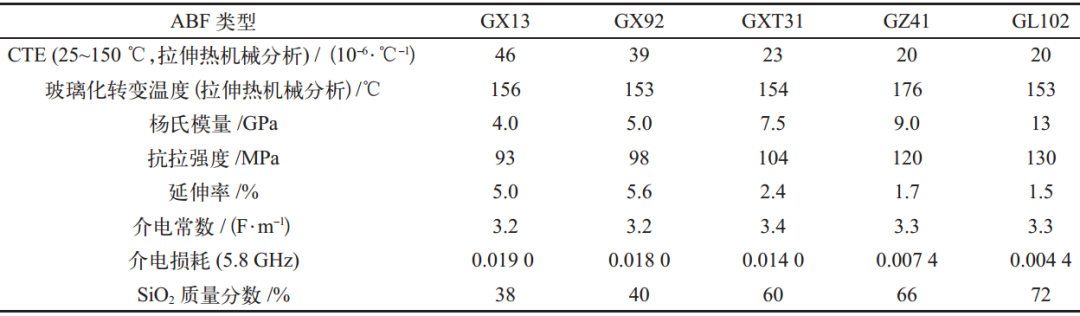

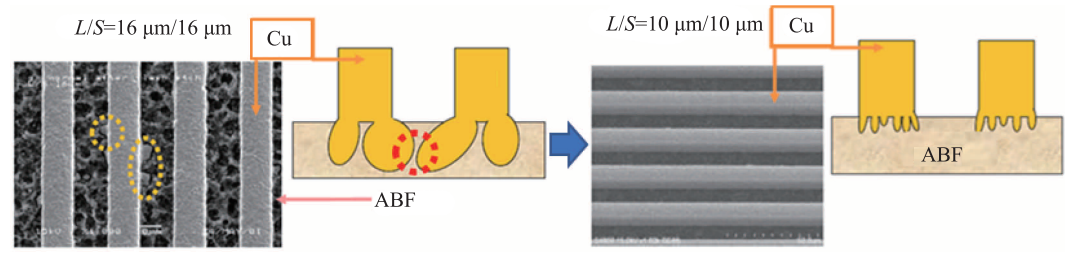

為了滿足高密度布線、高速傳輸和高疊層基板低翹曲的需求,ABF的物性不斷提升,從GX系列到GL系列,隨著硅粉填料的質量分數從38%增加到72%,熱膨脹系數(CTE)從46×10-6·℃-1降低到20×10-6·℃-1,減小一半以上;楊氏模量從4 GPa提高到13 GPa,介電損耗降低4倍。ABF基本物性參數對比如表1所示。表面粗糙度與精細線路如圖1所示,可以看出介質表面的粗糙度對線寬/線間距的影響。當介質表面的粗糙度較大時,圖形電鍍中有滲鍍風險,在細線路的底部易形成微短或短路,不利于細線路的線形控制。隨著線路節距的縮小,介質表面的粗糙度也相應減小,因此,ABF中硅微粉的平均直徑從0.5 μm下降到0.1 μm時,相應的表面粗糙度從400 nm下降到100 nm及以下。

表1? ABF基本物性參數對比

圖1??表面粗糙度與精細線路

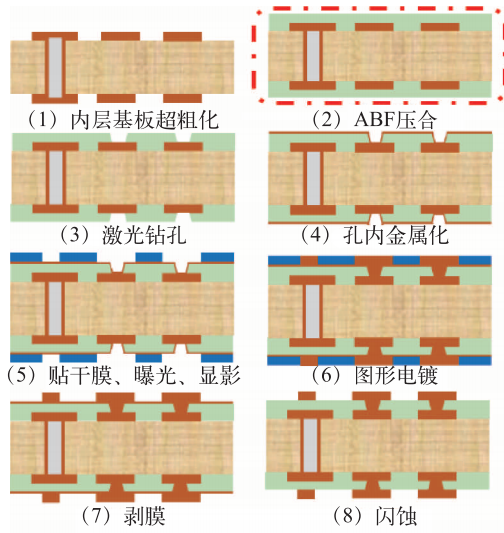

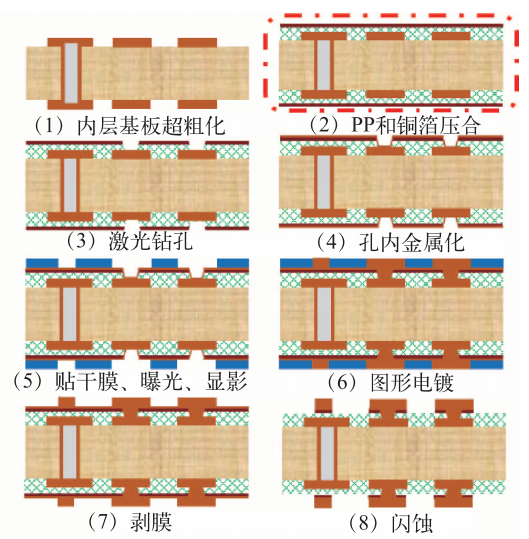

2.1.2 SAP工藝

精細線路通常選用SAP工藝實現,SAP與MSAP工藝流程如圖2所示,SAP工藝是將內層基板做超粗化處理以增強介質和下層金屬線路間的結合力,在基板兩面貼增層介質,通過真空壓膜和鏡面鋼板整平獲得均勻覆蓋在基板表面的介質層,激光鉆孔后對介質表面做除膠工藝處理,清除鉆孔產生的殘渣并形成均勻的、納米尺度的粗糙表面,在孔內及介質表面沉積疏松的化銅層,再經過圖形發生(包括貼膜、曝光、顯影工藝)和圖形轉移(包括圖形電鍍、剝膜和閃蝕)等一系列工藝形成增層線路。

SAP和MSAP的最大區別在于絕緣介質上的種子層。SAP中絕緣介質表面的種子層是通過化銅工藝沉積厚度約為1 μm、比電解銅疏松的化學銅,而MSAP中絕緣介質表面的種子層是和介質一起壓合的電解銅箔(厚度為2~3 μm)。由于閃蝕藥水的蝕刻選擇性,超薄又疏松的化銅層比電解銅更易去除,更利于實現高密度線路。但如果種子層與介質間的結合力弱,細線路在剝膜、閃蝕及超粗化處理等工藝中經過多次有壓力的藥液沖擊,會出現飛線、掉線等不良現象,尤其對于大尺寸基板上長度為幾十毫米的長距精細線路來說,其掉線現象會非常嚴重。所以SAP工藝的核心技術,也是通過使用無銅箔增層介質材料實現精細線路的前提條件,即控制化銅層與介質材料間的結合力。

(a)SAP工藝流程

(b)MSAP工藝流程

圖2? SAP與MSAP工藝流程

2.1.3 結合力控制技術

增層介質材料作為隔離上下兩層金屬線路的絕緣層,若其與下層線路的結合力弱,多層基板易在制備過程或可靠性測試中,因溫度、濕度等環境條件的變化出現爆板、分層等不良情況。若其與上層金屬的結合力弱,則在圖形發生和轉移工藝中就會出現線路倒伏、剝落,無法完成多層基板的制作。

通過對線路做超粗化處理來實現介質材料與下層線路的良好結合,采用粗化藥水對銅晶界進行有選擇性的刻蝕,在銅晶粒表面形成獨特的凹凸形狀,超粗化的電鍍銅表面如圖3所示,可以在控制對精細線路的蝕刻量的同時,提高線路銅和樹脂間的物理結合力。然后在超粗化的銅表面增加有機膜,利用有機膜、銅及樹脂間的共價鍵可以提高線路銅和樹脂間的化學結合力。

圖3 超粗化的電鍍銅表面

介質材料與上層線路結合力的控制涉及一系列工藝,包括材料的回溫取用時間、壓合參數、固化條件、除膠工藝,需根據材料的物化性質和固化機理的不同,優化介質材料使用時的全套工藝參數。其中除膠工藝決定了介質表面的最終處理狀態,包含3個步驟:1)蓬松,打散高分子樹脂中的C—C鍵,降低鍵能,形成蜂窩狀結構,使樹脂易受高錳酸鹽蝕刻液咬蝕;2)除膠,利用堿性高錳酸鹽蝕刻溶液除去內層鉆污,清潔孔壁并且粗化樹脂,形成幾百納米不等的粗糙表面;3)中和,除去除膠段反應的殘留物并清洗殘留的松散硅微粉。

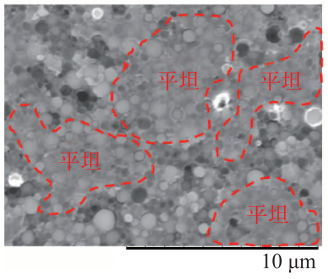

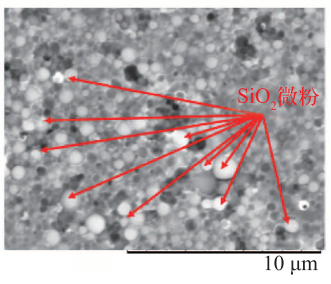

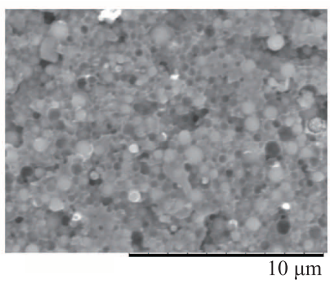

因為設備及藥水差異,同種材料的除膠工藝參數差別較大,但最終獲得的介質表面狀態是一致的。具體表現為樹脂和硅微粉均勻分布、納米級粗糙度的表面形貌,測量結合力的辦法參照IPC650相關標準。以GZ系列為例,其中樹脂為環氧樹脂和氰酸酯樹脂,相較于GX系列的環氧和苯酚硬化劑更難刻蝕,并且介質中的硅微粉填料質量占比達到66%。不同除膠工藝銅剝離后的介質表面如圖4所示,中科院微電子所研究結果表明,當除膠不足時,介質表面有多處樹脂平坦區域,部分較大尺寸的硅微粉剝落,這種形貌時對應的結合力僅為0.15 N/mm,如圖4(a)所示;當除膠過量時,表面硅粉剝落的同時有大量硅粉半露在表面,雖然表面的粗糙度增加,但因表面硅粉面積占比較大,這時的結合力仍偏低,只達到0.23 N/mm,若采用玻璃蝕刻劑對硅粉做微蝕處理,在硅粉和樹脂間制造空隙即形成“錨定效應”,也可以提高結合力;當除膠適量時,介質表面有樹脂和松散硅粉剝落形成的粗糙度,同時表面剩余的硅粉被樹脂包裹,或硅粉的大部分體積埋入樹脂中,化銅工藝中的催化劑離子鈀與樹脂的吸附性優于玻璃,利用其優異的吸附性,可以獲得化銅層和介質材料的較高結合力(0.4 N/mm以上),滿足精細線路工藝對無銅箔增層介質結合力的需求(通常為0.4~0.6 N/mm)。

(a)剝離力為0.15 N/mm

(b)剝離力為0.23 N/mm

(c)剝離力為0.40 N/mm

圖4? 中科院微電子所研究的不同除膠工藝銅剝離后的介質表面

2.2 翹曲控制技術

翹曲是由于片狀結構中不同組成部分間的CTE差異,在制造過程中,各個部分隨溫度變化漲縮不同,產生的機械應力不同,造成片狀結構表面起伏。嚴重的基板翹曲會導致2個重要的問題:一是嚴重的翹曲導致無法封裝或封裝失效,最直接的結果是倒裝焊的焊球局部無法與PCB連接,或相鄰焊球間發生橋接;二是過大的基板翹曲導致封裝后的基板與芯片間存在較大應力,過大的應力導致焊球開裂、芯片開裂等可靠性問題。因材料特性不同,基板翹曲有一定的不確定性,但通過材料及結構的設計也可以實現對翹曲的控制。

2.2.1 翹曲的不確定性

FCBGA封裝基板翹曲是因為銅線路、絕緣樹脂以及芯板間CTE失配產生的應力不平衡造成基板形狀改變。大部分相關文獻都是關于封裝后基板的翹曲檢測和討論,對封裝前的FCBGA基板翹曲的討論非常少。由于基板材料中含有大量的高分子材料,而這些材料的物理性質隨加工工藝和熱處理(比如回流、固化等條件)的差異,參數變化較大,很難得到如同金屬一樣的一致性。

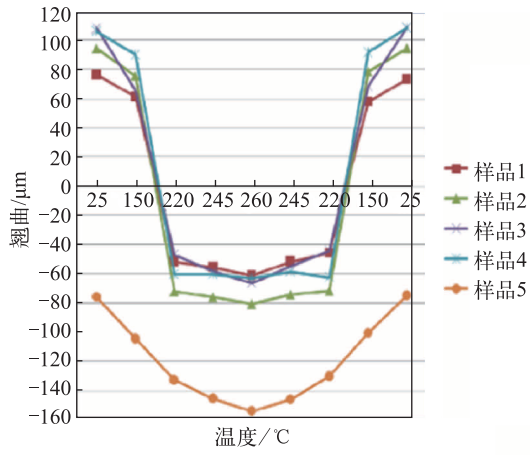

LIN等人對于多家供應商提供的用于疊層封裝(POP)的具有相同結構設計的基板(共5種基板),進行了封裝前和回流后的翹曲測量數據對比。選用一個12 mm的方形POP封裝用基板做設計,其中Core厚度為0.15 mm,采用低CTE材料,通過兩層板制作后的基板厚度為0.23 mm。翹曲模式包括內凹、外凸和組合模式3種,如圖5所示,通常把內凹稱為“笑臉”,外凸稱為“哭臉”,對應的翹曲測量數據通常正值為“哭臉”,負值為“笑臉”。5種基板的翹曲測試結果如圖6所示。

(a)笑臉

(b)哭臉

(c)組合

圖5 翹曲模式

圖6 5種基板的翹曲測試結果

從圖6可以看出:(1)不同供應商提供的基板翹曲差異超過20 μm;(2)采用低 CTE Core的所有供應商提供的基板在室溫下的翹曲均表現為“哭臉”;(3)同一供應商采用不同工藝制造的基板,其翹曲存在明顯差異;(4)采用超低CTE的Core的基板與所有供應商提供的樣品具有完全不同的翹曲特性,在室溫下的翹曲表現為笑臉。不同廠商提供的具有同樣的基板結構的產品,其翹曲參數不同,這是翹曲的一種不確定性。

基板翹曲的不確定性有以下幾個方面的原因。

(1)Core和絕緣層的主要成分是有機樹脂。有機樹脂在加工過程中,從半固化狀態轉變成固化狀態,分子間并不是完全徹底的結合。在一定的溫度下,固化會進一步發生,對基板的物性和翹曲存在影響。不同廠家的基板工藝條件有差異,所以固化后的物性差異導致翹曲不同,物性測試結果表明,經過不同的溫度處理,基板材料的物性存在差異。

(2)基板吸濕對于基板翹曲有一定的影響。有機樹脂均有一定的吸水率,加工完全的基板在空氣中吸收了水汽,水分子在基板中擴散是一個逐漸發生的過程,所以吸收水汽對于基板的翹曲也有影響。基板在封裝前需要在一定的溫度下烘烤一段時間,就是為了通過烘烤將基板吸收的水汽去除,增加尺寸的穩定性。不同廠家基板的存放時間和存放條件的差異,導致其吸濕程度不同,也會存在翹曲差異。

(3)Core本身具有一定的翹曲。Core本身是由多層玻纖布疊壓制成的,玻纖布的經線和緯線的張力不同,疊壓時多層玻纖布的經線和經線對齊,緯線和緯線對齊,才可以盡可能地減小Core的翹曲,但在實際加工中是無法實現每層玻璃纖維的經線和緯線完全精準對齊的。

2.2.2 基板翹曲的控制技術

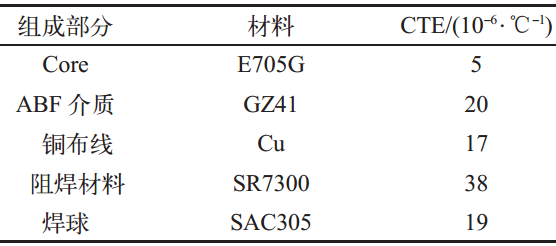

基板翹曲具有一定程度的不確定性,但翹曲控制仍有一定的規律可循。FCBGA基板的典型材料及其CTE如表2所示,Core、ABF介質材料、銅布線、阻焊材料和圖形均是影響翹曲的因素,完整基板的CTE與層數厚度以及銅線路的布線設計等諸多因素有關。

表2?FCBGA基板的典型材料和CTE

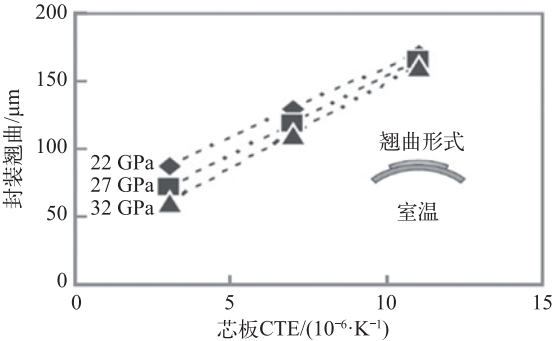

第一,基板CTE與彈性模量。NAKAMURA等人描述了基板材料的物性對基板翹曲的影響:(1)Core的CTE越小,封裝翹曲越小;(2)Core的彈性模量越高,封裝翹曲越小;(3)CTE的影響超過彈性模量的影響。Core CTE和彈性模量對封裝翹曲的影響如圖7所示。

圖7 Core CTE和彈性模量對封裝翹曲的影響

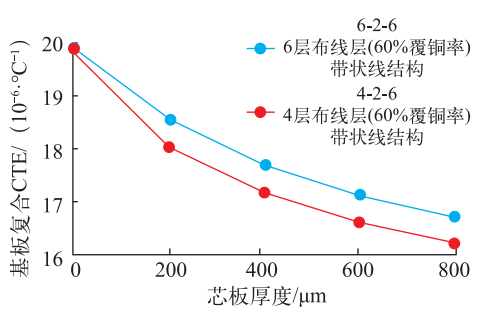

第二,Core的厚度。KOICHI描述了完整基板的CTE和Core厚度的關系,如圖8所示。隨著Core厚度的增加,多層基板的CTE從20×10-6·℃-1下降到接近16×10-6·℃-1。為降低基板的整體翹曲,采用低CTE材料作為Core,Core采用玻璃纖維增強的樹脂結構,其CTE是所有基板材料中最低的。同樣的疊層結構,Core厚度增加,Core在整個基板中的厚度占比增大,基板整體的CTE也隨之下降。通過增加Core的厚度(如從0.8 mm增加至1.4 mm)來降低翹曲,這一方法在實際的大尺寸FCBGA基板制造中被廣泛使用。

圖8 基板CTE與厚度的關系

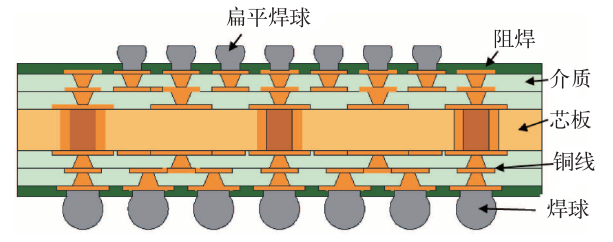

第三,結構設計與工藝。FCBGA基板結構如圖9所示,由于FCBGA基板都是對稱加工的,兩側絕緣層介質均采用同種材料。在保證信號完整性的前提下,設計相對于Core對稱的布線層,并且上下布線層的覆銅率保持一致,銅線路分布應盡可能均勻,保證絕緣層樹脂厚度一致,形成相對于Core對稱分布的線路和絕緣層結構。在此前提下,基板制造工藝的一致性尤為重要,如圖形掩模工藝中的曝光和顯影對干膜線寬/線間距的控制,圖形電鍍工藝中銅線路的高度,壓合工藝中的介質壓合厚度及閃蝕工藝中銅線路圖形閃蝕的均勻性等,并且在多層板的制造過程中保持一致的工藝控制和最短時間的工藝銜接。對稱的兩層是同時加工完成的,對稱兩層的布線和絕緣層具有相同的CTE,與Core間形成的熱失配、產生的機械應力互相平衡,可以最大幅度地降低翹曲。

圖9 FCBGA基板結構

總之,材料選擇的匹配和結構設計的對稱,對稱結構制造的一致性,增層與內層結構間達到應力平衡,是減小FCBGA基板翹曲的關鍵。

2.3 局部增強技術

隨著器件工作頻率、互連密度的增高,電互連延遲以及損耗已經成為越來越突出的問題。同時,在集成數量增大、密度增高的應用需求下,面對芯片高密度互連接口和板級工藝的尺寸差距及性能提升要求,業界的解決方法主要分為3個方向:(1)將芯片引腳進行扇出以適應更大尺度的連接,如晶圓級扇出再分配;(2)尋求中間轉接結構,如含硅通孔的轉接板;(3)開發更細線寬/線間距、更小互連直徑與截距的工藝路線,研發更高性能、更高工藝適應性的材料,如日本Shinko開發的頂層細線路基板(i-THOP)。上述3種方案在研發方面均有優勢較為突出的樣品及可靠性驗證報道,但在市場需求與成本管控的沖突下,硅轉接板與板級細線路開發在多種產品應用中遇到瓶頸,因此需要開辟一條可實現低成本、高密度集成的新路徑。

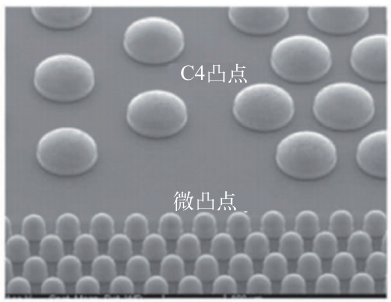

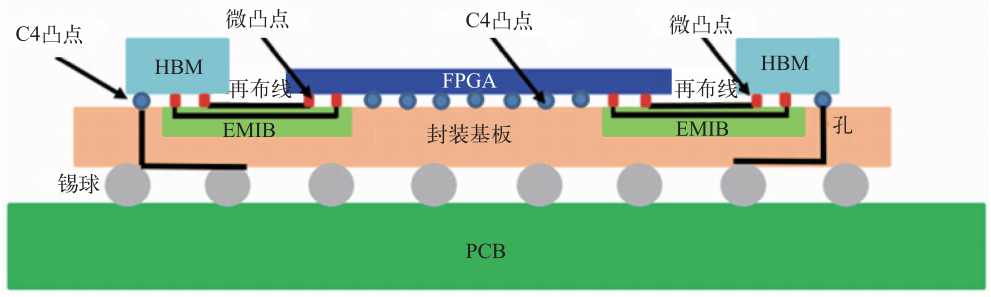

英特爾的嵌入式多芯片互連橋(EMIB)技術將后兩個方向進行了優勢互補,舍棄了難度大、成本高的硅通孔技術,保留硅轉接板中的細線路,使之成為硅橋結構,并通過增層技術將其埋置于基板中,將硅橋上引出的窄節距焊盤和2顆倒裝芯片上的微凸點鍵合互連,基板上的寬節距焊盤和倒裝芯片上的可控塌陷芯片連接(C4)凸點鍵合互連。硅橋分擔了芯片間的通信,信號與地則可排布在基板布線層中,一方面在硅橋上實現了低損耗、高密度的高速互連,另一方面分擔了增層布線壓力,降低基板細線路、疊孔等的加工難度,減少多層板加工的翹曲問題。如此巨大的優勢使得這一技術迅速被業內認可,業界圍繞硅橋與基板開展了一系列研究。2015年,英特爾的EMIB技術被應用于Stratix 10產品中,其取代硅轉接板實現了基板與多個高帶寬存儲器(HBM)的集成,實現焊盤節距為55μm,互連密度達256~625/mm,英特爾EMIB產品如圖10所示。自此,硅橋逐漸成為各大研究機構及公司探索高密度互連、系統化異質集成的主要路徑之一。

倒裝芯片上的C4凸點與微凸點

(c)EMIB結構示意圖

圖10 英特爾EMIB產品

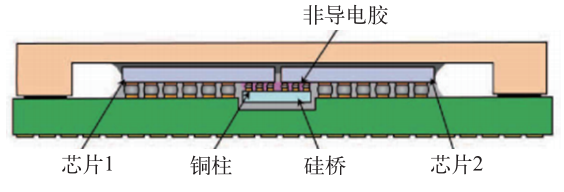

IBM提出一種直接鍵合異質集成(DBHi)的方法,將硅橋和2顆芯片分別通過小直徑銅柱鍵合,在完成布線后的基板特定區域的表面挖槽,再將鍵合好的硅橋和芯片整體表貼到基板的槽體內,基板上的焊盤和倒裝芯片通過大直徑可控塌陷焊球分別進行鍵合,實現了硅橋與基板通過異質異構接口同步與應用芯片的集成,IBM的DBHi結構如圖11所示。單層I/O密度最高達到400個,在5 GHz頻率下,其損耗低于1.5 dB。

圖11 IBM的DBHi結構

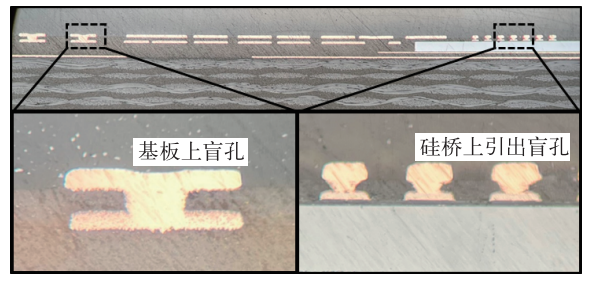

最近,中國科學院微電子所設計研發的硅橋可實現單邊互連帶寬為2.7 Tbit·s-1·mm-1,并成功將其集成于基板中。圖12為IME甚高密度互連埋入(UHDIE)基板樣品剖面圖,該基板在40 GHz頻率下的插入損耗測試中,插入損耗降低至2.0 dB,串擾為21dB,其單通道傳輸速率達40 Gbit/s。嵌入式硅橋技術需要硅橋和基板2種技術的密切聯合互動。通過開腔和層壓技術將硅橋埋置于板內的技術挑戰主要來自精準貼片、大小孔同步填實與小節距引出結構加工等工藝。微電子所實現了50 μm的硅橋焊盤全引出的8層板加工,其中同步鍍孔的直徑差達90 μm。

圖12 IME UHDIE基板樣品剖面

嵌入式硅橋技術仍然存在著一些挑戰。在性能指標上,國際上嵌入式硅橋技術的單邊互連吞吐帶寬在AIB接口的標準下發展,然而目前AIB接口的單通道速率僅為?2 Gbit/s,單邊吞吐量為504 Gbit·s-1·mm-1。新推出的UCle2.0接口,希望通過當今45 μm凸點間距的先進封裝技術將芯片的單邊吞吐帶寬提升到1.3 Tbit·s-1·mm-1。芯片間的帶寬吞吐量的發展是不間斷、無上限的,因此如何盡可能地提高芯片的帶寬是目前嵌入式硅橋技術面臨的一大指標挑戰。在結構上,以EMIB為代表的嵌入式硅橋技術在國際上已經得到了應用,但是目前的EMIB技術還主要局限在2個芯粒(Chiplet)為一組的邊到邊的互連。隨著芯粒個數的增加,芯粒間互連需求的增加,硅橋的個數會成倍地增長,這種增長帶來的大數量硅橋埋入又增加了工藝難度。

03

FCBGA基板技術展望

在材料方面,對于大尺寸系統級芯片(SoC)封裝來說,FCBGA基板的CTE需要更低,才能保證大尺寸芯片封裝的可靠性。ABF材料進一步降低CTE的難度很大,BT材料的半固化片的CTE可以達到1×10-6·℃-1~3×10-6·℃-1,作為堆積的絕緣材料在降低FCBGA基板整體CTE方面會做出重要貢獻。未來更大尺寸的SoC封裝中,采用PP半固化作為介質絕緣層,替代ABF或和ABF同時使用以降低CTE及基板翹曲、提高封裝的可靠性,是可選的技術路徑之一。未來的FCBGA基板在高密度布線方面,線寬/線間距在7μm/7μm水平上將持續相當長的一段時間,除非ABF作為增層核心材料這一狀況發生改變。如果液態絕緣樹脂在FCBGA基板上能夠大規模應用,最小線寬/線間距會進一步降低到5μm/5μm,甚至有可能達到2μm/2μm。液態樹脂絕緣材料與現有的基板制造技術相距甚遠,因其環保及材料利用率等問題,被基板制造商接受還有一定的距離。光敏絕緣材料可實現小盲孔,對于提高布線密度有幫助。但是,如果光敏樹脂不能擺脫樹脂+顆粒填充物的體系,提高布線密度,其達到高良率也是非常困難的。

在結構方面,EMIB基板大量用于芯粒封裝。相比硅轉接板,其具有低成本的技術優勢,而且可降低FCBGA基板層數,未來在三維異質集成封裝中會有大量的應用。由于硅橋的設計和制造并非現有基板廠的工作內容,必須有強有力的封裝設計和基板設計能力,同時還要有代工廠的支持才能實現。目前,基板廠需要和終端用戶緊密配合,才能完成芯片+硅橋+EMIB基板的整體設計;長遠來看,基板廠需要建立自己完善的封裝設計團隊,否則,制造EMIB的基板廠只能服務于那些頭部設計公司。目前已經有多種利用硅橋進行局部增強布線的封裝方式,未來在FCBGA基板中嵌入全新的硅橋封裝也是值得期待的。

在市場方面,近幾年隨著全球數據需求的迅速增加,網絡和數據中心得到迅速發展。數據處理、數據傳輸和數據存儲都對芯片的要求越來越高,SoC芯片的功能越來越復雜,尺寸越來越大。盡管如此,SoC的技術進步仍然滿足不了數據處理芯片的性能要求,人們開始采用Chiplet技術,通過三維異質集成來提高系統級封裝的性能,滿足數據處理快速增長的需求。FCBGA基板的尺寸越來越大,在一個基板上放置的芯片數量越來越多,基板的層數也越來越多,大尺寸、高疊層的FCBGA基板已經成為目前基板市場中增長最快的產品。2019—2022年,FCBGA基板市場的年平均增長率超過27%,呈現出爆發式增長態勢。FCBGA基板已經成為目前封裝市場上最為搶手的高端產品。全球的FCBGA基板市場出現一板難求的現象,基本的交貨期通常超過一年。需求小的客戶無法得到基板廠的支持,而頭部企業動輒包下整個基板廠的產能。FCBGA基板的制造商主要集中在日本、韓國和中國臺灣地區,三地的高端基板制造商近年來紛紛擴產,預計2025年前后FCBGA基板市場的缺貨情況會有所緩解。

總之,FCBGA基板作為高端芯片封裝的載體,因其良好的可加工性能,無論現在還是未來,在高端芯片封裝領域都起到非常重要的作用。隨著材料科學的進步,未來FCBGA基板技術會有進一步的發展。

參考文獻:(略)

中文引用格式:方志丹,于中堯,武曉萌,等. FCBGA基板關鍵技術綜述及展望[J].?電子與封裝,2023,23(3):030103.

英文引用格式:FANG Zhidan, YU Zhongyao, WU Xiaomeng, et al. Overview and prospect of key technologies of FCBGA substrate[J]. Electronics & Packaging, 2023, 23(3):030103.

作者簡介:方志丹(1977—),女,黑龍江五常人,博士,正高級工程師,主要研究方向為先進封裝領域高密度基板及功能基板的集成技術。

編輯:黃飛

電子發燒友App

電子發燒友App

評論