一、半導體封裝技術簡介

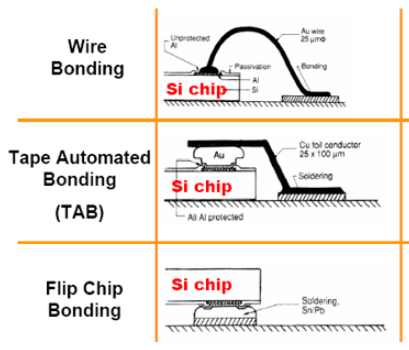

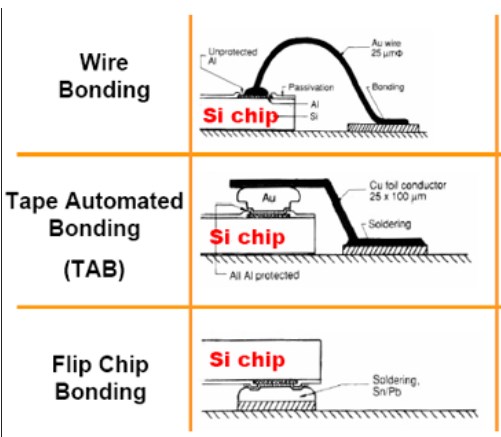

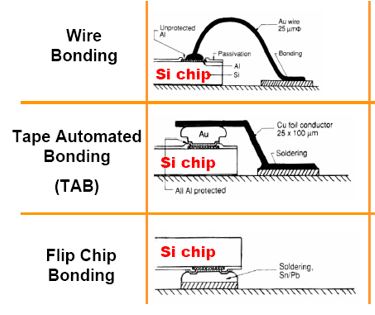

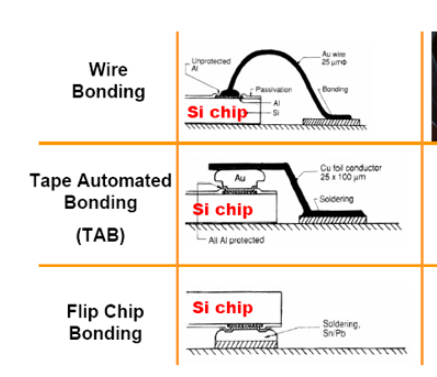

從事半導體行業,尤其是半導體封裝行業的人,總繞不開幾種封裝工藝,那就是芯片粘接、引線鍵合、倒裝連接技術。

尤其以引線鍵合(Wire Bonding)及倒裝連接(Flip Chip Bonding)最為常見,因為載帶連接技術(TAB)有一定的局限性,封裝上逐漸淘汰了這種技術。

倒裝芯片技術是通過芯片上的凸點直接將元器件朝下互連到基板、載體或者電路板上。引線鍵合的連接方式是將芯片的正面朝上,通過引線(通常是金線)將芯片與線路板連接。

引線鍵合、載帶連接、倒裝連接各有特點。其中倒裝連接以結構緊湊,可靠性高在封裝行業應用越來越廣泛。

二、什么是倒裝芯片技術?

倒裝芯片技術起源于IBM,IBM公司在1960年研制開發出在芯片上制作凸點的倒裝芯片焊接工藝。以95Pb5Sn凸點包圍著電鍍NiAu的凸球。后來制作PbSn凸點,使用可控塌焊連接(Controlled collapse Component Connection, 簡稱C4技術),該技術最初為自己的大型計算機主機所開發的一種高可靠的封裝技術。C4芯片具有優良的電學、熱學性能,封裝疲勞壽命至少提高10倍以上。

自從IBM研制并成功應用C4技術后,隨后的技術發展中,一些半導體公司又對C4技術進行了優化升級,其中包括Fairchild公司研制了Al凸點,Amelco公司研制了Au凸點技術。

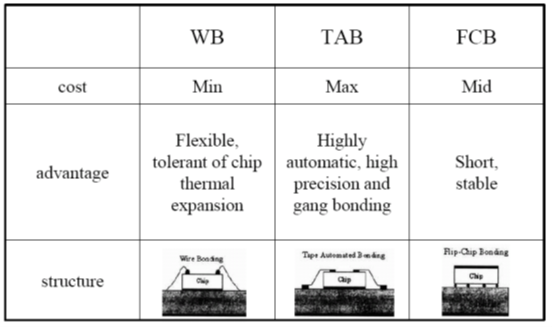

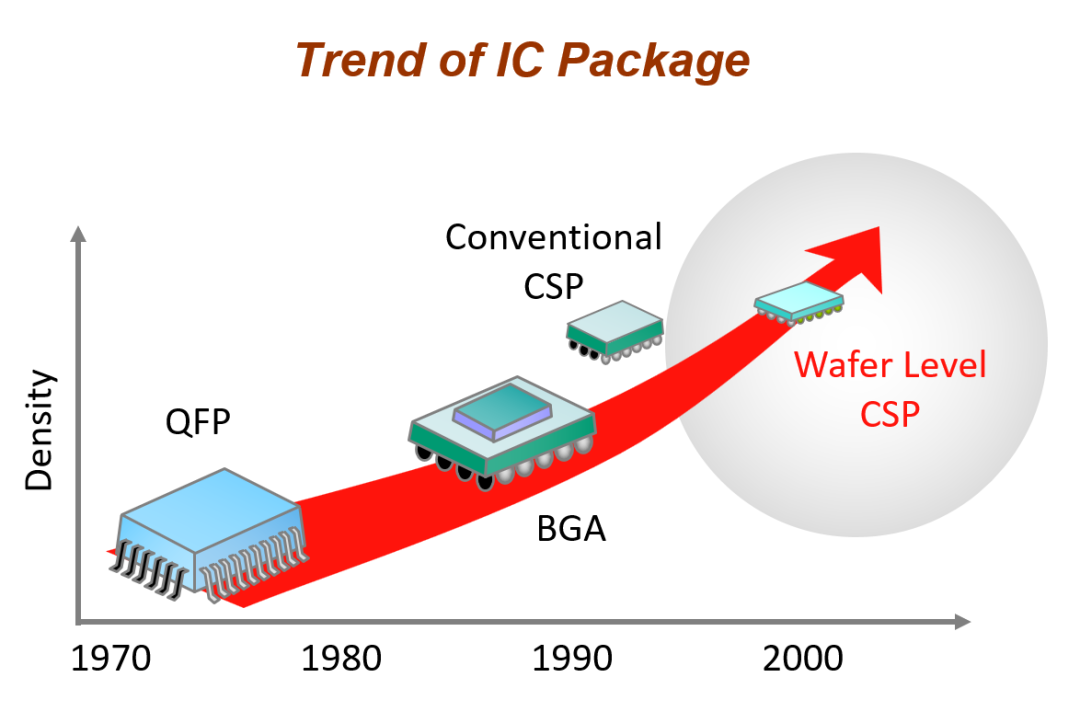

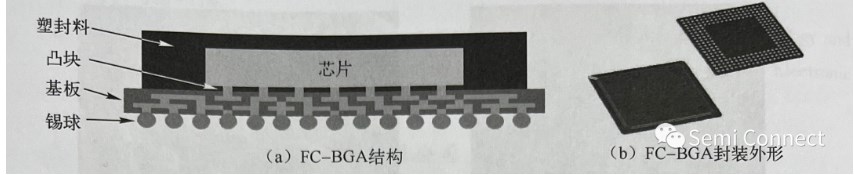

半導體封裝技術也從QFP(Quad Flat Package方形扁平式)封裝工藝發展到BGA(Ball Grid Array球狀引腳柵格陣列)封裝,到最新的CSP(Chip Scale Package晶圓級)封裝。

下圖是傳統的QFP、BGA等工藝封裝后的器件。

伴隨半導體芯片體積的逐漸減小,對芯片封裝技術要求越來越高,封裝技術向著晶圓及封裝發展。

在對傳統芯片進行封裝時,通常是將晶圓進行切割成Die,再對每一個Die進行封裝,伴隨封裝技術的成熟,在最新的半導體封裝中,將封裝工藝與半導體工藝進行融合,在晶圓上對芯片進行統一封裝,再切割形成可靠性更高的獨立芯片。

隨著倒裝技術的成熟應用,目前全世界的倒裝芯片消耗量超過年60萬片,且以約50%的速度增長,3%的晶圓封裝用于倒裝芯片凸點技術,幾年后可望超過20%。

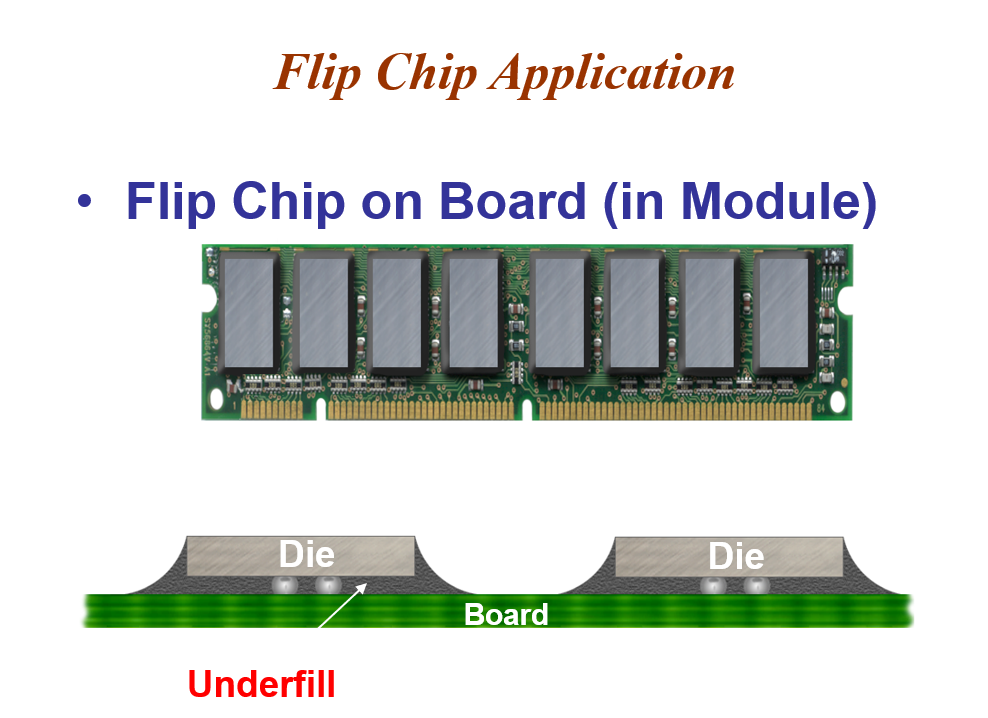

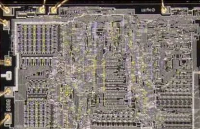

倒裝芯片元件主要用于半導體設備,有些元件,如無源濾波器,探測天線,存儲器裝備也開始使用倒裝芯片技術,由于芯片直接通過凸點直接連接基板和載體上。因此,更確切的說,倒裝芯片也叫DCA(Direct Chip Attach),下圖中CPU及內存條等電子產品是最常見的應用倒裝芯片技術的器件。

下圖是內存條中存儲芯片通過倒裝技術與線路板連接,芯片與電路板中間通過填充膠固定。

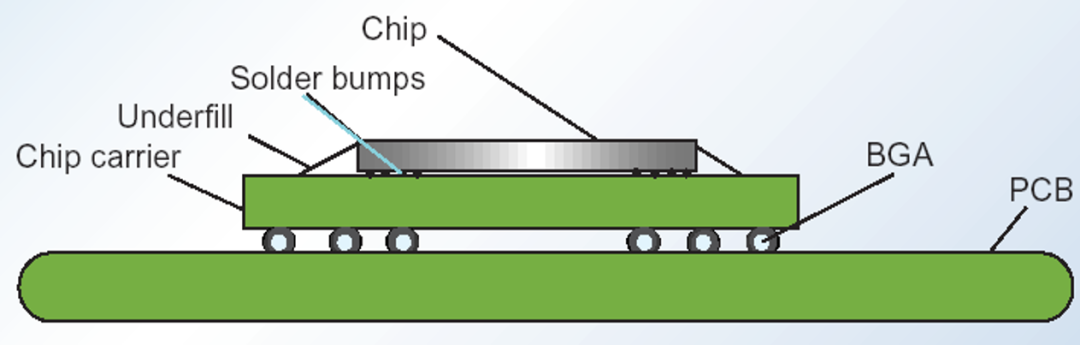

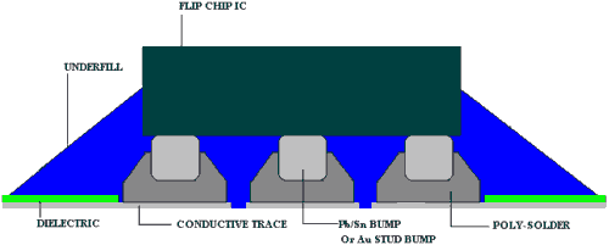

在典型的倒裝芯片封裝中, 芯片通過3到5個密耳(1mil=25um)厚的焊料凸點連接到芯片載體上,底部填充材料用來保護焊料凸點。

下圖是一張典型的倒裝連接圖,芯片與下方的基板采用倒裝方式連接:

三、倒裝技術技術細節

在半導體芯片倒裝連接的過程中,有許多前后處理的工序,以下詳細介紹倒裝工藝的相關細節:

第一步:凸點下金屬化(UBM,under bump metallization)

倒裝連接第一步需在芯片表面制作凸點技術,倒裝連接的本質是芯片上的凸點與基板上的凸點(凹槽)連接,半導體表面的金屬化有以下幾種方式:

(a)濺射:用濺射的方法一層一層地在硅片上沉積薄膜,然后通過照相平版技術形成UBM圖樣,然后刻蝕掉不是圖樣的部分。

(b)蒸鍍:?利用掩模,通過蒸鍍的方法在硅片上一層一層地沉積。這種選擇性的沉積用的掩模可用于對應的凸點的形成之中。

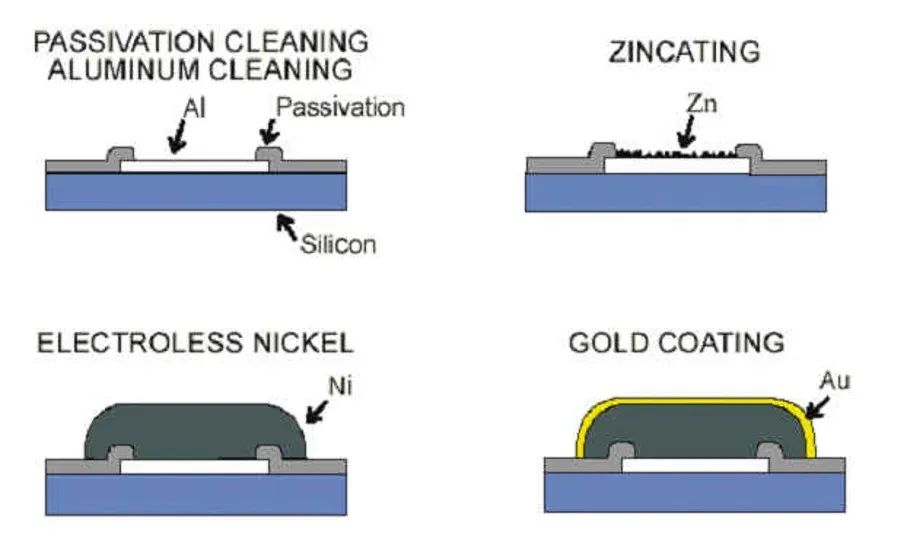

(c)化學鍍:采用化學鍍的方法在Al焊盤上選擇性地鍍Ni。常常用鋅酸鹽工藝對Al表面進行處理。無需真空及圖樣刻蝕設備,低成本。

下圖是半導體芯片進行凸點金屬化(UBM)的流程:

由于鋁焊盤表面有一層氧化物,鍍層金屬無法粘附在氧化的表面上,因此要對鋁表面進行適當的處理以清除氧化物層。

一般的方法是在鋁焊盤上采用鋅酸鹽處理(zincation),該技術是在鋁的表面沉積一層鋅,防止鋁發生氧化,鍍鋅工藝的一個缺點是鋁也會被鍍液腐蝕掉,因此需要采用二次鍍鋅工藝,在進行鍍鋅工藝中,有0.3-0.4mm厚的鋁將被腐蝕掉。在鍍鋅過程中,鋅沉積在鋁表面,而同時鋁及氧化鋁層則被腐蝕掉。鋅保護鋁不再發生氧化,鋅層的厚度很薄。

在進行鍍鋅工藝后,進一步采用化學鍍鎳用作UBM的沉積,金屬鎳起到連接/擴散阻擋的作用。鎳的擴散率非常小,與焊料也幾乎不發生反應,它僅與錫有緩慢的反應,因此非常適合作為共晶焊料的UBM金屬。化學鍍鎳既可以用于UBM金屬的沉積,也可以用來形成凸點。在部分倒裝凸點的表面會進一步鍍金,由于金導電性能好,且不易氧化,可增加倒裝連接的可靠性。

第二步: 回流形成凸點

焊料凸點方法有蒸鍍焊料凸點、電鍍焊料凸點、印刷焊料凸點、釘頭焊料凸點、放球凸點、焊料轉移凸點等不同工藝,其中電鍍焊料及印刷焊料工藝使用較廣泛。

在半導體表面凸點金屬化后,通過回流爐將金屬化部分形成倒裝球。

回流形成凸點的大致過程如下圖所示:

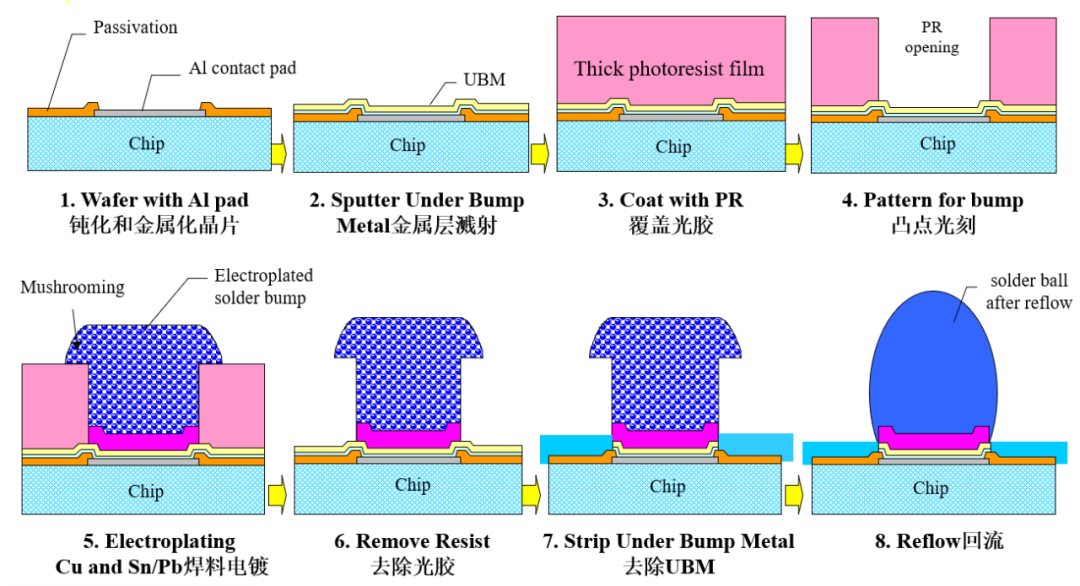

其中電鍍焊料凸點的具體形成過程如下圖:

凸點常用的材料是Pb/Sn合金,因為其回流焊特性好,適合工業化生產。

除了常見的Pb/Sn合金,凸點也有Au/Ni合金等凸點材料,為了保證可靠的互連,UBM必須與用于凸點的焊料合金相容。適合高鉛的UBM不一定適合高錫焊料。例如Cu潤濕層合適于含錫3-5%的高鉛焊料,但是不適合于高錫焊料,因為Cu與Sn反應迅速而生成Sn-Cu金屬間化合物。如果Cu被消耗完畢,焊料將與焊區不潤濕。

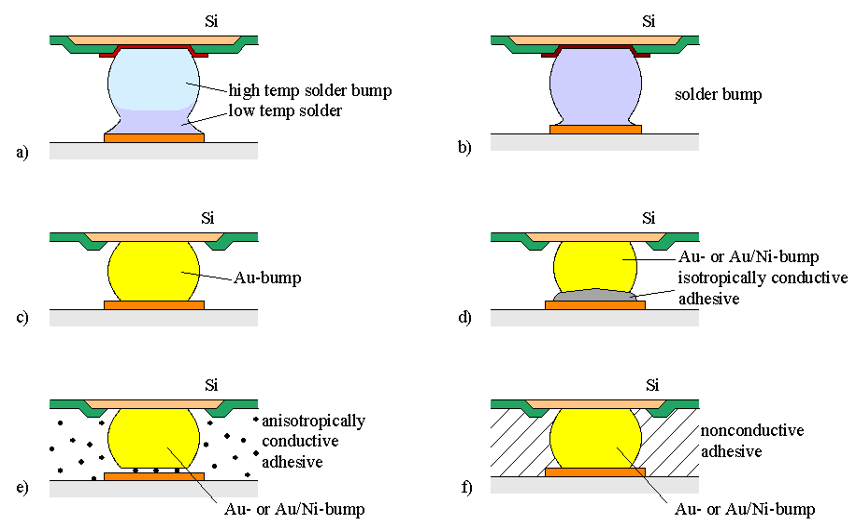

下圖是不同的凸點材質件的倒裝連接:

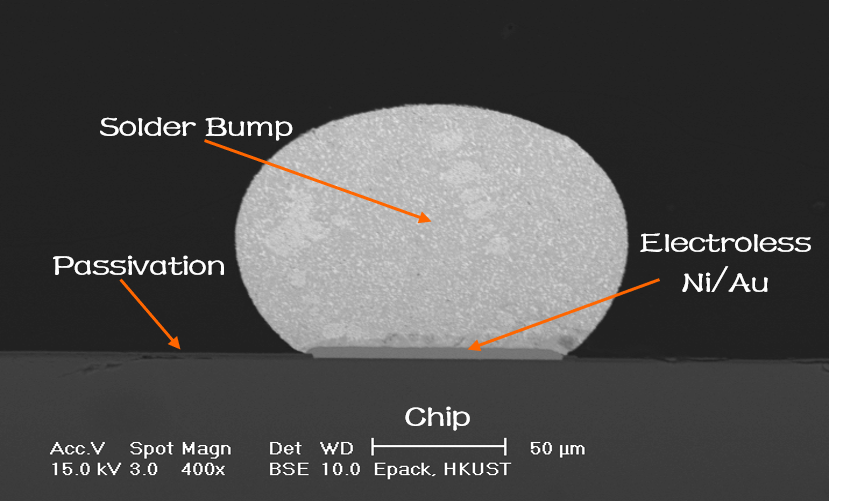

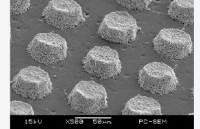

芯片表面形成的凸點在掃描電鏡下觀察到的外觀如下圖所示:

下圖中的左圖是回流(高溫)前的凸點狀態,右圖是經高溫后的凸點狀態,經高溫后凸點融化成球形。

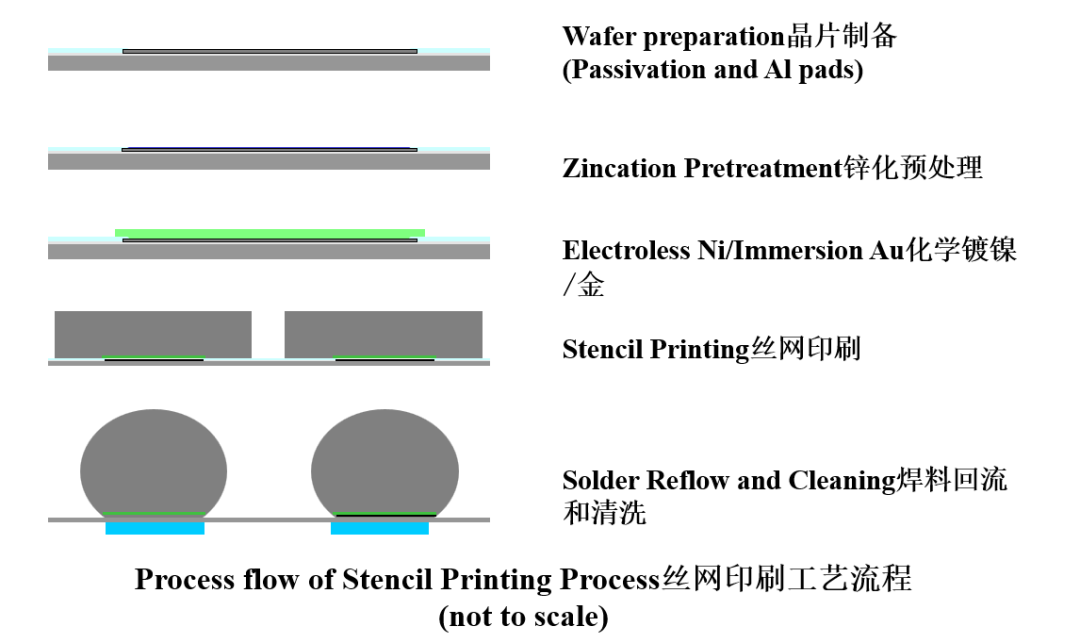

化學鍍UBM和絲網印刷工藝(Electroless UBM and Stencil Printing)是工業應用中低成本倒裝焊凸點制備方法。

以下是絲網印刷凸點制作流程(Stencil Printing Process Flow)及完成后的凸點形貌:

第三步:倒裝芯片組裝

此工序是將完成凸點制作的芯片與載板進行倒裝互聯。

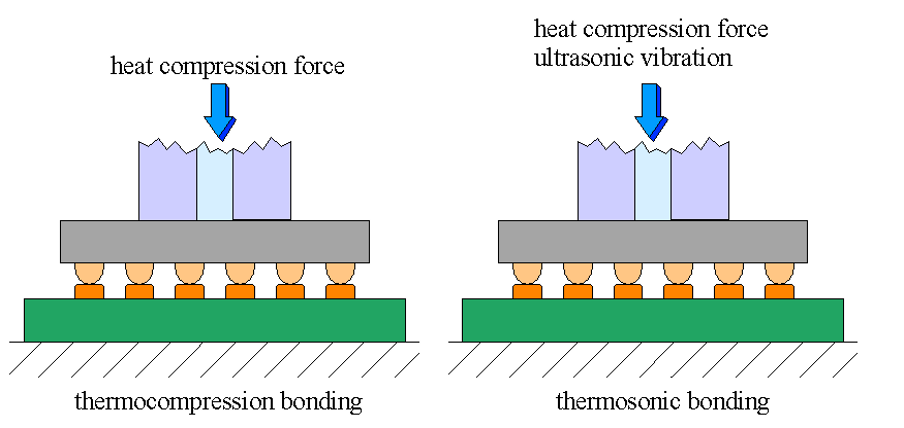

熱壓倒裝技術是芯片與載板連接的常用方法,最合適的凸點材料是金,凸點可以通過傳統的電解鍍金方法生成,或者采用釘頭凸點方法,后者就是引線鍵合技術中常用的凸點形成工藝。

對于熱壓倒裝技術,由于壓力較大,溫度也較高,這種工藝僅適用于剛性基底,如氧化鋁或硅。另外,基板必須保證較高的平整度,熱壓頭也要有較高的平行對準精度。為了避免半導體材料受到不必要的損害,施加壓力時應該有一定的梯度。

第四步:底部填充與固化

倒裝連接后已完成了芯片與基板的連接,為了提高倒裝穩定性,會在倒裝后的芯片與基板之間采用填充膠加固,填膠工藝如下圖所示:

芯片與基底之間的底部填充材料使連接抵抗熱疲勞的性能顯著提高,如果沒有底部填充,則熱疲勞將是倒裝芯片主要的可靠性問題。

(a)底部填充材料將集中的應力分散到芯片的塑封材料中去。

(b)可阻止焊料蠕變,并增加倒裝芯片連接的強度與剛度。

(c)保護芯片免受環境的影響(濕氣、離子污染等)。

(d)使得芯片耐受機械振動與沖擊。

四、倒裝芯片技術總結

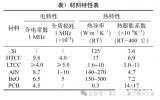

與一般的焊點連接一樣,倒裝芯片連接的可靠性也要受到基板與芯片的熱膨脹系數(CTE)失配的影響,此外焊點的高度、焊點之間的最大間距亦會對可靠性造成影響。連接區的裂紋多是在從連接溫度冷卻下來的過程中產生的。

由于金的熔點溫度高,因此它對疲勞損傷的敏感程度遠小于焊料。因此,如果在熱循環中應力沒有超過凸點與焊盤之間的連接強度,那么可靠性不會存在太大問題。

芯片與基底之間的底部填充材料使連接抵抗熱疲勞的性能顯著提高,如果沒有底部填充,則熱疲勞將是倒裝芯片主要的可靠性問題。

倒裝芯片組裝非常適用于高頻應用領域,因為在這種組裝結構中,芯片與基底之間的連接通路非常短。倒裝焊點的串連阻抗為1mW左右,串連電感為0.025nH,遠小于引線鍵合中的5-10nH。

正是由于倒裝芯片組裝的這種優點,信號的傳輸時延可以顯著降低。

五、倒裝芯片技術的優點與缺點

(1)倒裝連接技術優點:

(a)小尺寸: 小的IC引腳圖形 (只有扁平封裝的5%)減小了高度和重量。

(b)功能增強: 使用倒裝芯片能增加I/O的數量。I/O不像導線鍵合處于芯片四周而受到數量的限制。面陣列可以在更小的空間里進行更多信號、功率以及電源等互連。一般的倒裝芯片焊盤可達400個。

(c)性能增加: 短的互連距離減小了電感、電阻以及電容,保證了信號延遲減少、較好的高頻率、以及從晶片背面較好的熱通道。

(d)提高了可靠性:大芯片的環氧填充確保了高可靠性。倒裝芯片可減少三分之二的互連引腳數。

(e)提高了散熱能力:倒裝芯片沒有塑封,芯片背面可進行有效的冷卻。

(f)低成本:批量的凸點降低了成本。

(2)倒裝連接技術的缺點:

(a)裸芯片很難測試;

(b)凸點芯片適應性有限

(c)隨著間距地減小和引腳數的增多導致PCB技術面臨挑戰;

(d)必須使用X射線檢測設備檢測不可見的焊點;

(e)和SMT工藝相容性較差;

(f)操作夾持裸晶片比較困難;

(g)要求很高的組裝精度;

(h)目前使用底部填充要求一定的固化時間;

(i)有些基板可靠性較低;

(j)維修很困難或者不可能。

審核編輯:湯梓紅

電子發燒友App

電子發燒友App

評論