據(jù)傳,業(yè)界公認(rèn)的臺積電獨(dú)吞蘋果訂單的關(guān)鍵利器就是CoWoS封裝技術(shù)。這幾年,先進(jìn)封裝技術(shù)不斷涌現(xiàn),目前可以列出的估計有幾十種,讓人眼花繚亂。主流的封裝技術(shù)都有哪些?如何區(qū)分呢?下面就給大家盤點(diǎn)一下。

為了便于區(qū)分,將先進(jìn)封裝分為兩大類:① 基于XY平面延伸的先進(jìn)封裝技術(shù),主要通過RDL進(jìn)行信號的延伸和互連;② 基于Z軸延伸的先進(jìn)封裝技術(shù),主要是通過TSV進(jìn)行信號延伸和互連。

基于XY平面延伸的 先進(jìn)封裝技術(shù)

這里的XY平面指的是Wafer或者芯片的XY平面,這類封裝的鮮明特點(diǎn)就是沒有TSV硅通孔,其信號延伸的手段或技術(shù)主要通過RDL層來實(shí)現(xiàn),通常沒有基板,其RDL布線時是依附在芯片的硅體上,或者在附加的Molding上。因?yàn)樽罱K的封裝產(chǎn)品沒有基板,所以此類封裝都比較薄,目前在智能手機(jī)中得到廣泛的應(yīng)用。

1.FOWLP

FOWLP (Fan-out Wafer Level Package)是WLP(Wafer Level Package)的一種,因此我們需要先了解WLP晶圓級封裝。

在WLP技術(shù)出現(xiàn)之前,傳統(tǒng)封裝工藝步驟主要在裸片切割分片后進(jìn)行,先對晶圓(Wafer)進(jìn)行切割分片(Dicing),然后再封裝(Packaging)成各種形式。

WLP于2000年左右問世,有兩種類型:Fan-in(扇入式)和Fan-Out(扇出式)WLP晶圓級封裝和傳統(tǒng)封裝不同,在封裝過程中大部分工藝過程都是對晶圓進(jìn)行操作,即在晶圓上進(jìn)行整體封裝(Packaging),封裝完成后再進(jìn)行切割分片。

因?yàn)榉庋b完成后再進(jìn)行切割分片,因此,封裝后的芯片尺寸和裸芯片幾乎一致,因此也被稱為CSP(Chip Scale Package)或者WLCSP(Wafer Level Chip Scale Packaging),此類封裝符合消費(fèi)類電子產(chǎn)品輕、小、短、薄化的市場趨勢,寄生電容、電感都比較小,并具有低成本、散熱佳等優(yōu)點(diǎn)。

開始WLP多采用Fan-in型態(tài),可稱之為Fan-in WLP 或者FIWLP,主要應(yīng)用于面積較小、引腳數(shù)量少的芯片。

隨著IC工藝的提升,芯片面積縮小,芯片面積內(nèi)無法容納足夠的引腳數(shù)量,因此衍生出Fan-Out WLP 封裝形態(tài),也稱為FOWLP,實(shí)現(xiàn)在芯片面積范圍外充分利用RDL做連接,以獲取更多的引腳數(shù)。

FOWLP,由于要將RDL和Bump引出到裸芯片的外圍,因此需要先進(jìn)行裸芯片晶圓的劃片分割,然后將獨(dú)立的裸芯片重新配置到晶圓工藝中,并以此為基礎(chǔ),通過批量處理、金屬化布線互連,形成最終封裝。FOWLP封裝流程如下圖所示。

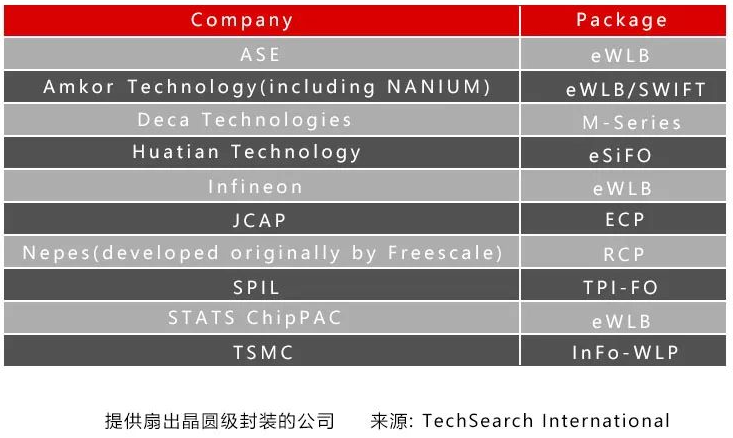

FOWLP受到很多公司的支持,不同的公司也有不同的命名方法,下圖所示為各大公司的提供的FOWLP。

無論是采用Fan-in還是Fan-out,WLP晶圓級封裝和PCB的連接都是采用倒裝芯片形式,芯片有源面朝下對著印刷電路板,可以實(shí)現(xiàn)最短的電路徑,這也保證了更高的速度和更少的寄生效應(yīng)。另一方面,由于采用批量封裝,整個晶圓能夠?qū)崿F(xiàn)一次全部封裝,成本的降低也是晶圓級封裝的另一個推動力量。

2.INFO

InFO技術(shù)起源于FOWLP封裝。FOWLP封裝最早在2009~2010年由Intel提出,僅用于手機(jī)基帶芯片封裝。FOWLP的英文全稱為Fan-Out Wafer Level Packaging,簡稱FOWLP,中文全稱為扇出型晶圓級封裝,其采取拉線出來的方式,成本相對便宜。FOWLP可以讓多種不同裸晶,做成像WLP制程一般埋進(jìn)去,等于減一層封裝,假設(shè)放置多顆裸晶,等于省了多層封裝,有助于降低客戶成本。此時唯一會影響IC成本的因素則為裸晶大小。

相較系統(tǒng)級封裝(SiP),扇出型晶圓級封裝不僅設(shè)計難度低于矽穿孔(Through Silicon Via;TSV)3D IC,且接近2.5D IC概念與相對有助降低成本。2013年起,全球各主要封測廠積極擴(kuò)充FOWLP產(chǎn)能,主要是為了滿足中低價智慧型手機(jī)市場,對于成本的嚴(yán)苛要求。FOWLP由于不須使用載板材料,因此可節(jié)省近30%封裝成本,且封裝厚度也更加輕薄,有助于提升晶片商產(chǎn)品競爭力。臺積電(TSMC)在扇出型晶圓級封裝領(lǐng)域投入并開發(fā)了集成扇出型(Integrated Fan-Out, InFO)封裝技術(shù),改變了晶圓級封裝的市場格局。隨著InFO技術(shù)的大規(guī)模應(yīng)用,以及嵌入式晶圓級球柵陣列(eWLB)技術(shù)的進(jìn)一步發(fā)展,一批新廠商和扇出型晶圓級封裝技術(shù)可能將進(jìn)入市場。臺積電的扇出型晶圓級封裝解決方案被稱為InFO,已用于蘋果iPhone 7系列手機(jī)的A10應(yīng)用處理器封裝,其量產(chǎn)始于2016年。

臺積電在2014年宣傳InFO技術(shù)進(jìn)入量產(chǎn)準(zhǔn)備時,稱重布線層(RDL)間距(pitch)更小(如10微米),且封裝體厚度更薄。

InFO給予了多個芯片集成封裝的空間,比如8mm x 8mm平臺可用于射頻和無線芯片的封裝,15mm x 15mm可用于應(yīng)用處理器和基帶芯片封裝,而更大尺寸如25mm x 25mm用于圖形處理器和網(wǎng)絡(luò)等應(yīng)用的芯片封裝。

2016年說是扇出型封裝市場的轉(zhuǎn)折點(diǎn),蘋果和臺積電的加入改變了該技術(shù)的應(yīng)用狀況,可能將使市場開始逐漸接受扇出型封裝技術(shù)。扇出型封裝市場將分化發(fā)展成兩種類型:

(1)扇出型封裝“核心”市場,包括基帶、電源管理及射頻收發(fā)器等單芯片應(yīng)用。該市場是扇出型晶圓級封裝解決方案的主要應(yīng)用領(lǐng)域,并將保持穩(wěn)定的增長趨勢。

(2)扇出型封裝“高密度”市場,始于蘋果公司APE,包括處理器、存儲器等輸入輸出數(shù)據(jù)量更大的應(yīng)用。該市場具有較大的不確定性,需要新的集成解決方案和高性能扇出型封裝解決方案。但是,該市場具有很大的市場潛力。

FOWLP可滿足更多I/O數(shù)量需求,如果要大量應(yīng)用FOWLP技術(shù),首先必須克服以下之各種挑戰(zhàn)問題:

(1)焊接點(diǎn)的熱機(jī)械行為:因FOWLP的結(jié)構(gòu)與BGA構(gòu)裝相似,所以FOWLP焊接點(diǎn)的熱機(jī)械行為與BGA構(gòu)裝相同,F(xiàn)OWLP中焊球的關(guān)鍵位置在硅晶片面積的下方,其最大熱膨脹系數(shù)不匹配點(diǎn)會發(fā)生在硅晶片與PCB之間。

(2)晶片位置之精確度:在重新建構(gòu)晶圓時,必須要維持晶片從持取及放置(Pick and Place)于載具上的位置不發(fā)生偏移,甚至在鑄模作業(yè)時,也不可發(fā)生偏移。因?yàn)榻殡妼娱_口,導(dǎo)線重新分布層(Redistribution Layer; RDL)與焊錫開口(Solder Opening)制作,皆使用黃光微影技術(shù),光罩對準(zhǔn)晶圓及曝光都是一次性,所以對于晶片位置之精確度要求非常高。

(3)晶圓的翹曲行為:人工重新建構(gòu)晶圓的翹曲(Warpage)行為,也是一項(xiàng)重大挑戰(zhàn),因?yàn)橹匦陆?gòu)晶圓含有塑膠、硅及金屬材料,其硅與膠體之比例在X、Y、Z三方向不同,鑄模在加熱及冷卻時之熱漲冷縮會影響晶圓的翹曲行為。

(4)膠體的剝落現(xiàn)象:在常壓時被膠體及其他聚合物所吸收的水份,在經(jīng)過220~260℃回焊(Reflow)時,水份會瞬間氣化,進(jìn)而產(chǎn)生高的內(nèi)部蒸氣壓,如果膠體組成不良,則易有膠體剝落之現(xiàn)象產(chǎn)生。

3.FOPLP

FOPLP(Fan-out Panel Level Package)面板級封裝,借鑒了FOWLP的思路和技術(shù),但采用了更大的面板,因此可以量產(chǎn)出數(shù)倍于 300 毫米硅晶圓芯片的封裝產(chǎn)品。

FOPLP技術(shù)是FOWLP 技術(shù)的延伸,在更大面積的方形載板上進(jìn)行Fan-Out制程,因此被稱為 FOPLP 封裝技術(shù),其Panel載板可以采用PCB載板,或者液晶面板用的玻璃載板。

目前而言,F(xiàn)OPLP采用了如 24×18英寸(610×457mm)的PCB載板,其面積大約是 300 mm硅晶圓的4 倍,因而可以簡單的視為在一次的制程下,就可以量產(chǎn)出 4 倍于300 mm硅晶圓的先進(jìn)封裝產(chǎn)品。

和FOWLP工藝相同,F(xiàn)OPLP 技術(shù)可以將封裝前后段制程整合進(jìn)行,可以將其視為一次的封裝制程,因此可大幅降低生產(chǎn)與材料等各項(xiàng)成本。下圖為FOWLP和FOPLP比較。

FOPLP采用了PCB上的生產(chǎn)技術(shù)進(jìn)行RDL的生產(chǎn),其線寬、線間距目前均大于10um,采用SMT設(shè)備進(jìn)行芯片和無源器件的貼裝,由于其面板面積遠(yuǎn)大于晶圓面積,因而可以一次封裝更多的產(chǎn)品。相對FOWLP,F(xiàn)OPLP具有更大的成本優(yōu)勢。目前,全球各大封裝業(yè)者包括三星電子、日月光均積極投入到FOPLP 制程技術(shù)中。

4.EMIB

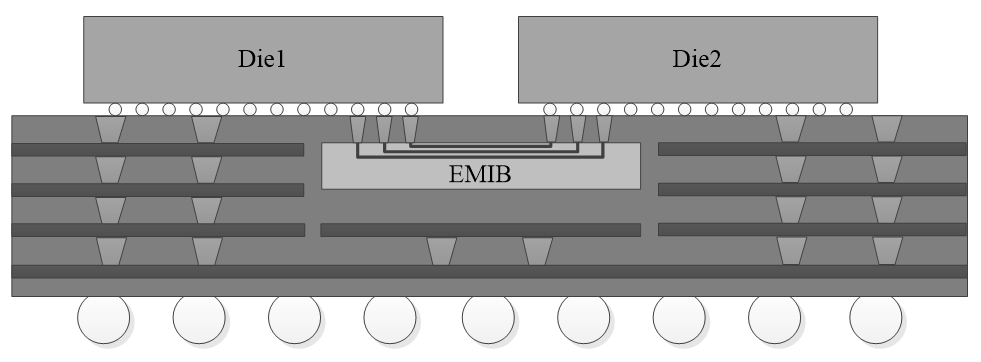

EMIB(Embedded Multi-Die Interconnect Bridge)嵌入式多芯片互連橋先進(jìn)封裝技術(shù)是由英特爾提出并積極應(yīng)用的,和前面描述的3種先進(jìn)封裝不同,EMIB是屬于有基板類封裝,因?yàn)镋MIB也沒有TSV,因此也被劃分到基于XY平面延伸的先進(jìn)封裝技術(shù)。

EMIB理念跟基于硅中介層的2.5D封裝類似,是通過硅片進(jìn)行局部高密度互連。與傳統(tǒng)2.5封裝的相比,因?yàn)闆]有TSV,因此EMIB技術(shù)具有正常的封裝良率、無需額外工藝和設(shè)計簡單等優(yōu)點(diǎn)。

傳統(tǒng)的SoC芯片,CPU、GPU、內(nèi)存控制器及IO控制器都只能使用一種工藝制造。采用EMIB技術(shù),CPU、GPU對工藝要求高,可以使用10nm工藝, IO單元、通訊單元可以使用14nm工藝,內(nèi)存部分則可以使用22nm工藝,采用EMIB先進(jìn)封裝技術(shù)可以把三種不同工藝整合到一起成為一個處理器。下圖是EMIB示意圖。

和硅中介層(interposer)相比,EMIB硅片面積更微小、更靈活、更經(jīng)濟(jì)。EMIB封裝技術(shù)可以根據(jù)需要將CPU、IO、GPU甚至FPGA、AI等芯片封裝到一起,能夠把10nm、14nm、22nm等多種不同工藝的芯片封裝在一起做成單一芯片,適應(yīng)靈活的業(yè)務(wù)的需求。

通過EMIB方式,KBL-G平臺將英特爾酷睿處理器與AMD Radeon RX Vega M GPU整合在一起,同時具備了英特爾處理器強(qiáng)大的計算能力與AMD GPU出色的圖形能力,并且還有著極佳的散熱體驗(yàn)。這顆芯片創(chuàng)造了歷史,也讓產(chǎn)品體驗(yàn)達(dá)到了一個新的層次。

基于Z軸延伸的 先進(jìn)封裝技術(shù)

基于Z軸延伸的先進(jìn)封裝技術(shù)主要是通過TSV進(jìn)行信號延伸和互連,TSV可分為2.5D TSV和3D TSV,通過TSV技術(shù),可以將多個芯片進(jìn)行垂直堆疊并互連。

在3D TSV技術(shù)中,芯片相互靠得很近,所以延遲會更少,此外互連長度的縮短,能減少相關(guān)寄生效應(yīng),使器件以更高的頻率運(yùn)行,從而轉(zhuǎn)化為性能改進(jìn),并更大程度的降低成本。

TSV技術(shù)是三維封裝的關(guān)鍵技術(shù),包括半導(dǎo)體集成制造商、集成電路制造代工廠、封裝代工廠、新興技術(shù)開發(fā)商、大學(xué)與研究所以及技術(shù)聯(lián)盟等研究機(jī)構(gòu)都對 TSV 的工藝進(jìn)行了多方面的研發(fā)。

此外,需要讀者注意,雖然基于Z軸延伸的先進(jìn)封裝技術(shù)主要是通過TSV進(jìn)行信號延伸和互連,但RDL同樣是不可或缺的,例如,如果上下層芯片的TSV無法對齊時,就需要通過RDL進(jìn)行局部互連。

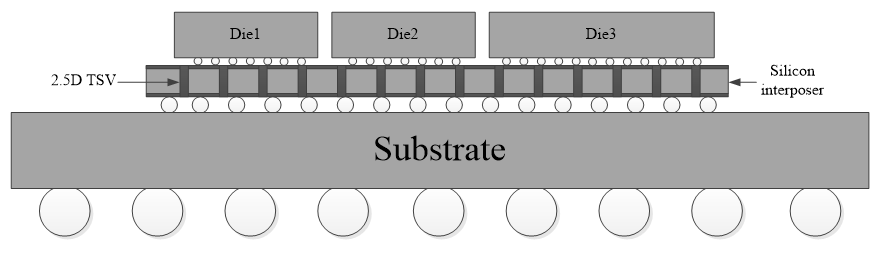

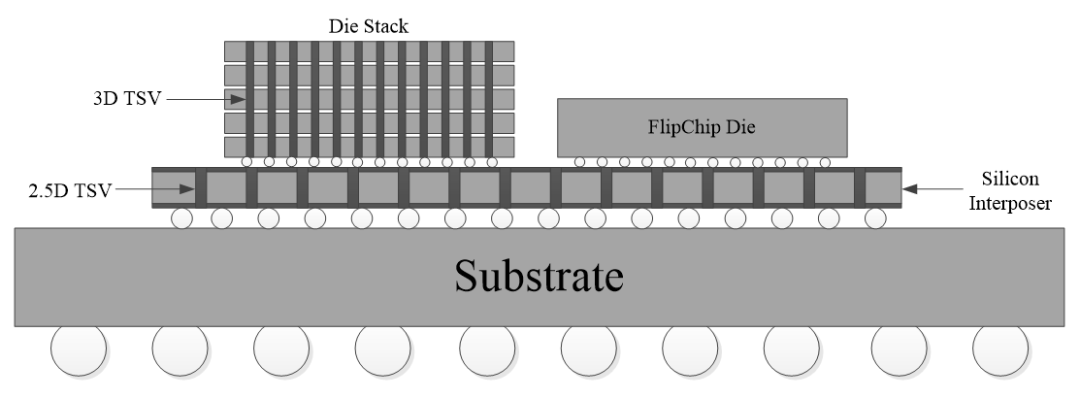

5.CoWoS

CoWoS(Chip-on-Wafer-on-Substrate)是臺積電推出的 2.5D封裝技術(shù),CoWoS是把芯片封裝到硅轉(zhuǎn)接板(中介層)上,并使用硅轉(zhuǎn)接板上的高密度布線進(jìn)行互連,然后再安裝在封裝基板上,如下圖所示。

CoWoS和前面講到的InFO都來自臺積電,CoWoS有硅轉(zhuǎn)接板Silicon Interposer,InFO則沒有。CoWoS針對高端市場,連線數(shù)量和封裝尺寸都比較大。InFO針對性價比市場,封裝尺寸較小,連線數(shù)量也比較少。

臺積電2012年就開始量產(chǎn)CoWoS,通過該技術(shù)把多顆芯片封裝到一起,通過Silicon Interposer高密度互連,達(dá)到了封裝體積小,性能高、功耗低,引腳少的效果。

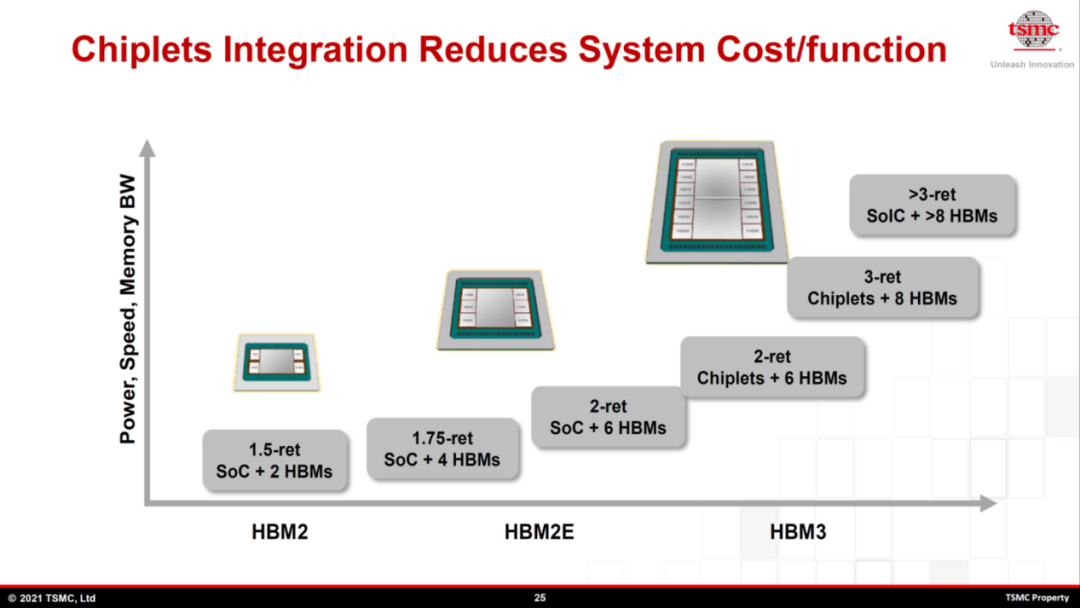

臺積電表示第5代技術(shù)的晶體管數(shù)量是第3代的20倍。新的封裝技術(shù)增加了3倍的中介層面積,使用了全新的TSV解決方案,更厚的銅連接線。目前,這項(xiàng)技術(shù)已經(jīng)用于制造AMD MI200“Aldebaran”專業(yè)計算卡,其中封裝了2顆GPU核心、8片HBM2e緩存。

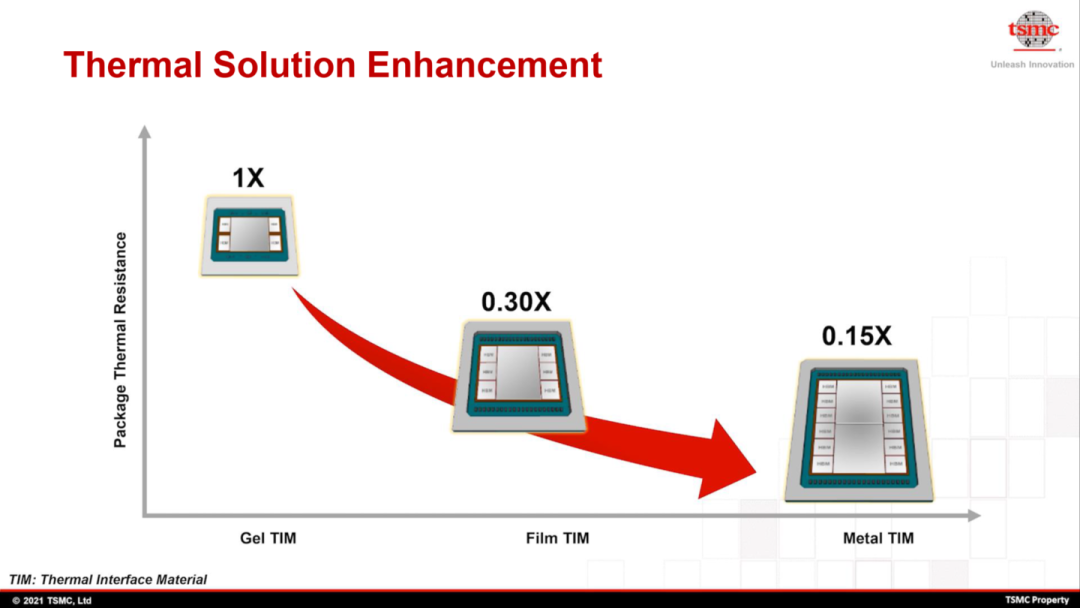

臺積電還表示,新技術(shù)同時也使用了性能更好的導(dǎo)熱方式,第5代技術(shù)使用了金屬導(dǎo)熱材料,熱阻降低至此前的0.15倍,有助于這類高性能芯片散熱。

臺積電目前還在開發(fā)第六代CoWoS封裝解決方案,以集成更多的小芯片和DRAM芯片,仍未確定最終方案,預(yù)計可以在同一封裝內(nèi)容納兩個計算芯片和八個或以上的HBM3 DRAM芯片,可能會在2023年推出。

CoWoS技術(shù)應(yīng)用很廣泛,英偉達(dá)的GP100、戰(zhàn)勝柯潔的AlphaGo背后的Google芯片TPU2.0都是采用CoWoS技術(shù),人工智能AI的背后也是有CoWoS的貢獻(xiàn)。目前,CoWoS已經(jīng)獲得NVIDIA、AMD、Google、XilinX、華為海思等高端芯片廠商的支持。

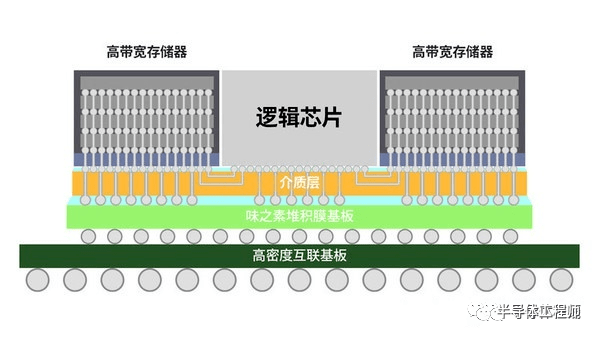

6.HBM

HBM(High-Bandwidth Memory )高帶寬內(nèi)存,主要針對高端顯卡市場。HBM使用了3D TSV和2.5D TSV技術(shù),通過3D TSV把多塊內(nèi)存芯片堆疊在一起,并使用2.5D TSV技術(shù)把堆疊內(nèi)存芯片和GPU在載板上實(shí)現(xiàn)互連。下圖所示為HBM技術(shù)示意圖。

HBM目前有三個版本,分別是HBM、HBM2和HBM2E,其帶寬分別為128 GBps/Stack、256 GBps/Stack和307 GBps/Stack,最新的HBM3還在研發(fā)中。

AMD、NVIDIA和海力士主推的HBM標(biāo)準(zhǔn),AMD首先在其旗艦顯卡首先使用HBM標(biāo)準(zhǔn),顯存帶寬可達(dá)512 GBps,NVIDIA也緊追其后,使用HBM標(biāo)準(zhǔn)實(shí)現(xiàn)1TBps的顯存帶寬。和DDR5相比,HBM性能提升超過了3倍,但功耗卻降低了50%。

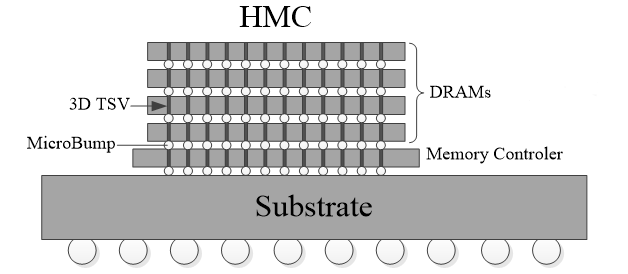

7.HMC

HMC(Hybrid Memory Cube)標(biāo)準(zhǔn)由美光主推,目標(biāo)市場是高端服務(wù)器市場,尤其是針對多處理器架構(gòu)。HMC使用堆疊的DRAM芯片實(shí)現(xiàn)更大的內(nèi)存帶寬。另外HMC通過3DIC異質(zhì)集成技術(shù)把內(nèi)存控制器(memory controller)集成到DRAM堆疊封裝里。以往內(nèi)存控制器都做在處理器里,所以在高端服務(wù)器里,當(dāng)需要使用大量內(nèi)存模塊時,內(nèi)存控制器的設(shè)計非常復(fù)雜。現(xiàn)在把內(nèi)存控制器集成到內(nèi)存模塊內(nèi),則內(nèi)存控制器的設(shè)計就大大地簡化了。最后,HMC使用高速串行接口(SerDes)來實(shí)現(xiàn)高速接口,適合處理器和內(nèi)存距離較遠(yuǎn)的情況(例如處理器和內(nèi)存在兩張不同的PCB板上)。

下圖所示為HMC技術(shù)示意圖。

對比HBM和HMC可以看出,兩者很相似,都是將DRAM芯片堆疊并通過3D TSV互連,并且其下方都有邏輯控制芯片,兩者的不同在于:HBM通過Interposer和GPU互連,而HMC則是直接安裝在Substrate上,中間缺少了Interposer和2.5D TSV。

在HMC堆疊中,3D TSV的直徑約為5~6um,數(shù)量超過了2000+,DRAM芯片通常減薄到50um,之間通過20um的MicroBump將芯片相連。

以往內(nèi)存控制器都做在處理器里,所以在高端服務(wù)器里,當(dāng)需要使用大量內(nèi)存模塊時,內(nèi)存控制器的設(shè)計非常復(fù)雜。現(xiàn)在把內(nèi)存控制器集成到內(nèi)存模塊內(nèi),則內(nèi)存控制器的設(shè)計就大大地簡化了。此外,HMC使用高速串行接口(SerDes)來實(shí)現(xiàn)高速接口,適合處理器和內(nèi)存距離較遠(yuǎn)的情況。

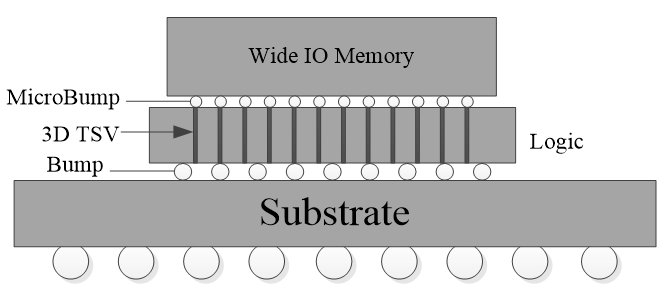

8.Wide-IO

Wide-IO(Wide Input Output)寬帶輸入輸出技術(shù)由三星主推,目前已經(jīng)到了第二代,可以實(shí)現(xiàn)最多512bit的內(nèi)存接口位寬,內(nèi)存接口操作頻率最高可達(dá)1GHz,總的內(nèi)存帶寬可達(dá)68GBps,是DDR4接口帶寬(34GBps)的兩倍。

Wide-IO通過將Memory芯片堆疊在Logic芯片上來實(shí)現(xiàn),Memory芯片通過3D TSV和Logic芯片及基板相連接,如下圖所示。

Wide-IO具備TSV架構(gòu)的垂直堆疊封裝優(yōu)勢,有助打造兼具速度、容量與功率特性的移動存儲器,滿足智慧型手機(jī)、平板電腦、掌上型游戲機(jī)等行動裝置的需求,其主要目標(biāo)市場是要求低功耗的移動設(shè)備。

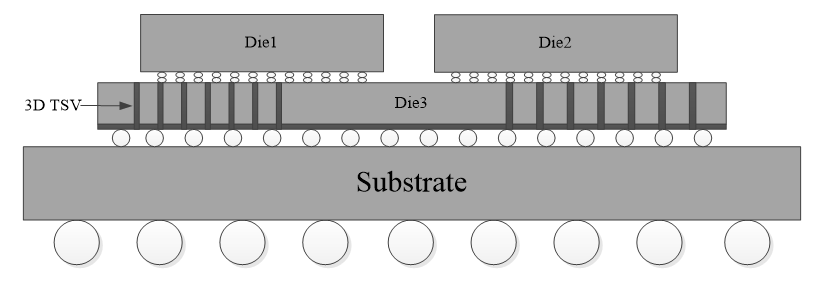

9.Foveros

除了前面介紹過的EMIB先進(jìn)封裝之外,Intel還推出了Foveros有源板載技術(shù)。在Intel的技術(shù)介紹中,F(xiàn)overos被稱作3D Face to Face Chip Stack for heterogeneous integration,三維面對面異構(gòu)集成芯片堆疊。

EMIB與Foveros的區(qū)別在于前者是2D封裝技術(shù),而后者則是3D堆疊封裝技術(shù),與2D的EMIB封裝方式相比,F(xiàn)overos更適用于小尺寸產(chǎn)品或?qū)?nèi)存帶寬要求更高的產(chǎn)品。其實(shí)EMIB和Foveros在芯片性能、功能方面的差異不大,都是將不同規(guī)格、不同功能的芯片集成在一起來發(fā)揮不同的作用。不過在體積、功耗等方面,F(xiàn)overos 3D堆疊的優(yōu)勢就顯現(xiàn)了出來。Foveros每比特傳輸?shù)臄?shù)據(jù)的功率非常低,F(xiàn)overos技術(shù)要處理的是Bump間距減小、密度增大以及芯片堆疊技術(shù)。

下圖所示是 Foveros 3D封裝技術(shù)示意圖。

首款Foveros 3D堆疊設(shè)計的主板芯片LakeField,它集成了10nm Ice Lake處理器以及22nm核心,具備完整的PC功能,但體積只有幾枚美分硬幣大小。

雖說Foveros是更為先進(jìn)的3D封裝技術(shù),但它與EMIB之間并非取代關(guān)系,英特爾在后續(xù)的制造中會將二者結(jié)合起來使用。

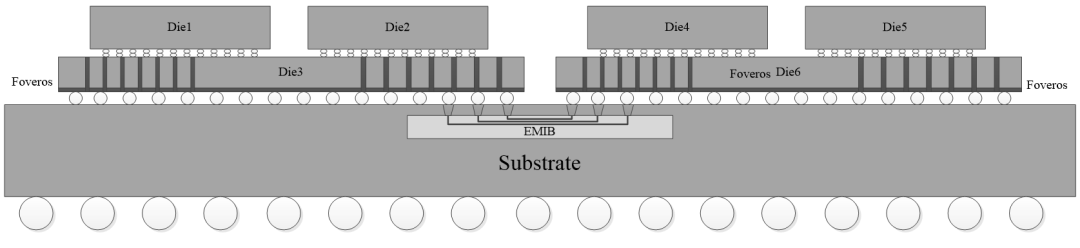

10.Co-EMIB(Foveros + EMIB)

Co-EMIB是EMIB和Foveros的綜合體,EMIB主要是負(fù)責(zé)橫向的連結(jié),讓不同內(nèi)核的芯片像拼圖一樣拼接起來,而Foveros則是縱向堆棧,就好像蓋高樓一樣,每層樓都可以有完全不同的設(shè)計,比如說一層為健身房,二層當(dāng)寫字樓,三層作公寓。

將EMIB和Foveros合并起來的封裝技術(shù)被稱作Co-EMIB,是可以具有彈性更高的芯片制造方法,可以讓芯片在堆疊的同時繼續(xù)橫向拼接。因此,該技術(shù)可以將多個3D Foveros芯片通過EMIB拼接在一起,以制造更大的芯片系統(tǒng)。下圖是Co-EMIB技術(shù)示意圖。

Co-EMIB封裝技術(shù)能提供堪比單片的性能,達(dá)成這個技術(shù)的關(guān)鍵,就是ODI(Omni-Directional Interconnect)全向互連技術(shù)。ODI具有兩種不同型態(tài),除了打通不同層的電梯型態(tài)連接外,也有連通不同立體結(jié)構(gòu)的天橋,以及層之間的夾層,讓不同的芯片組合可以有極高的彈性。ODI封裝技術(shù)可以讓芯片既實(shí)現(xiàn)水平互連,又可以實(shí)現(xiàn)垂直互連。

Co-EMIB通過全新的3D + 2D封裝方式,將芯片設(shè)計思維也從過去的平面拼圖,變成堆積木。因此,除了量子計算等革命性的全新計算架構(gòu)外,CO-EMIB可以說是在維持并延續(xù)現(xiàn)有計算架構(gòu)與生態(tài)的最佳作法。

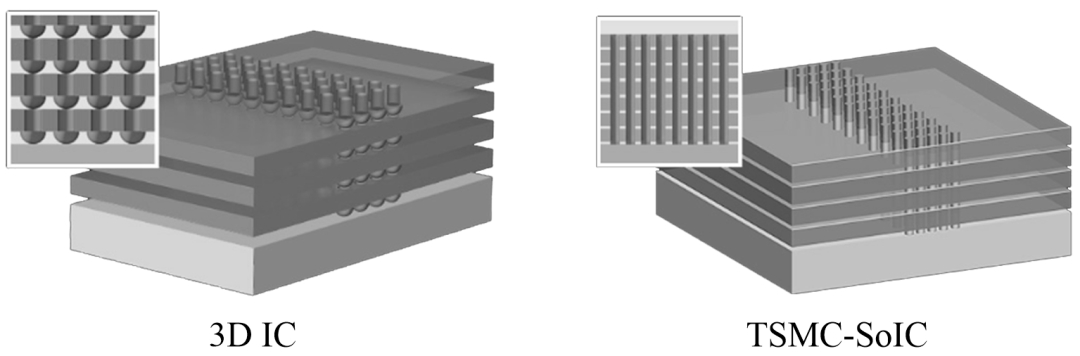

11.SoIC

SoIC也稱為TSMC-SoIC,是臺積電提出的一項(xiàng)新技術(shù)——集成片上系統(tǒng)(System-on-Integrated-Chips),預(yù)計在2021年,臺積電的SoIC技術(shù)就將進(jìn)行量產(chǎn)。

究竟什么是SoIC?所謂SoIC是一種創(chuàng)新的多芯片堆棧技術(shù),能對10納米以下的制程進(jìn)行晶圓級的集成。該技術(shù)最鮮明的特點(diǎn)是沒有凸點(diǎn)(no-Bump)的鍵合結(jié)構(gòu),因此具有有更高的集成密度和更佳的運(yùn)行性能。

SoIC包含CoW(Chip-on-wafer)和WoW(Wafer-on-wafer)兩種技術(shù)形態(tài),從TSMC的描述來看,SoIC就一種WoW晶圓對晶圓或CoW芯片對晶圓的直接鍵合(Bonding)技術(shù),屬于Front-End 3D技術(shù)(FE 3D),而前面提到的InFO和CoWoS則屬于Back-End 3D技術(shù)(BE 3D)。TSMC和Siemens EDA(Mentor)就SoIC技術(shù)進(jìn)行合作,推出了相關(guān)的設(shè)計與驗(yàn)證工具。

下圖是3D IC和SoIC集成的比較。

具體的說,SoIC和3D IC的制程有些類似,SoIC的關(guān)鍵就在于實(shí)現(xiàn)沒有凸點(diǎn)的接合結(jié)構(gòu),并且其TSV的密度也比傳統(tǒng)的3D IC密度更高,直接通過極微小的TSV來實(shí)現(xiàn)多層芯片之間的互聯(lián)。如上圖所示是3D IC和SoIC兩者中TSV密度和Bump尺寸的比較。可以看出,SoIC的TSV密度要遠(yuǎn)遠(yuǎn)高于3D IC,同時其芯片間的互聯(lián)也采用no-Bump的直接鍵合技術(shù),芯片間距更小,集成密度更高,因而其產(chǎn)品也比傳統(tǒng)的3D IC有更高的功能密度。

12.X-Cube

將芯片從2D平鋪封裝改成3D立體式堆疊式封裝已經(jīng)成為目前半導(dǎo)體業(yè)界的共識,這種在第三維度上進(jìn)行拓展的封裝技術(shù)能夠有效降低整個芯片的面積,提升集成度。目前業(yè)界領(lǐng)頭羊都在3D封裝技術(shù)上面努力著,前有臺積電的CoWoS(實(shí)際上是2.5D),后有Intel的Foveros,而三星自家的3D封裝技術(shù)就名為X-Cube。

X-Cube的全稱是eXtended-Cube,意為拓展的立方體。在Die之間的互聯(lián)上面,它使用的是成熟的TSV工藝,即硅穿孔工藝。目前三星自己的X-Cube測試芯片已經(jīng)能夠做到將SRAM層堆疊在邏輯層之上,通過TSV進(jìn)行互聯(lián),制程是他們自家的7nm EUV工藝。三星表示這樣可以將SRAM與邏輯部分分離,更易于擴(kuò)展SRAM的容量。另外,3D封裝縮短了Die之間的信號距離,能夠提升數(shù)據(jù)傳輸速度并提高能效。

X-Cube可靈活應(yīng)用于未來芯片之上,包括5G、AI和高性能計算等領(lǐng)域的芯片均可使用該技術(shù)。三星表示X-Cube已經(jīng)在自家的7nm和5nm制程上面通過了驗(yàn)證,計劃和無晶圓廠的芯片設(shè)計公司繼續(xù)合作,推進(jìn)3D封裝工藝在下一代高性能應(yīng)用中的部署。

X-Cube技術(shù)大幅縮短了芯片間的信號傳輸距離,提高數(shù)據(jù)傳輸速度,降低功耗,并且還可以按客戶需求定制內(nèi)存帶寬及密度。

2021年5月,三星宣布下一代2.5D封裝技術(shù)Interposer-Cube4(I-Cube4)即將面世,可將一個或多個Logic Chip和多個高帶寬內(nèi)存芯片(HBM)使用硅中介層,從而使多個芯片排列封裝在一個芯片里。

到了2021年11月,三星又推出了全新2.5D封裝解決方案H-Cube(Hybrid Substrate Cube,混合基板封裝),專用于需要高性能和大面積封裝技術(shù)的HPC、人工智能、數(shù)據(jù)中心和網(wǎng)絡(luò)產(chǎn)品等領(lǐng)域。

三星電子透露,H-Cube技術(shù)是由三星晶圓代工廠和Amkor Technology公司聯(lián)合開發(fā),采用在高端ABF基板上疊加大面積的HDI基板的結(jié)構(gòu),通過將連接芯片和基板的焊錫球間距縮短35%,縮小ABF基板的尺寸,同時在ABF基板下添加HDI基板以確保與系統(tǒng)板的連接,從而進(jìn)一步實(shí)現(xiàn)更大的2.5D封裝。

來源:SiP與先進(jìn)封裝技術(shù)等網(wǎng)絡(luò)內(nèi)容綜合

審核編輯:湯梓紅

電子發(fā)燒友App

電子發(fā)燒友App

評論