本文介紹了3D-IC中三個不同層次的3D是什么。

?66年前的一個炎炎夏日,在德州達拉斯一間空蕩蕩的辦公室里,一位高大的身影頗顯孤單,他就是TI剛入職的新員工杰克?基爾比,他正在苦思冥想電路小型化的問題。 ? 此時正值工廠停工放假,同事們大多都去休假了。基爾比正在思考能否將電路所需的所有器件制作在一塊半導體材料上? ? 幾個月后,基爾比實現了他的構想,人類歷史上第一塊集成電路就這么誕生了。

? 自從1958集成電路發明以來,集成電路給人類文明帶來難以估量的巨大的進步。“為現代信息技術奠定了基礎”是2000年諾貝爾物理學獎給予杰克?基爾比發明集成電路的中肯評價。 ? 今天,我們甚至可以說:“集成電路為現代科技奠定了基礎”。試想,沒有集成電路,人類現在的科技會退回到何種地步? ?

?從時間到空間? ?

集成電路的基本單元是晶體管,我稱之為功能細胞。如何在有限的面積或體積內集成更多的晶體管成為集成電路發展的關鍵。 ? 1965年,戈登?摩爾提出摩爾定律,指出集成電路上的器件數量每隔十八個月將翻一番,從時間上對集成電路的發展做出了預言。 ? 在人類的認知中,時間和空間是不可分割的,我們常稱之為時空。時間有一個維度,空間有三個維度,合稱四維時空。 ? 時間具有單向性,只能向前發展,空間的每個維度都可雙向發展。當事物的發展在時間受到限制或者約束時,則會在空間上尋找突破,謂之以空間換時間,集成電路的發展也正是如此。 ?

摩爾定律中,我們關注的是晶體管的數量隨時間以指數規律增加,隨著摩爾定律難以為繼,今天的集成電路,我們更關注如何在有限的空間內制造更多的晶體管。 ?

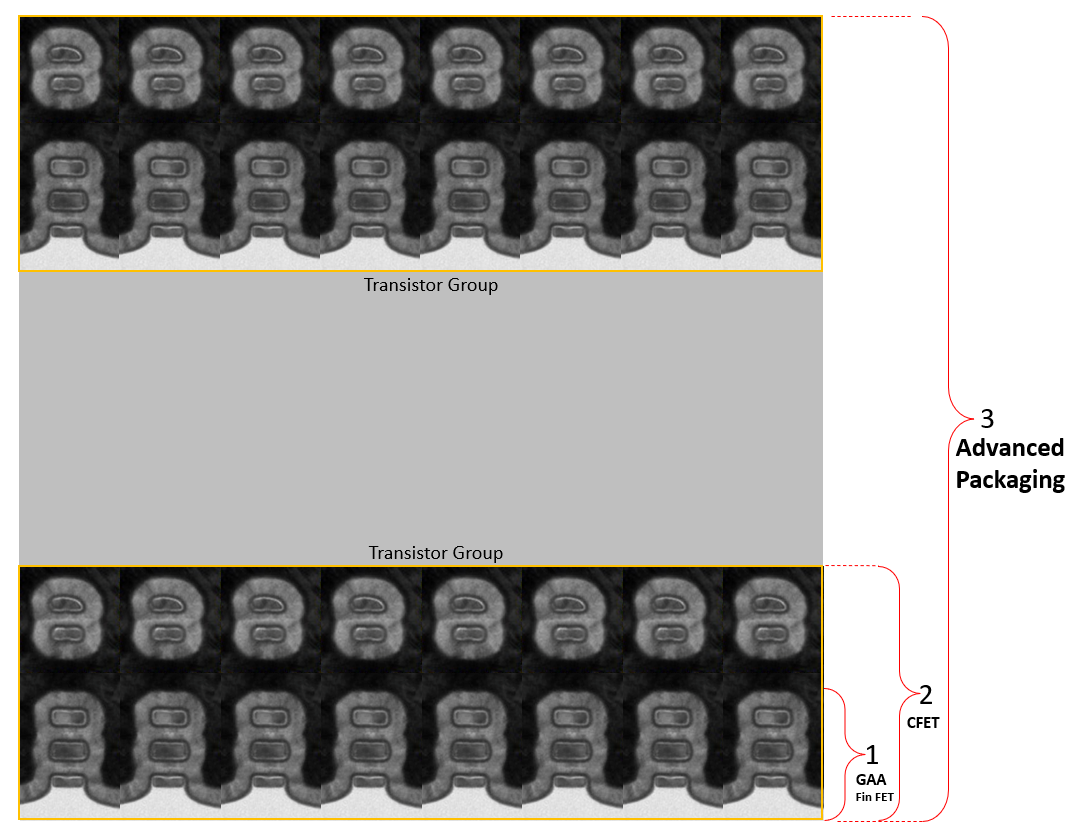

3D的必由之路? ? 空間有三個維度六個方向,要想在有限的空間內集成制造更多的晶體管,必須窮盡三個維度六個方向。 ? 集成電路自發明以來,就是在晶圓平面上制造晶體管并進行互連。為了在有限的面積內制造更多的晶體管,晶體管的尺寸需要越做越小,直到有一天,平面晶體管縮小的已經無法正常工作時,新的類型的晶體管FinFET取代了平面晶體管,后來又發展出GAA晶體管,這兩者都屬于晶體管結構上的3D化,我們稱之為3D-IC中第一層次的3D。 ? 晶體管結構上的3D化并不能完全解決問題,因此3D-IC中第二層次的3D也出現了,即晶體管堆疊,比較有代表性的是CFET。

? 同時,人們發現在先進封裝中,將芯片堆疊也能有效提高晶體管的集成密度,即在有效的空間內集成更多的晶體管,這就是3D-IC第三個層次的3D。 ? 對于城市的發展來說,要想提高城市的居住密度,就需要建造高樓大廈。對于集成電路來說,要提高集成密度,必須采用3D集成。 ? 下面,我們就對3D-IC中三個層次的3D進行逐一解析。 ?

?3D層次1??晶體管結構的3D化?

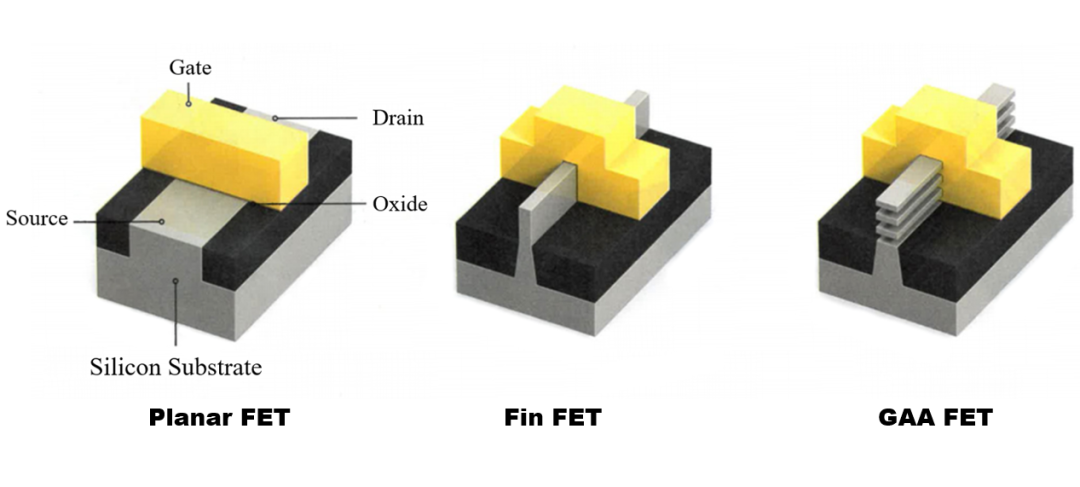

集成電路中用到的晶體管,通常是場效應晶體管Field-Effect Transistor,簡稱為FET,此類晶體管柵極Gate的最初形態是平面狀,被稱為平面晶體管 Planar FET。其特征尺寸(Feature Size)指的是柵極的寬度(Gate Width),即MOS器件的溝道長度(Channel Length)。

隨著晶體管尺寸的逐步縮小,其特征尺寸也在不斷縮小,當特征尺寸到了22nm,平面晶體管由于其柵極對于溝道的控制能力較弱而出現短溝道效應,逐漸被一種新型的晶體管所取代,即鰭式場效應晶體管(Fin FET)。此時,特征尺寸不再以柵極的寬度作為其度量標準,而是代表著該工藝下晶體管密度和上一代工藝相比較的等效尺寸。 ? 例如同樣面積的芯片,其晶體管數量增加了一倍,此時,此芯片晶體管的特征尺寸則為上一代的特征尺寸的0.7,以此類推。當然在不同的半導體廠家,對特征尺寸的定義也不盡相同,例如Intel和TSMC的定義就不完全相同。 ? 從平面型晶體管Planar FET到鰭式晶體管FinFET,是晶體管結構的重大改變,晶體管內部結構由平面走向3D,我們稱之為晶體管結構的3D化。 ? 到了3nm,Fin FET對電流的控制能力也有些力不從心,就需要采用堆疊納米片型晶體管GAA FET。GAA采用柵極環繞溝道的結構,柵極對于溝道的控制能力比Fin FET又有所增強,?使得晶體管能夠在更小的空間內實現更佳的性能。 ? 下圖為Planar FET、Fin FET、GAA FET三種晶體管微觀結構比較。 ?

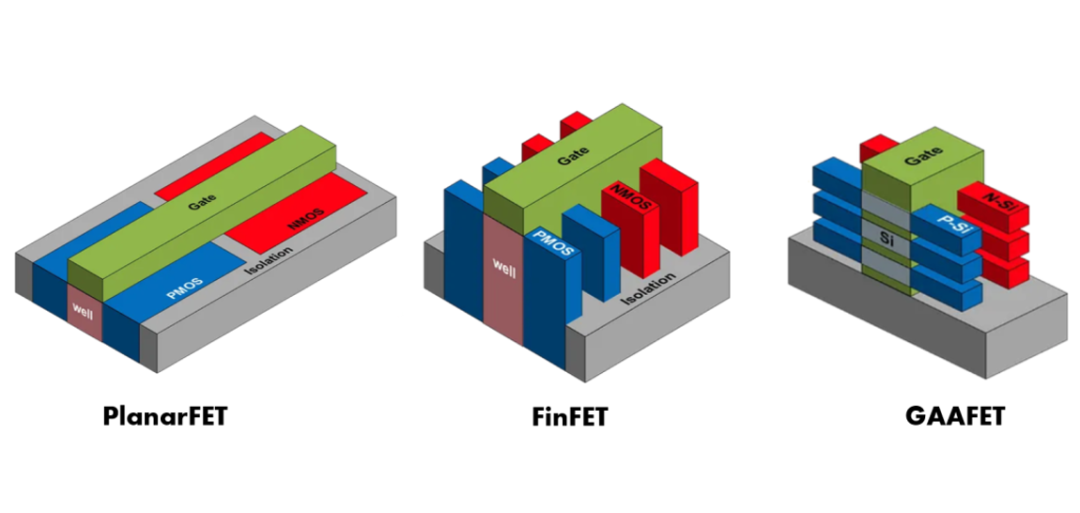

下圖是將NMOS晶體管和PMOS晶體管并列制造的三種類型的晶體管的結構比較,集成電路的最常見的基本單元通常由NMOS晶體管和PMOS晶體管共同組成。 ?

? 目前在先進工藝中,Fin FET是主流,GAA FET則后來居上,并且在3nm后有望全面取代Fin FET,Planar FET則繼續在大尺寸器件中發揮余熱。 ?

3D層次2??晶體管的3D集成?

從上面的描述中,我們可以看出,當今主流的芯片,其晶體管的結構已經全面實現3D化。

在芯片中,晶體管只有薄薄的一層,能否制造多層晶體管,將它們堆疊起來?這就是下面我們要將說的:晶體管的堆疊,即晶體管的3D集成。

隨著摩爾定律的不斷發展,芯片制程也愈發接近物理極限,為了能夠進一步增加單位面積上的器件數量,業內開始嘗試將實現3D結構的晶體管再進行堆疊,提出了采用垂直堆疊晶體管的CFET。

CFET?

CFET互補場效應晶體管,被視為1nm以下制程的關鍵要素,是繼FinFET和GAA之后的新一代的晶體管技術。

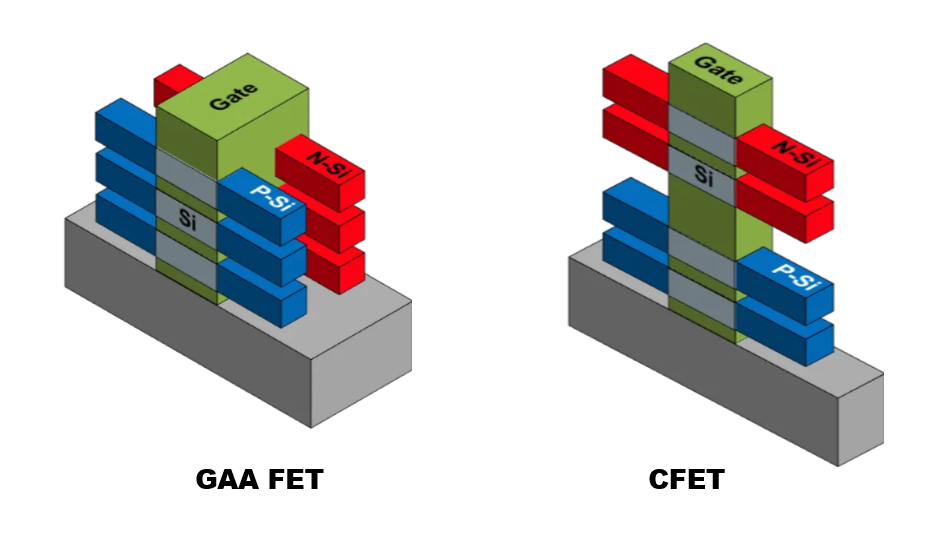

下圖是GAA FET和CFET的結構比較,可以看出GAA FET中NMOS管和PMOS管并排放置,位于同一個平面,而在CFET中,NMOS管和PMOS管垂直堆疊,NMOS管位于PMOS管之上,其面積占用僅為GAA FET的一半。 ?

因此,采用CFET垂直堆疊架構的芯片,相較采用GAAFET架構的芯片,面積最多能縮小50%。

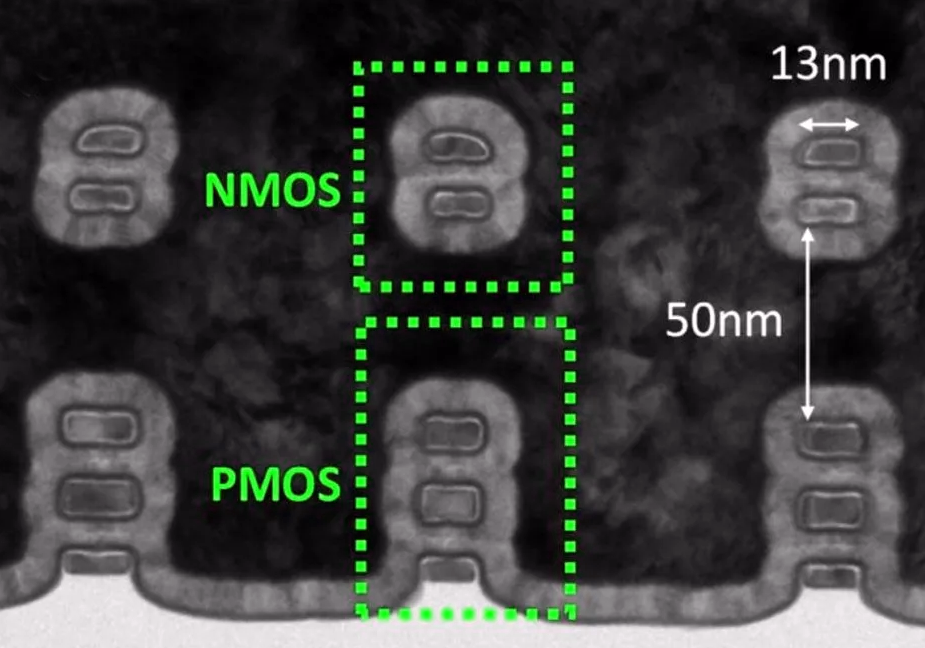

下圖所示為CFET晶體管層的剖面圖,NMOS管位于PMOS管之上。

? CFET將PMOS管和NMOS管結合在了一起,使得開關速度和驅動能力具有互補性,從而提升了晶體管的整體性能。CFET讓業界看到了晶體管結構新的發展前景。 ? 目前,CFET制程需要解決多層晶體管堆疊帶來的大量的技術挑戰,保守估計,CFET結構需要8-10年才能投入商用。 ? 此后,在CFET的基礎上是否可以再堆疊更多層晶體管,我們將拭目以待。 ?

3D層次3??晶體管群的3D集成?

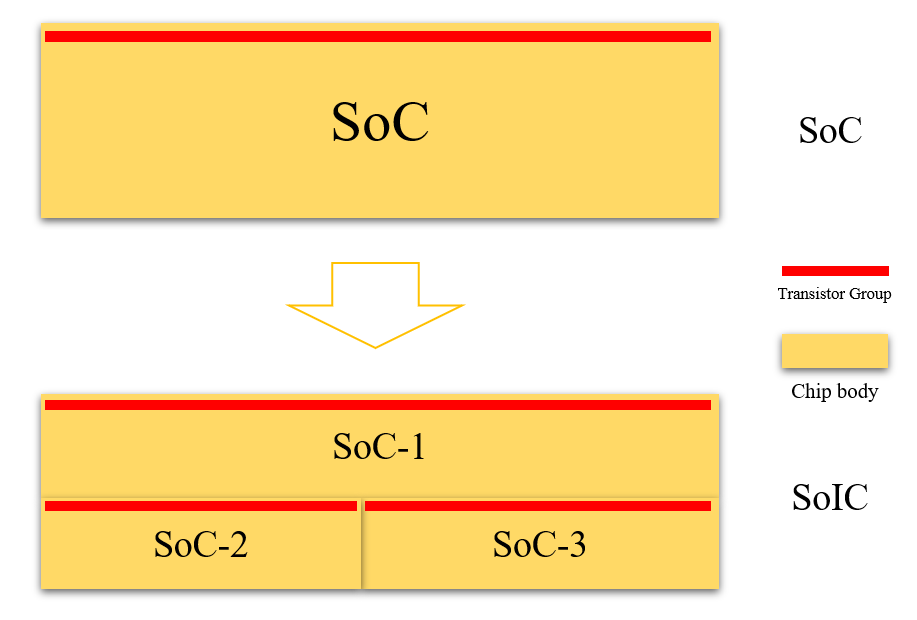

這篇文章中,我采用了一個新的名詞,晶體管群(Transistor Group),是指在特定工藝下完成的一顆芯片中晶體管的總稱。例如一顆SoC中的所有晶體管組成一個SoC晶體管群,一顆Chiplet中的所有晶體管組成一個Chiplet晶體管群。晶體管群通常采用相同的工藝一次制造完成。 ? 在一顆芯片中,晶體管群及其互連所占的體積,我稱之為有效功能體積EFV(Effective Function Volume),和整個芯片本身的體積相比,有效功能體積所占的比例并不大。 ? 通過晶圓減薄然后再進行3D堆疊可以提高有效功能體積的占比,從而提升系統的功能密度。 ? 下圖所示為SoC和SoIC的比較, 其中紅色為晶體管群所占體積,黃色為芯片體積。其中SoC中包含1個晶體管群,SoIC中包含3個晶體管群。 ?

可以看出同樣的體積下,SoIC中的3個晶體管群所占的體積比例更大,其有效功能體積EFV更大。因此,同樣的工藝下,SoIC的功能密度更高,即在相同的體積中可集成更多的晶體管。同時,SoIC中的3個晶體管群可采用不同的工藝節點制造,因此其靈活性更高。

晶體管群的3D集成是當今集成電路最為熱點的技術,有人稱為3DIC,有人稱為先進封裝,也有人稱為Multi-Die或者SiP技術。

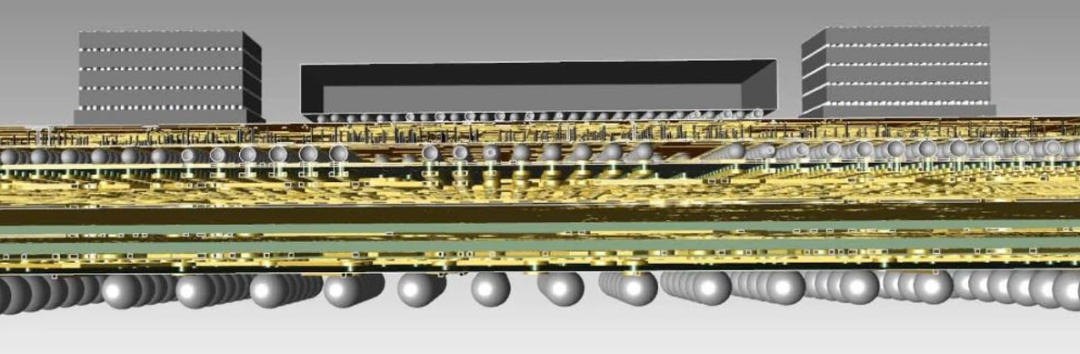

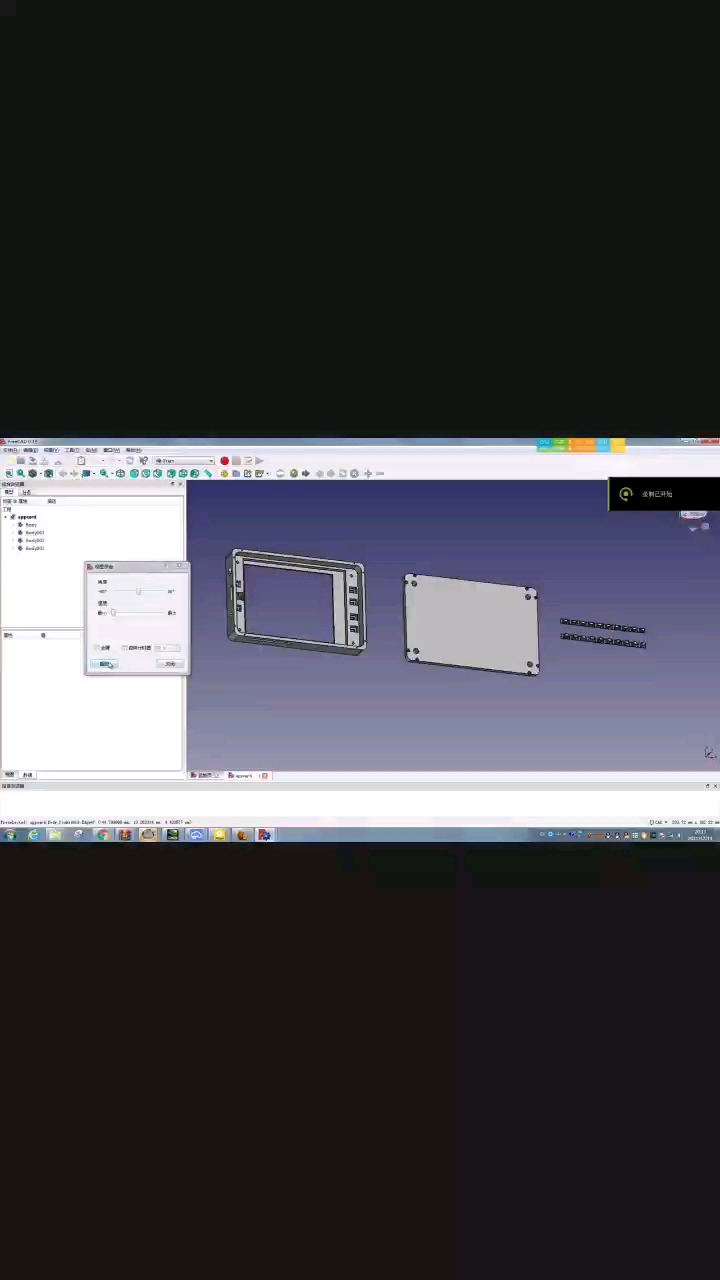

下圖所示為典型的HBM先進封裝在EDA工具中的設計截圖。

總 結

從晶體管結構的3D化到晶體管的3D集成再到晶體管群的3D集成,分為三個層次的3D,它們互為補充,并不沖突。最終的發展目標是在三個層次都實現3D化。 ? 第一個層次的3D,晶體管結構的3D化已經通過FinFET和GAA實現,針對不同的工藝節點需要,靈活采用Fin FET,GAA FET或者Planar FET。 ? 第二個層次的3D,晶體管的3D集成,即晶體管堆疊,目前已經論證可通過CFET實現,但由于其工藝上存在著較大的技術挑戰,需要8-10年才可實現商用。 ? 第三個層次的3D,晶體管群的3D集成,可通過先進封裝技術實現,目前的3DIC多指的是這一類。先進封裝是在晶體管群制造完成后,需要經過晶圓減薄,TSV,RDL,Hybrid bonding等技術將晶體管群堆疊并互連起來,目前,其關鍵技術為TSV,Hybrid bonding 等。 ? 從晶體管結構的3D化到晶體管的3D集成(晶體管堆疊)再到晶體管群的3D集成(晶體管群堆疊),三個層次的3D造就了最終極的3D-IC。 ?

3D-IC中三個層次的3D

審核編輯:黃飛

?

電子發燒友App

電子發燒友App

評論