Cadence宣布業內首個DDR4 Design IP解決方案在28納米級芯片上得到驗證

2012-09-10 09:53:24 1403

1403 賽靈思的20納米產品以備受市場肯定的28納米制程突破性技術為基礎,提供超越一個技術世代的系統效能、功耗和可編程系統整合度,繼續超越下一代!

2012-12-03 09:48:01 876

876 全球電子設計創新領先企業Cadence設計系統公司(NASDAQ: CDNS),近日推出新版本Incisive Enterprise Simulator,該版本將復雜SoC的低功耗驗證效率提高了30

2013-05-14 10:31:40 1832

1832 Cadence系統芯片開發工具已經通過臺積電(TSMC) 16納米 FinFET制程的設計參考手冊第0.1版與 SPICE 模型工具認證,客戶現在可以享用Cadence益華電腦流程為先進制程所提供的速度、功耗與面積優勢。

2013-06-06 09:26:45 1236

1236 艾邁斯歐司朗與創邁思聯合發布演示方案,實現OLED屏下超高安全級別人臉認證 ? ?????? 發布完整的智能手機集成解決方案聯合演示,包括OLED屏下方案; ?????? 解決方案包括結合了隱蔽

2022-06-28 11:46:04 797

797

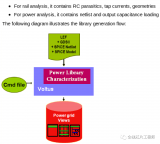

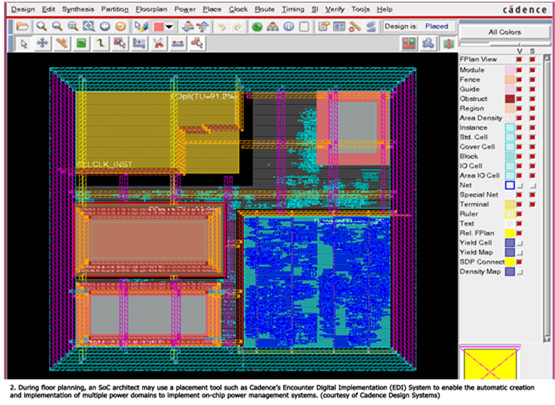

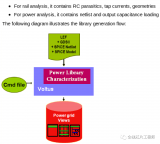

Cadence功耗分析首先需生成power grid library

2023-09-06 09:47:50 859

859

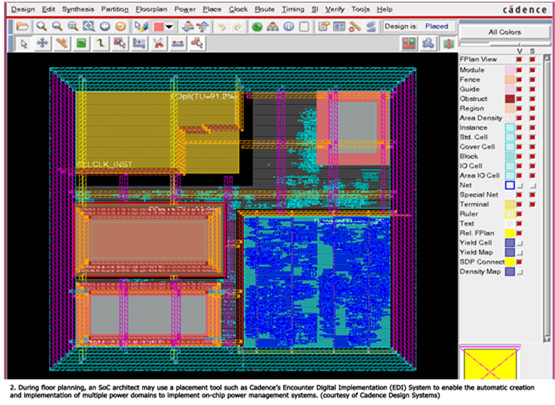

全球電子設計創新領先企業Cadence設計系統公司(NASDAQ: CDNS)今天宣布,全球領先的晶圓廠之一中國中芯國際[0.40 2.56%]集成電路制造有限公司(SMIC)推出一款采用Cadence Encounter數字技術和SMIC

2012-04-11 09:44:30 825

825 Cadence設計系統公司發布了Cadence Allegro系統互連設計平臺針對印刷電路板(PCB)設計進行的全新產品和技術增強。改進后的平臺為約束驅動設計提供了重要的新功能,向IC、封裝和板

2018-11-23 17:02:55

。” Cadence推出的RFSiP套件為無線通信應用的RFSiPs設計提供了自動化和加速設計流程的最新產品和技術。它同時提供了基于802.11b/g無線局域網設計的成熟的SiP實施方法,能夠低風險地實現

2008-06-27 10:24:12

Cadence仿真流程Cadence仿真流程[/hide][此貼子已經被作者于2009-8-16 13:47:51編輯過]

2009-08-16 13:47:03

授權使用正確的低功耗分析和最優化引擎,這些功能要求集成在整個設計流程中。此外,在65納米芯片設計中,約有50%的設計工作是混合信號設計。傳統的模擬設計流程與數字工作處于完全隔離的狀態,如何把模擬和數字

2019-05-20 05:00:10

數據透傳是選擇低功耗WiFi模塊還是低功耗藍牙模塊好?

2021-01-04 06:55:35

物聯網的興起帶動越來越多的公司選用無線互聯產品,在無線互聯中低功耗藍牙(BLE)是不可缺少的用來支持相互連接的產品之一,因為低功耗藍牙無需網關就可以直接與智能終端通信,有比較好的人機交互體驗,特別是藍牙MESH發布,可以讓更多結點在同一個網絡互通。 許多工程師不清楚如何選型;有什么技巧嗎?

2021-03-06 08:22:49

本帖最后由 eehome 于 2013-1-5 10:02 編輯

數字語音解碼器的低功耗設計方案

2012-08-20 12:50:40

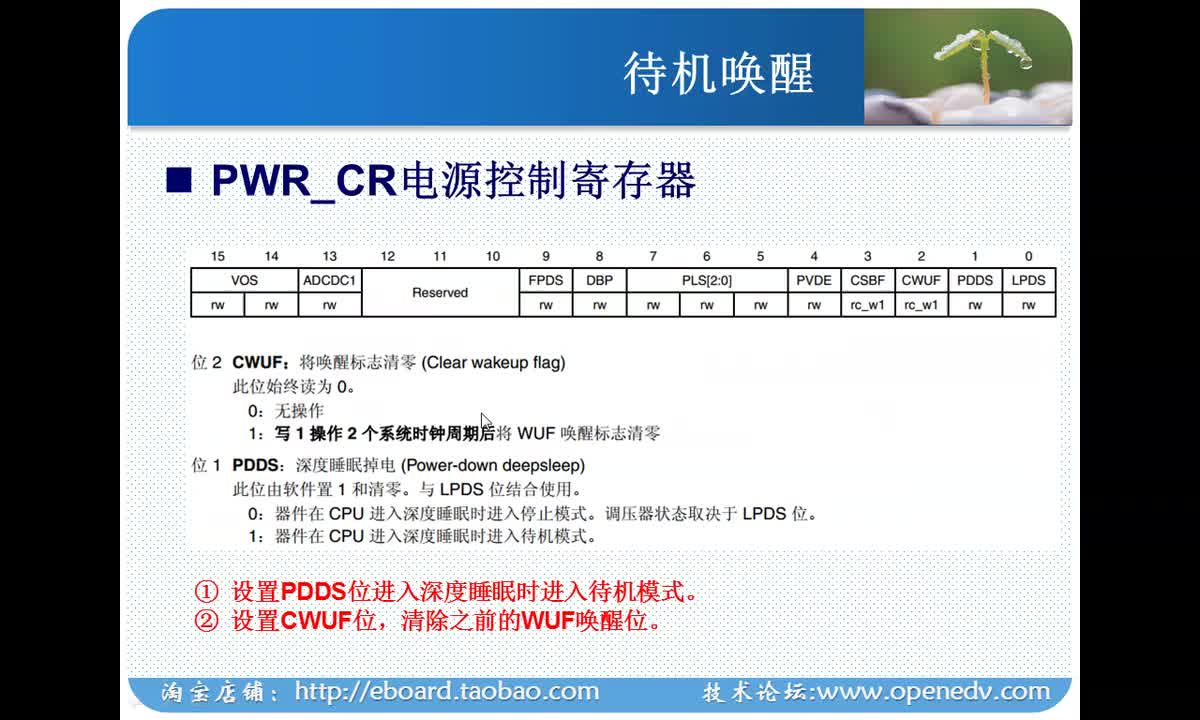

程序使用定時喚醒采樣方式,每隔一段時間喚醒,進行AD采樣。問題在于,如果不使用內部2.5V基準電壓,進入低功耗時候,電流在20uA左右;使用內部2.5V基準電壓,進入低功耗前關閉(ADC12CTL0

2018-06-21 14:54:10

` Nordic發布了nRF8002低功耗藍牙單芯片解決方案,成本更低,功耗更低,更簡單應用于無線藍牙智能標簽和配件(如手鏈,墜子,鑰匙扣,小玩具和臂章等)。 要配置μBlue? nRF8002

2012-03-26 14:20:38

Port Pins,它說“有時在數字輸入時將數字輸入配置為模擬輸入是適當的和可能的必須進入低功耗狀態。“我不太理解這一點,關于數字輸入必須如何進入低功耗狀態。”請你闡述一下這一點好嗎?如果有一些例子的話會很有幫助的。謝謝!

2020-04-30 09:25:33

,通過發行所謂的“虛擬資產”、“數字資產”、“虛擬貨幣”等方式吸收資金,已經侵害到公眾的合法權益了。五部委聯合發布風險提示,讓無數人拍手叫好!有網友甚至吐出心聲:確實該整頓了,這些打著“給大眾迅速賺大錢

2018-08-29 13:36:47

今天更新一篇數字IC低功耗設計方法總結,內容參考的是郭煒老師的書:《SoC設計方法與實現(第3版)》,希望能給大家帶來幫助~

2021-07-29 06:38:58

芯片設計解決方案供應公司微捷碼(Magma)設計自動化有限公司近日宣布,已和專為消費性應用提供超低功耗65納米FPGA(現場可編程門陣列)技術的先驅者SiliconBlue科技公司正式簽定技術合作

2019-07-26 07:29:40

現在電子產品一般都有要求低功耗,不同的MCU,進入低功耗的處理流程可能不一樣,但是大致的流程還是一樣。現對MCU進入低功耗的處理流程大致如下:(1)關閉MCU之外的外設電源,例如:RS485、CAN

2021-11-01 08:10:03

一半,而性能提高兩倍。通過選擇一個高性能低功耗的工藝技術,一個覆蓋所有產品系列的、統一的、可擴展的架構,以及創新的工具,賽靈思將最大限度地發揮 28 納米技術的價值, 為客戶提供具備 ASIC 級功能

2019-08-09 07:27:00

為什么需要低功耗設計?如何實現數字IC低功耗的設計?

2021-11-01 06:37:46

單位。中科院計算技術研究所:負責設計驗證及測試綜合 SIG,與中科鑒芯(北京)科技有限責任公司聯合發布故障仿真器 v1.0;中科院微電子研究所:負責器件模型與參數提取 SIG、工藝模型及 PDK SIG

2022-06-24 15:17:14

2月19日,在新華社新媒體中心與搜狗公司戰略合作簽約儀式上,搜狗公司與新華社新媒體中心聯合發布了全球首個站立式AI合成主播,新的AI合成主播將從過去的“坐著播新聞”升級成結合肢體動作的“站立

2019-02-25 09:28:26

本資料是關于如何采用低功耗28nm降低系統總成本

2012-07-31 21:25:06

Cadence 仿真流程:第一章 在Allegro 中準備好進行SI 仿真的PCB 板圖1)在Cadence 中進行SI 分析可以通過幾種方

2008-07-12 08:56:05 0

0

低功耗數字VLSI設計:概覽:

2009-07-25 16:44:42 0

0 cadence 視頻教程 (第28課):adence SPB 15.7 視頻教程,手把手教你學習cadence軟件使用方法。本套視頻教程是于博士信號完整性研究網于爭博士主講。從一個工程師的角度出發講解軟件的操

2009-09-16 19:02:12 0

0 Tensilica 日前宣布與Cadence 合作,根據Tensilica 的330HiFi 音頻處理器和388VDO 視頻引擎,為其多媒體子系統建立一個通用功耗格式(CPF)的低功耗參考設計流程。Cadence 和Tensilica公司的工

2009-12-04 13:54:39 32

32 安富利與賽普拉斯聯合發布Spartan-3A FPGA評估套件升級版

安富利公司旗下之安富利電子元件部 (Avnet Electronics Marketing) 美洲業務區與賽普拉斯半導體公

2008-09-25 07:55:47 687

687 2009年3月4日,Cadence設計系統公司今天宣布生物指紋安全解決方案領先廠商UPEK®, Inc.已經整合其設計流程,并選擇Cadence®作為其全芯片數字、模擬與混合信號設計的

2009-03-05 12:14:18 519

519

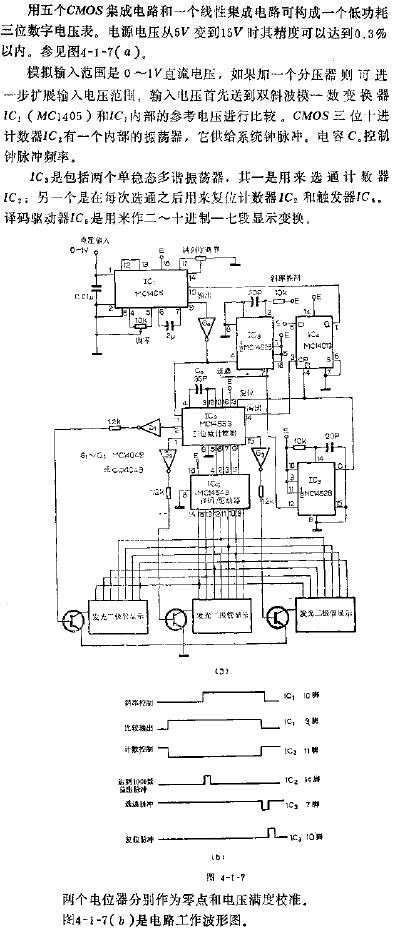

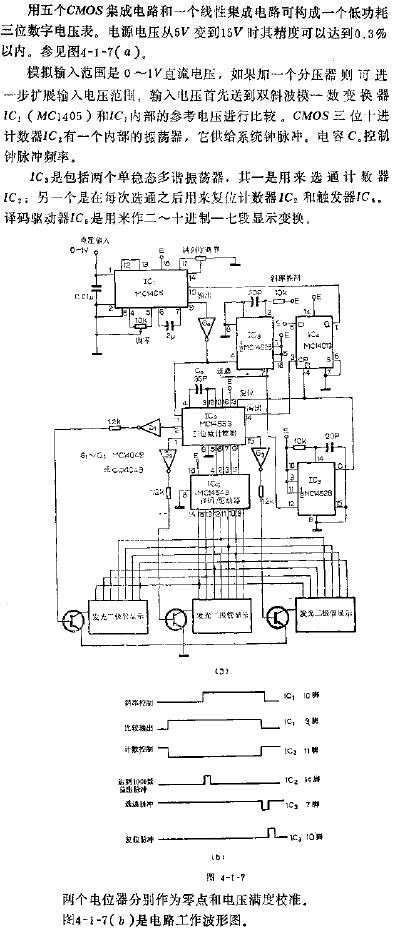

低功耗數字電壓表

2009-04-10 10:15:58 585

585

中芯國際采用Cadence DFM解決方案用于65和45納米 IP/庫開發和全芯片生產

Cadence 模型化的 Litho Physical 和 Litho Electrical

2009-10-19 17:48:11 461

461 中芯國際(SMIC)和Cadence 共同推出用于65納米的低功耗解決方案Reference Flow 4.0

完全集成的能效型流程令快速、輕松地設計低功耗尖端器件成為可能

2009-10-31 07:48:01 1228

1228 中芯國際(SMIC)和Cadence共同推出用于65納米的低功耗解決方案Reference Flow 4.0

全球電子設計創新領先企業Cadence設計系統公司今天宣布推出一款全面的低功耗設計流程,面向

2009-11-04 17:05:17 589

589 SIG發布新版低功耗藍牙規范

藍牙技術聯盟(Bluetooth Special Interest Group,SIG)日前推出采用低功耗版本藍牙核心規范4.0版本的升級版藍牙低功耗無線技術,將為具備低成本、

2009-12-30 08:52:37 1153

1153 臺積電與聯電大客戶賽靈思合作28納米產品

外電引用分析師資訊指出,聯電大客戶賽靈思(Xilinx)3月可能宣布與臺積電展開28納米制程合作;臺積電28納米已確定取得富

2010-01-19 15:59:55 1058

1058 統一工藝和架構,賽靈思28納米FPGA成就高性能和低功耗的完美融合

賽靈思公司(Xilinx)近日宣布,為推進可編程勢在必行之必然趨勢,正對系統工程師在全球發布賽靈思

2010-03-02 08:48:51 576

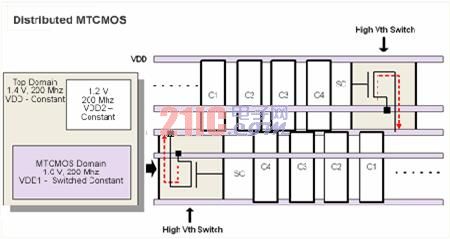

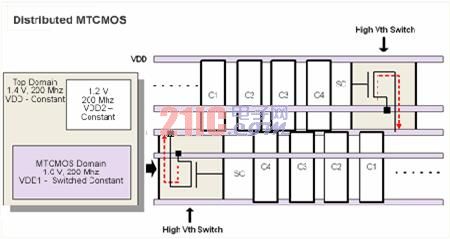

576 根據貫穿整個IC實現流程的集成化低功耗設計技術策略

降低功耗是現代芯片設計最具挑戰性需求之一。采用單點工具流程時,往往只有到了設計流程后期階段才會去考慮降

2010-04-21 10:54:28 651

651

微捷碼(Magma®)設計自動化有限公司日前宣布,一款經過驗證的支持Common Platform™聯盟32/28納米低功耗工藝技術的層次化RTL-to-GDSII參考流程正式面市。

2011-01-26 09:44:09 894

894 本文基于IEEEl801標準Uni-fied Power Format(UPF),采用Synopsys和Mentor Graphics的EDA工具實現了包括可測性設計在內的“從RTL到GDSII”的完整低功耗流程設計。本論文第1部分描述了低功耗技術和術語

2011-03-11 11:33:55 1621

1621

即將上市的這種新流程支持Cadence的硅實現方法,專注于獨一無二且普遍深入的設計意圖、提取與從RTL到GDSII,然后到封裝。硅實現是EDA360構想的一個關鍵組成部分。

2011-06-28 09:44:23 455

455 三星電子有限公司使用Cadence統一數字流程,從RTL到GDSII,成功實現了20納米測試芯片的流片

2011-07-27 08:47:49 967

967 全球電子設計創新領先企業Cadence設計系統公司(NASDAQ: CDNS),宣布Giantec Semiconductor Corp.已采用Cadence? Virtuoso?統一定制/模擬(IC6.1)以及Encounter?統一數字流程生產其混合信號芯片。

2011-09-27 11:06:26 1483

1483 本白皮書介紹了有關賽靈思 28 nm 7 系列 FPGA 功耗的幾個方面,其中包括臺積電 28nm高介電層金屬閘 (HKMG) 高性能低功耗(28nm HPL 或 28 HPL)工藝的選擇。 本白皮書還介紹了 28 HPL 工藝提供

2012-03-07 14:43:44 41

41 Cadence 設計系統公司日前宣布,汽車零部件生產商Denso公司在改用了Cadence定制/模擬與數字流程之后,在低功耗混合信號IC設計方面實現了質量與效率的大幅提升。將Cadence Encounter RTL-to-G

2012-09-04 09:31:59 811

811 該14納米產品體系與芯片是ARM、Cadence與IBM之間在14納米及以上高級工藝節點上開發系統級芯片(SoC)多年努力的重要里程碑。使用FinFET技術以14納米標準設計的SoC能夠大幅降低功耗。 這

2012-11-16 14:35:55 1270

1270 Cadence設計系統公司日前宣布Avago Technologies在大型28納米網絡芯片設計中使用其EDI系統,大幅度加快設計進度,提高了工程效率。Avago實現1GHz的性能,比之前所用軟件設計的芯片提高57%。

2013-02-04 09:17:00 1150

1150

全球電子設計創新領先企業Cadence設計系統公司(NASDAQ:CDNS)今天宣布,歷經廣泛的基準測試后,半導體制造商聯華電子(NYSE:UMC;TWSE:2303)(UMC)已采用Cadence? “設計內”和“簽收”可制造性設計(DFM)流程對28納米設計進行物理簽收和電學變量優化。

2013-07-18 12:02:09 905

905 日前,聯華電子與SuVolta公司宣布聯合開發28納米工藝技術,該工藝將SuVolta的SuVolta的Deeply Depleted Channel晶體管技術集成到聯華電子的28納米High-K/Metal Gate高效能移動工藝。

2013-07-25 10:10:52 1049

1049 全球電子創新設計Cadence公司與上海華力微電子,15日共同宣布了華力微電子基于Cadence Encounter數字技術交付55納米平臺的參考設計流程。華力微電子首次在其已建立55納米工藝上實現了從RTL到GDSII的完整流程。

2013-08-16 11:08:11 1383

1383 全球電子設計創新領先企業Cadence設計系統公司(NASDAQ:CDNS)與上海華力微電子有限公司,今天共同宣布華力微電子基于Cadence ? Encounter? 數字技術交付出55納米平臺的參考設計流程。

2013-08-16 12:02:40 1445

1445 中芯國際新款40納米 Reference Flow5.1結合了最先進的Cadence CCOpt和GigaOpt工藝以及Tempus 時序簽收解決方案, 新款RTL-to-GDSII數字流程支持Cadence的分層低功耗流程和最新版本的通用功率格式(CPF).

2013-09-05 10:45:03 1839

1839 ? 數字工具流程,應用于其新款SMIC Reference Flow 5.1,一款為低功耗設計的完整的RTL-GDSII 數字流程。Cadence流程結合了先進功能,以幫助客戶為40納米芯片設計提高功率、性能和面積。

2013-09-05 16:50:41 748

748 9月24日——全球電子設計創新領先企業Cadence設計系統公司(NASDAQ: CDNS)今天宣布,Silicon Labs采用完整的Cadence? 混合信號低功耗設計流程,使其最新款節能型

2013-09-25 09:59:51 913

913 美國加州圣何塞,2014年9月30日 ─ 全球知名的電子設計創新領導者Cadence設計系統公司(NASDAQ: CDNS)今日宣布其豐富的IP組合與數字和定制/模擬設計工具可支持臺積電全新的超低功耗(ULP)技術平臺。

2014-10-08 19:24:35 906

906 詳細介紹Cadence的仿真流程

有需要的朋友下來看看

2015-12-08 14:49:11 0

0 2016年3月22日,中國上海——楷登電子(美國 Cadence 公司,NASDAQ: CDNS)今日宣布,用于10納米 FinFET工藝的數字、定制/模擬和簽核工具通過臺積電(TSMC)V1.0設計參考手冊(DRM)及SPICE認證。

2016-03-22 13:54:54 1026

1026 繼廣州車展正式宣布YunOS for Car品牌升級為YunOS Auto后,此次泰國發布會上,YunOS TV也正式升級亮相。12月8日,YunOS攜手Cybo在泰國曼谷召開聯合發布會。此次與Cybo的合作,意味著YunOS正式進軍海外。

2016-12-09 09:37:11 845

845 基于CCopt引擎的SMIC40nm低功耗工藝CortexA9的時鐘樹實現,該文基于 SMIC 40nm 低功耗工藝的 ARM Cortex A9 物理設計的實際情況,詳細闡述了如何使用 cadence 最新的時鐘同步優化技術,又稱為 CCopt 技術來實現統一的時鐘樹綜合和物理優化。

2017-09-28 09:08:51 7

7 臺積電業務開發副總經理金平中指出,臺積電的超低功耗平臺包括55納米超低功耗技術、40納米超低功耗技術、22納米超低功耗/超低漏電技術等,都已經被各種穿戴式產品和物聯網應用采用,同時,臺積電也把超低功耗

2017-12-11 15:03:29 1409

1409 浪潮與科大訊飛IPF2018聯合發布超強AI系統AI Booster 4月26日,在2018浪潮云數據中心合作伙伴大會(IPF2018)上,浪潮與科大訊飛聯合發布了面向于語音識別、翻譯等AI

2018-05-06 05:03:00 4967

4967 雙方聯合推出基于華潤上華110納米嵌入式閃存技術平臺的低功耗物聯網完整解決方案。

2018-08-15 08:52:50 3822

3822 Cadence Low-Power Solution是用于低功耗芯片的邏輯設計、驗證和實現的完全集成的、標準化的流程,將領先的設計、驗證和實現技術與Si2Common Power Format

2018-11-13 11:30:03 1357

1357 近日,華虹集團旗下中國領先的12英寸晶圓代工企業上海華力與全球IC設計領導廠商---聯發科技股份有限公司(以下簡稱“聯發科技”)共同宣布,在兩家公司的互相信任及持續努力下,近日雙方合作成果之一---基于上海華力28納米低功耗工藝平臺的一顆無線通訊數據處理芯片成功進入量產階段。

2018-12-12 15:15:01 2029

2029 12月11日,華虹集團旗下中國領先的12英寸晶圓代工企業上海華力與全球IC設計領導廠商---聯發科技股份有限公司(以下簡稱“聯發科技”)共同宣布,在兩家公司的互相信任及持續努力下,近日雙方合作成果之一---基于上海華力28納米低功耗工藝平臺的一顆無線通訊數據處理芯片成功進入量產階段。

2018-12-14 15:47:30 3159

3159 華虹集團旗下中國領先的12英寸晶圓代工企業上海華力與全球IC設計領導廠商---聯發科技股份有限公司(以下簡稱“聯發科技”)共同宣布,在兩家公司的互相信任及持續努力下,近日雙方合作成果之一---基于上海華力28納米低功耗工藝平臺的一顆無線通訊數據處理芯片成功進入量產階段。

2019-01-01 15:13:00 3780

3780 華虹集團旗下上海華力與聯發科技股份有限公司共同宣布,在兩家公司的互相信任及持續努力下,近日雙方合作成果之一——基于上海華力28納米低功耗工藝平臺的一顆無線通訊數據處理芯片成功進入量產階段。

2019-01-07 14:15:45 3224

3224 中國移動、中國電信、中國聯通三家運營商聯合發布了《開放參考設計理念、進展及未來演進策略》白皮書

2019-06-27 17:14:11 3991

3991 采用極紫外(EUV)光刻技術的Cadence 數字全流程解決方案已通過Samsung Foundry 5nm早期低功耗版(5LPE)工藝認證。

2019-07-11 16:36:47 3436

3436 在HUAWEI CONNECT2019期間,華為與北京中安星云軟件技術有限公司(以下簡稱“中安星云”)聯合發布了融慧智簡大數據安全解決方案,依托協議解析和大數據技術為用戶提供動態可視的安全防護能力。

2019-10-12 17:09:47 567

567 和知名服務商、企業代表共聚一堂,共同探討“未來智造發展的新模式、新平臺、新生態”和企業數字化轉型實踐。 在現場和直播平臺數萬觀眾的見證下,會長單位杭州優海信息系統有限公司與浙江藍卓工業互聯網信息技術有限公司聯合發布了基于supOS的

2021-01-14 13:49:01 1533

1533 世界移動通信大會(MWC展)在上海盛大開幕。大會同期,廣和通聯合宏電在內的眾多生態合作伙伴,隆重啟動“5G智造營·生態原力發布會”,發布會上, 宏電攜手廣和通聯合發布搭載廣和通5G模組FM650

2021-03-10 14:11:10 1052

1052 就在普京與拜登舉行會晤之際中俄聯合發布國際月球科研站路線圖;而且今天是神舟載人飛船發射成功的大好日子,我國空間站的建設加速推進正大邁步的走向世界前列。 中俄聯合發布國際月球科研站路線圖的時間是在全球

2021-06-17 12:04:40 11394

11394 安富利旗下全球電子元器件產品與解決方案分銷商e絡盟通過其在線互動社區與英飛凌聯合發起低功耗物聯網設計挑戰賽。

2021-07-19 14:54:53 1582

1582

現在電子產品一般都有要求低功耗,不同的MCU,進入低功耗的處理流程可能不一樣,但是大致的流程還是一樣。現對MCU進入低功耗的處理流程大致如下:(1)關閉MCU之外的外設電源,例如:RS485、CAN

2021-10-25 11:36:02 18

18 展銳賦能螞蟻鏈和廣和通聯合發布螞蟻鏈首批無線通信可信上鏈模組。

2021-11-19 20:29:52 1278

1278 近日,全球能源管理和自動化領域的數字化轉型專家施耐德電氣攜手CNBC Catalyst,聯合發布了名為《開啟可持續未來:數字解決方案成為可持續轉型關鍵》的報告(以下簡稱報告)。

2022-03-21 17:09:08 1394

1394 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)今日宣布,其數字和定制 / 模擬設計流程已獲得 TSMC N3E 和 N4P 工藝認證,支持最新的設計規則手冊(DRM)。

2022-06-17 17:33:05 4800

4800 8月28日,由華為云、軟通動力信息技術(集團)股份有限公司(下稱“軟通動力”)等多家合作伙伴聯合發起的首屆828 B2B企業節正式啟動。作為此次盛事的聯合發起方,軟通動力出席啟動儀式并將全程參與

2022-08-30 11:25:47 747

747 會上,云天勵飛與華為聯合發布基于昇騰AI的“AICE賦能行業解決方案”,以AI賦能城市千行百業,共筑產業生態,共創數智未來。

2022-09-05 11:03:41 647

647 電子發燒友網站提供《低功耗數字溫度計參考設計.zip》資料免費下載

2022-09-06 10:44:37 2

2 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布,Cadence 數字和定制/模擬設計流程已通過 TSMC N3E 和 N2 先進工藝的設計規則手冊(DRM)認證。兩家公司還發布

2023-05-09 10:09:23 708

708 研究院黨委書記、副院長宋靈恩,羅蘭貝格全球合伙人兼大中華區副總裁李冰聯合發布《工業數字化/智能化2030白皮書》。 白皮書憧憬了“IMAGINE”的未來工業,分析了十六大工業行業的數字化進展和二十個共性的高價值工業數字化場景,洞悉了工業裝

2023-06-01 03:10:02 363

363

中芯國際是中國大陸最大的半導體制造企業之一,主要業務是為其他半導體公司生產晶片。暫時中斷28納米芯片的生產擴大,將致力于提高12納米節點的生產能力。smic的決定是出于經濟上的原因。

2023-06-01 10:50:21 1485

1485 已經過 SF2 和 SF3 流程認證 ●? Cadence 數字全流程針對先進節點實現了最佳 PPA 結果 ● Cadence 定制/模擬工具,包括基于 AI 的 Virtuoso Studio

2023-07-05 10:10:01 322

322 已經過 SF2 和 SF3 流程認證 ●?Cadence 數字全流程針對先進節點實現了最佳 PPA 結果 ●Cadence 定制/模擬工具,包括基于 AI 的 Virtuoso Studio,已針對

2023-07-05 10:12:14 381

381 的 Cadence 流程,以十足把握交付各類 HPC 及消費電子應用 中國上海,2023 年 7 月 14 日——楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布其數字和定制/模擬

2023-07-14 12:50:02 381

381

9月20日-22日,以“加速行業智能化”為主題的華為全聯接大會2023在上海召開。作為本屆大會唯一最高級別(鉆石級)的合作伙伴,軟通動力受邀參會,并出席行業輔助運營聯合發布儀式, 與華為及伙伴聯合發布

2023-09-24 21:55:01 650

650

內容提要 Cadence 數字全流程涵蓋關鍵的新技術,包括一款高精度且支持大規模擴展的寄生參數 3D 場求解器 Cadence Cerebrus 由 AI 驅動,支持 N2 制程,可大幅提高客戶

2023-10-10 16:05:04 270

270 內容提要 1 通過利用 Cadence AI 驅動云端數字全流程,Imagination 成功將其最新 5nm 節點的漏電功耗降低 20%,將總功耗降低 6%,同時改善了面積和性能

2023-10-18 15:50:01 160

160 “基于人工智能的cadence cerebrus和更廣泛的cadence數字進程是為復雜的下一代設計而設計的,例如5納米低功耗gpu的imagination。”

2023-10-20 10:04:07 261

261 清華、阿里安全、Real_AI聯合發布最新AI安全評估平臺

2023-01-13 09:07:31 1

1 Cadence近日宣布,其數字和定制/模擬流程在Intel的18A工藝技術上成功通過認證。這一里程碑式的成就意味著Cadence的設計IP將全面支持Intel的代工廠在這一關鍵節點上的工作,并提

2024-02-27 14:02:18 160

160

電子發燒友App

電子發燒友App

評論