探討使用PROTEL設(shè)計(jì)軟件實(shí)現(xiàn)高速PCB設(shè)計(jì)的過程中,需要注意的一些布局與布線方面的相關(guān)原則問題.

2011-12-10 00:03:00 1146

1146 Allegro/OrCAD 16.6在應(yīng)對PCB設(shè)計(jì)的小型化、高速化、智能化、以及提升團(tuán)隊(duì)協(xié)同設(shè)計(jì)效率方面實(shí)現(xiàn)了長足的進(jìn)步。

2013-01-06 09:36:43 5881

5881 本文主要詳解PCB設(shè)計(jì)高速模擬輸入信號走線,首先介紹了PCB設(shè)計(jì)高速模擬輸入信號走線方法,其次闡述了九大關(guān)于PCB設(shè)計(jì)高速模擬輸入信號走線規(guī)則,具體的跟隨小編一起來了解一下。

2018-05-25 09:06:44 8394

8394

經(jīng)驗(yàn),畫過通訊、工業(yè)控制、嵌入式、數(shù)碼消費(fèi)類產(chǎn)品的高速、高密度、數(shù)模混合等PCB設(shè)計(jì)。處理高速信號很有經(jīng)驗(yàn),通過對于疊層的控制、信號的分類、拓?fù)浣Y(jié)構(gòu)的確定、微帶線帶狀線分析、阻抗的控制、時(shí)序的分析、平面

2013-03-26 14:52:54

組件在整個(gè)通道中的相互作用。 通道中的每個(gè)組件都包含一些設(shè)計(jì)變量,其會影響通道中其他組件的性能。必須考慮插入損耗、回波損耗、串?dāng)_、阻抗等連接器變量。PCB設(shè)計(jì)決策包括布局、布線、材料/層壓材料選擇

2023-04-18 14:52:28

高速PCB設(shè)計(jì)系列課:入門篇:林超文PCB設(shè)計(jì)PADS和OrCAD實(shí)操指南http://t.elecfans.com/topic/22.html?elecfans_trackid=bbspost

2015-05-05 09:30:27

對于廣大PCB設(shè)計(jì)工程師而言,提到時(shí)序問題,覺得比較茫然,看到時(shí)序圖,更是一頭霧水,感覺時(shí)序問題很高深。大家平常的設(shè)計(jì)中,最常見的是各種等長關(guān)系,網(wǎng)上流傳的Layout Guide,也會告訴大家

2014-10-21 09:35:50

高速PCB設(shè)計(jì)之一 何為高速PCB設(shè)計(jì)電子產(chǎn)品的高速化、高密化,給PCB設(shè)計(jì)工程師帶來新的挑戰(zhàn)。PCB設(shè)計(jì)不再是產(chǎn)品硬件開發(fā)的附屬,而成為產(chǎn)品硬件開發(fā)中“前端IC,后端PCB,SE集成”3個(gè)環(huán)節(jié)中

2014-10-21 09:41:25

`請問高速PCB設(shè)計(jì)前期的準(zhǔn)備工作有哪些?`

2020-04-08 16:32:20

高速PCB設(shè)計(jì)常見問題問: 高速系統(tǒng)的定義?/ 答: 高速數(shù)字信號由信號的邊沿速度決定,一般認(rèn)為上升時(shí)間小于4 倍信號傳輸延遲時(shí)可視為高速信號。而平常講的高頻信號是針對信號頻率而言的。設(shè)計(jì)開發(fā)高速

2019-01-11 10:55:05

高速PCB設(shè)計(jì)常見問題

2012-09-03 10:34:50

本帖最后由 eehome 于 2013-1-5 09:46 編輯

高速PCB設(shè)計(jì)指南。

2012-08-04 10:35:49

高速PCB設(shè)計(jì)指南

2012-04-02 22:47:12

高速PCB設(shè)計(jì)指南

2012-08-12 13:09:35

高速PCB設(shè)計(jì)指南

2013-12-07 11:48:35

高速PCB設(shè)計(jì)電容的應(yīng)用采集

2014-10-24 11:19:05

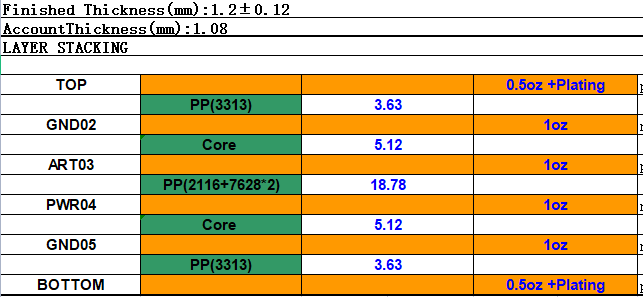

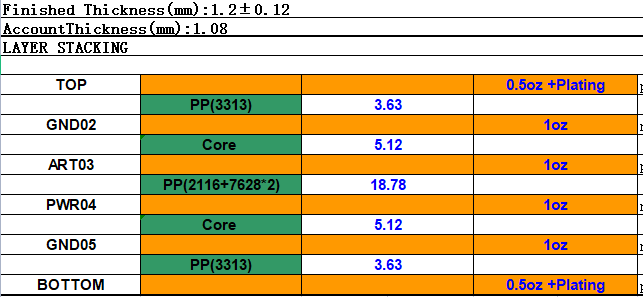

高速PCB設(shè)計(jì)的疊層問題

2009-05-16 20:51:30

本帖最后由 eehome 于 2013-1-5 09:53 編輯

高速PCB設(shè)計(jì)已成為數(shù)字系統(tǒng)設(shè)計(jì)中的主流技術(shù),PCB的設(shè)計(jì)質(zhì)量直接關(guān)系到系統(tǒng)性能的好壞乃至系統(tǒng)功能的實(shí)現(xiàn)。針對高速PCB

2012-03-31 14:29:39

`請問高速PCB設(shè)計(jì)規(guī)則有哪些?`

2020-02-25 16:07:38

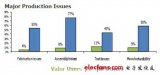

隨著信號上升沿時(shí)間的減小及信號頻率的提高,電子產(chǎn)品的EMI問題越來越受到電子工程師的關(guān)注,幾乎60%的EMI問題都可以通過高速PCB來解決。以下是九大規(guī)則: 高速PCB設(shè)計(jì)解決EMI問題的九大規(guī)則

2016-01-19 22:50:31

高速PCB設(shè)計(jì)完成后,一般都要經(jīng)過評審才會發(fā)出去做板。但是修改在EMC,貼片,信號完整性等方面有些什么修改意見嗎?

2021-03-07 06:28:29

資料主要講述射頻與數(shù)模混合高速pcb設(shè)計(jì)

2020-10-23 23:35:56

在高速pcb設(shè)計(jì)中,經(jīng)常聽到要求阻抗匹配。而設(shè)計(jì)中導(dǎo)致阻抗不匹配的原因有哪些呢?一般又對應(yīng)著怎么的解決方案?歡迎大家來討論

2014-10-24 13:50:36

高速pcb設(shè)計(jì)技術(shù)

2009-07-17 21:56:11

高速PCB設(shè)計(jì)指南之(一~八 )目錄2001/11/21CHENZHI/LEGENDSILICON一、1、PCB布線2、PCB布局3、高速PCB設(shè)計(jì)二、1、高密度(HD)電路設(shè)計(jì)2、抗干擾技術(shù)3

2012-07-13 16:18:40

高速FPGA PCB設(shè)計(jì)指南

2012-08-16 17:01:22

SerDes應(yīng)用的PCB設(shè)計(jì)要點(diǎn)– reference2:差分信號的回流路徑問題討論– video如何應(yīng)對未來高密SerDes設(shè)計(jì)的挑戰(zhàn)高速PCB layout設(shè)計(jì)應(yīng)考慮的點(diǎn):PCB mate...

2021-11-12 06:46:26

Allegro高速PCB設(shè)計(jì)技巧視頻--PCB設(shè)計(jì)必備免費(fèi)分享有問題加QQ451701569 [qq]451701569[/qq]自行下載學(xué)習(xí)鏈接: http://pan.baidu.com/s

2016-05-10 19:54:57

《Cadence Allegro實(shí)戰(zhàn)攻略與高速PCB設(shè)計(jì)》基本信息作者: 杜正闊 高寶君 何宗明 叢書名: EDA精品智匯館出版社:電子工業(yè)出版社ISBN:9787121284724上架時(shí)間

2017-08-11 17:11:31

在高速PCB設(shè)計(jì)中,過孔有哪些注意事項(xiàng)?

2021-04-25 09:55:24

圖解在高速的PCB設(shè)計(jì)中的走線規(guī)則

2021-03-17 07:53:30

高速PCB設(shè)計(jì)的基本內(nèi)容是什么高速PCB的設(shè)計(jì)方法是什么

2021-04-27 06:33:07

在高速PCB設(shè)計(jì)過程中,由于存在傳輸線效應(yīng),會導(dǎo)致一些一些信號完整性的問題,如何應(yīng)對呢?

2021-03-02 06:08:38

如何去面對高速高密度PCB設(shè)計(jì)的新挑戰(zhàn)?

2021-04-23 06:18:11

解決高速PCB設(shè)計(jì)信號問題的全新方法

2021-04-25 07:56:35

高速數(shù)字PCB設(shè)計(jì)信號完整性解決方法

2021-03-29 08:12:25

在一般的非高速PCB設(shè)計(jì)中,我們都是認(rèn)為電信號在導(dǎo)線上的傳播是不需要時(shí)間的,就是一根理想的導(dǎo)線,這種情況在低速的情況下是成立的,但是在高速的情況下,我們就不能簡單的認(rèn)為其是一根理想的導(dǎo)線了,電信號

2019-05-30 06:59:24

布線技術(shù)實(shí)現(xiàn)信號串?dāng)_控制的設(shè)計(jì)策略EMC的PCB設(shè)計(jì)技術(shù)CADENCE PCB設(shè)計(jì)技術(shù)方案基于高速FPGA的PCB設(shè)計(jì)技術(shù)解析高速PCB設(shè)計(jì)中的時(shí)序分析及仿真策略闡述基于Proteus軟件的單片機(jī)仿真

2014-12-16 13:55:37

電容在高速PCB設(shè)計(jì)的應(yīng)用

2012-08-14 11:40:20

什么是高速pcb設(shè)計(jì)高速線總體規(guī)則是什么?

2019-06-13 02:32:06

高頻高速PCB設(shè)計(jì)之實(shí)用大全(2).pdf(128.59 KB)

2019-09-16 08:54:58

高速PCB設(shè)計(jì)指南之(一~八 )目錄 2001/11/21 一、1、PCB布線2、PCB布局3、高速PCB設(shè)計(jì)

二、1、高密度(HD)電路設(shè)計(jì)2、抗干擾技術(shù)

2008-08-04 14:14:42 0

0 高速PCB設(shè)計(jì)的疊層問題

2009-05-16 20:06:45 0

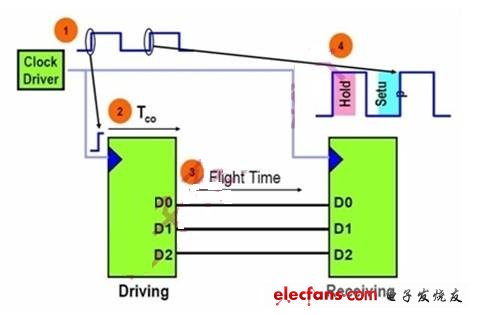

0 Cadence高速PCB的時(shí)序分析:列位看觀,在上一次的連載中,我們介紹了什么是時(shí)序電路,時(shí)序分析的兩種分類(同步和異步),并講述了一些關(guān)于SDRAM 的基本概念。這一次的連載中,

2009-07-01 17:23:27 0

0 電容在高速PCB設(shè)計(jì)中的應(yīng)用:探討高速PCB設(shè)計(jì)電容的應(yīng)用。電容是電路板上不可缺少的一個(gè)部分,并且起到了至關(guān)重要的作用,探討他具備至關(guān)重要的價(jià)值。您在設(shè)計(jì)中是否有這樣

2009-08-16 13:11:56 0

0 PCB設(shè)計(jì)基礎(chǔ)教程

此教程包括:

高速PCB設(shè)計(jì)指南之一 高速PCB設(shè)計(jì)指南之二 PCB Layout指南(上) PCB Layout指南(下) PCB設(shè)計(jì)的一般原則 PCB設(shè)計(jì)基礎(chǔ)知識 PCB設(shè)計(jì)

2010-03-15 14:22:26 0

0 Cadence 高速 PCB 的時(shí)序分析 1.引言 時(shí)序分析,也許是 SI 分析中難度最大的一部分。我懷著滿腔的期許給 Cadence 的資深工程師發(fā)了一封 e-mail,希望能夠得到一份時(shí)序分析的案

2010-04-05 06:37:13 0

0 高速PCB設(shè)計(jì)指南之一

第一篇 PCB布線在PCB設(shè)計(jì)中,布線是完成產(chǎn)品設(shè)計(jì)的重要步驟,可以說前面的準(zhǔn)備工作都是為它而做

2009-11-11 14:57:48 600

600 高速PCB設(shè)計(jì)指南之五

第一篇 DSP系統(tǒng)的降噪技術(shù)

隨著高速DSP(數(shù)字信號處理器)和外

2009-11-11 15:05:39 550

550 高速PCB設(shè)計(jì)指南之六

第一篇 混合信號電路板的設(shè)計(jì)準(zhǔn)則

模擬電路的工作依賴連續(xù)變化的

2009-11-11 15:06:25 463

463 高速PCB設(shè)計(jì)指南之七

第一篇 PCB基本概念

1、“層(Layer) ”的概念 與字處理或其它許多

2009-11-11 15:07:15 433

433 高速PCB抄板與PCB設(shè)計(jì)方案

目前高速PCB的設(shè)計(jì)在通信、計(jì)算機(jī)、圖形圖像處理等領(lǐng)域應(yīng)用廣泛。而在這些領(lǐng)域工程師們用的高速PCB

2009-11-18 14:11:47 824

824 基于Cadence的高速PCB設(shè)計(jì)

隨著人們對通信需求的不斷提高,要求信號的傳輸和處理的速度越來越快.相應(yīng)的高速PCB的應(yīng)用也越來越廣,設(shè)計(jì)也越來越

2009-12-12 17:50:27 954

954 高速PCB 設(shè)計(jì)已成為數(shù)字系統(tǒng)設(shè)計(jì)中的主流技術(shù),PCB的設(shè)計(jì)質(zhì)量直接關(guān)系到系統(tǒng)性能的好壞乃至系統(tǒng)功能的實(shí)現(xiàn)。針對高速PCB的設(shè)計(jì)要求,結(jié)合筆者設(shè)計(jì)經(jīng)驗(yàn),按照PCB設(shè)計(jì)流程,對PCB設(shè)計(jì)

2011-08-30 15:44:23 0

0 簡要闡述了高速PCB設(shè)計(jì)的主要內(nèi)容, 并結(jié)合Cadence軟件介紹其解決方案比較了傳統(tǒng)高速設(shè)計(jì)方法與以Cadence為代表的現(xiàn)代高速PCB設(shè)計(jì)方法的主要差異指出在進(jìn)行高速設(shè)計(jì)過程中必須借助于

2011-11-21 16:53:58 0

0 理論研究和實(shí)踐都表明,對高速電子系統(tǒng)而言,成功的PCB設(shè)計(jì)是解決系統(tǒng)EMC問題的重要措施之一.為了滿足EMC標(biāo)準(zhǔn)的要求,高速PCB設(shè)計(jì)正面臨新的挑戰(zhàn),在高速PCB設(shè)計(jì)中,設(shè)計(jì)者需要糾正或放棄

2011-11-23 10:25:41 0

0 高速PCB設(shè)計(jì)技術(shù)(中文)

2011-12-02 14:16:44 161

161 在北京舉行的Mentor 2012中國PCB設(shè)計(jì)技術(shù)研討會上,該公司業(yè)務(wù)開發(fā)經(jīng)理David Wiens分析闡述了高速PCB設(shè)計(jì)的6個(gè)關(guān)鍵要素:流程并行化、虛擬原型設(shè)計(jì)、DFM、復(fù)雜度管理、協(xié)同和IP管理。

2012-07-02 11:30:15 903

903

高速PCB設(shè)計(jì)指南,大家自己有需要的趕緊下載吧,機(jī)不可失

2015-10-27 14:09:28 0

0 高速電路PCB設(shè)計(jì)技巧分享,好東西,喜歡的朋友可以下載來學(xué)習(xí)。

2016-01-18 15:41:19 0

0 高速電路PCB設(shè)計(jì)實(shí)踐,好東西,喜歡的朋友可以下載來學(xué)習(xí)。

2016-01-18 15:41:19 0

0 高速PCB設(shè)計(jì)指南.........................

2016-05-09 15:22:31 0

0 高速PCB設(shè)計(jì)指南............................

2016-05-09 15:22:31 0

0 高速PCB設(shè)計(jì)指南.......................

2016-05-09 15:22:31 0

0 高速PCB設(shè)計(jì)指南,可以做參考

2016-12-16 22:07:10 0

0 高速PCB設(shè)計(jì)電容的應(yīng)用,很有參考意義

2016-12-16 22:07:10 0

0 高速PCB設(shè)計(jì)指南,好資料,又需要的下來看看

2017-01-12 12:18:20 0

0 高速PCB設(shè)計(jì)電容的應(yīng)用

2017-01-28 21:32:49 0

0 高速PCB設(shè)計(jì)之DSP系統(tǒng)的降噪技術(shù)

2017-08-28 08:53:38 9

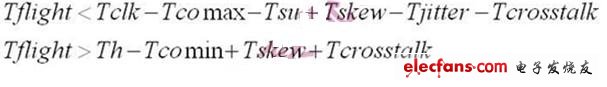

9 本文檔的主要內(nèi)容詳細(xì)介紹的是PCB設(shè)計(jì)有哪些誤區(qū)PCB設(shè)計(jì)的十大誤區(qū)下部分主要內(nèi)容包括了:1.時(shí)序及等長設(shè)計(jì)概述,2.共同時(shí)鐘并行總線時(shí)序設(shè)計(jì),3.源同步時(shí)鐘并行總線時(shí)序設(shè)計(jì),4.高速串行總線時(shí)序設(shè)計(jì),5.時(shí)序及等長設(shè)計(jì)總結(jié)

2019-01-07 08:00:00 0

0 高速PCB設(shè)計(jì)EMI有什么規(guī)則

2019-08-21 14:38:03 807

807

在高速PCB設(shè)計(jì)中推薦使用多層電路板。

2019-08-22 10:34:35 7705

7705 本文主要分析一下在高速PCB設(shè)計(jì)中,高速信號與高速PCB設(shè)計(jì)存在一些理解誤區(qū)。 誤區(qū)一:GHz速率以上的信號才算高速信號? 提到高速信號,就需要先明確什么是高速,MHz速率級別的信號算高速、還是

2019-11-05 11:27:17 10310

10310

高速PCB設(shè)計(jì)是指信號的完整性開始受到PCB物理特性(例如布局,封裝,互連以及層堆疊等)影響的任何設(shè)計(jì)。而且,當(dāng)您開始設(shè)計(jì)電路板并遇到諸如延遲,串?dāng)_,反射或發(fā)射之類的麻煩時(shí),您將進(jìn)入高速PCB設(shè)計(jì)領(lǐng)域。

2020-06-19 09:17:09 1537

1537 在高速PCB設(shè)計(jì)的學(xué)習(xí)中,有很多的知識點(diǎn)需要大家去了解和掌握,比如常見的信號完整性、反射、串?dāng)_、電源噪聲、濾波等。本文就和大家分享10個(gè)和高速PCB設(shè)計(jì)相關(guān)的重要知識,希望對大家的學(xué)習(xí)有所幫助。

2020-10-23 14:20:58 2739

2739

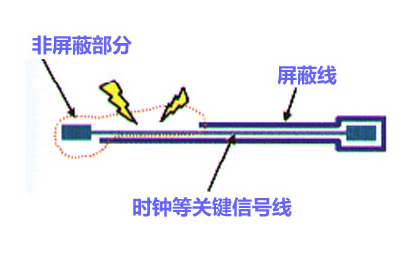

在高速PCB設(shè)計(jì)中,差分信號的應(yīng)用越來越廣泛,這主要是因?yàn)楹推胀ǖ膯味诵盘栕呔€相比,差分信號具有抗干擾能力強(qiáng)、能有效抑制EMI、時(shí)序定位精確的優(yōu)勢。

2021-03-23 14:40:47 2760

2760 電子發(fā)燒友網(wǎng)為你提供高速PCB設(shè)計(jì)傳輸線效應(yīng)問題四點(diǎn)應(yīng)對資料下載的電子資料下載,更有其他相關(guān)的電路圖、源代碼、課件教程、中文資料、英文資料、參考設(shè)計(jì)、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-04 08:53:59 12

12 SerDes應(yīng)用的PCB設(shè)計(jì)要點(diǎn)– reference2:差分信號的回流路徑問題討論– video如何應(yīng)對未來高密SerDes設(shè)計(jì)的挑戰(zhàn)高速PCB layout設(shè)計(jì)應(yīng)考慮的點(diǎn):PCB mate...

2021-11-07 10:21:00 47

47 如今,隨著電子元件飛速的發(fā)展,各類電子設(shè)備和計(jì)算機(jī)的運(yùn)行速度,也越來越快。高速電路在電子設(shè)備的應(yīng)用也愈加廣泛,人們也越來越離不開這些電子產(chǎn)品。不管啥電子產(chǎn)品都需要和PCB設(shè)計(jì)掛鉤,市場巨大,學(xué)會高速

2022-01-27 13:59:58 3097

3097 多層板與高速PCB設(shè)計(jì)

2022-12-30 09:21:23 6

6 射頻與數(shù)模混合類高速PCB設(shè)計(jì)

2022-12-30 09:21:27 3

3 高速PCB設(shè)計(jì)培訓(xùn)教材

2022-12-30 09:22:12 15

15 高速PCB設(shè)計(jì)技術(shù)(中文)

2022-12-30 09:22:12 9

9 高速PCB設(shè)計(jì)指南之一

2022-12-30 09:22:13 6

6 高速PCB設(shè)計(jì)指南之七

2022-12-30 09:22:13 4

4 高速PCB設(shè)計(jì)指南之三

2022-12-30 09:22:13 3

3 高速PCB設(shè)計(jì)指南之五

2022-12-30 09:22:14 3

3 高速PCB設(shè)計(jì)指南之八

2022-12-30 09:22:14 5

5 高速PCB設(shè)計(jì)指南之六

2022-12-30 09:22:15 3

3 高速PCB設(shè)計(jì)指南之四

2022-12-30 09:22:15 4

4 高速PCB設(shè)計(jì)指南二

2022-12-30 09:22:16 5

5 高速PCB設(shè)計(jì)電容的應(yīng)用

2022-12-30 09:22:16 29

29 高速PCB設(shè)計(jì)的疊層問題

2022-12-30 09:22:17 37

37 高速PCB設(shè)計(jì)電容的應(yīng)用

2023-03-01 15:37:57 2

2 高速PCB設(shè)計(jì)當(dāng)中鋪銅處理方法

2023-11-24 18:03:58 263

263

PCB設(shè)計(jì)之高速電路

2023-12-05 14:26:22 290

290

電子發(fā)燒友App

電子發(fā)燒友App

評論