電磁干擾的PCB設(shè)計方法

電磁干擾(Electromagnetic InteRFerence),簡稱EMI,有傳導(dǎo)干擾和輻射干擾兩種。傳導(dǎo)干擾主要是電子設(shè)

2009-04-07 22:13:01 843

843 所謂干擾,必然是發(fā)生在不同的單元電路、部件或系統(tǒng)之間,而地線干擾是指通過公用地線的方式產(chǎn)生的信號干擾。注意這里所提到的信號,通常是指交流信號或者跳變信號。地線

2012-03-21 11:50:07 6045

6045

電源、地線的處理既使在整個PCB板中的布線完成得都很好,但由于電源、 地線的考慮不周到而引起的干擾, 會使產(chǎn)品的性能下降,有時甚至影響到產(chǎn)品的成功率.所以對電、 地線的布線要認(rèn)真對 待,把電、地線所

2018-08-21 21:49:05

本帖最后由 gk320830 于 2015-3-7 13:54 編輯

PCB布線中的地線干擾分析與抑制方法 1.地線的定義 什么是地線?大家在教科書上學(xué)的地線定義是:地線是作為電路電位基準(zhǔn)點

2013-10-11 10:58:18

是由電纜與地線構(gòu)成的環(huán)路電流產(chǎn)生的,因此成為地環(huán)路干擾。地環(huán)路中的電流還可以由外界電磁場感應(yīng)出來。 3.2公共阻抗干擾 當(dāng)兩個電路共用一段地線時,由于地線的阻抗,一個電路的地電位會受另一個電路工作

2018-09-13 15:58:38

干擾是由電纜與地線構(gòu)成的環(huán)路電流產(chǎn)生的,因此成為地環(huán)路干擾。地環(huán)路中的電流還可以由外界電磁場感應(yīng)出來。 3.2公共阻抗干擾 當(dāng)兩個電路共用一段地線時,由于地線的阻抗,一個電路的地電位會受另一個電路

2018-09-04 16:31:28

的電流還可以由外界電磁場感應(yīng)出來。3.2公共阻抗干擾當(dāng)兩個電路共用一段地線時,由于地線的阻抗,一個電路的地電位會受另一個電路工作電流的調(diào)制。這樣一個電路中的信號會耦合進(jìn)另一個電路,這種耦合稱為公共阻抗

2012-02-20 14:20:42

PCB布線的地線干擾與抑制處理方法

2015-08-18 10:22:30

可能相差很大。正是這些電位差才造成了電路工作的異常。電路是一個等電位體的定義僅是人們對地線電位的期望。HENRY給地線了一個更加符合實際的定義,他將地線定義為:信號流回源的低阻抗路徑。這個定義中突出

2023-09-20 06:34:50

設(shè)備達(dá)到電磁兼容標(biāo)準(zhǔn)最有效、成本最低的手段。本文介紹數(shù)字電路PCB設(shè)計中的EMI控制技術(shù)。1 EMI的產(chǎn)生及抑制原理EMI的產(chǎn)生是由于電磁干擾源通過耦合路徑將能量傳遞給敏感系統(tǒng)造成的。它包括經(jīng)由導(dǎo)線或

2019-04-27 06:30:00

共阻干擾是由PCB上大量的地線造成。當(dāng)兩個或兩個以上的回路共用一段地線時,不同的回路電流在共用地線上產(chǎn)生一定壓降,此壓降經(jīng)放大就會影響電路性能;當(dāng)電流頻率很高時,會產(chǎn)生很大的感抗而使電路受到干擾

2018-11-26 11:06:15

靠近整流二極管放置。 3)電源與地的布線原則 PCB的電源與地的布線是否合理是整個電路板減小電磁干擾的關(guān)鍵所在。電源線和地線的設(shè)計是PCB中不可忽視的問題,往往也是難度最大的一項設(shè)計,設(shè)計時應(yīng)遵循

2018-09-21 11:51:38

有較多的磁通量,因而在電路中感應(yīng)出較強的電流。因此,必須減少環(huán)路面積。最常見的環(huán)路如圖1 所示,由電源和地線所形成。在可能的條件下,可以采用具有電源及接地層的多層PCB設(shè)計。多層電路板不僅將電源和接地間

2012-02-03 14:09:10

的延遲,在傳輸線的終端形成反射噪聲。 在設(shè)計PCB的時候應(yīng)該注意采用正確的方法: 1、地線的合理設(shè)計。 在電子設(shè)計中,接地是控制干擾的重要方法。如果能將接地和屏蔽正確的結(jié)合起來用,可以解決大部分

2023-04-10 16:03:54

PCB設(shè)計中的電磁干擾問題PCB的干擾抑制步驟

2021-04-25 06:51:58

高頻電路中,千萬不要認(rèn)為,把地線的某個地方接了地,這就是“地線”,一定要以小于λ/20的間距,在布線上打過孔,與多層板的地平面“良好接地”。如果把覆銅處理恰當(dāng)了,覆銅不僅具有加大電流,還起了屏蔽干擾

2016-09-06 13:03:13

電子設(shè)備的靈敏度越來越高,這要求設(shè)備的抗干擾能力也越來越強,因此PCB設(shè)計也變得更加困難,如何提高PCB的抗干擾能力成為眾多工程師們關(guān)注的重點問題之一。本文將介紹PCB設(shè)計中降低噪聲與電磁干擾的一

2018-09-18 15:40:54

電子設(shè)備的靈敏度越來越高,這要求設(shè)備的抗干擾能力也越來越強,因此PCB設(shè)計也變得更加困難,如何提高PCB的抗干擾能力成為眾多工程師們關(guān)注的重點問題之一。ADI中文技術(shù)支持論壇上網(wǎng)友分享的《PCB設(shè)計

2019-05-31 06:39:14

;為了抑制出現(xiàn)在印制導(dǎo)線終端的反射干擾,可在傳輸線的末端對地和電源端各加接一個相同阻值的匹配電阻。 (2)采用屏蔽措施 可設(shè)置大面積的屏蔽地線和專用屏蔽線以屏蔽弱信號不受干擾。 (3)去耦電容的配置

2018-08-31 11:09:59

印制電路板(PCB)是電子產(chǎn)品中電路元件和器件的支撐件.它提供電路元件和器件之間的電氣連接。隨著電于技術(shù)的飛速發(fā)展,PGB的密度越來越高。PCB設(shè)計的好壞對抗干擾能力影響很大.因此,在進(jìn)行PCB設(shè)計

2018-09-14 16:22:33

本帖最后由 gk320830 于 2015-3-7 09:05 編輯

PCB設(shè)計原則和抗干擾措施印制電路板(PCB)是電子產(chǎn)品中電路元件和器件的支撐件.它提供電路元件和器件之間的電氣連接。隨著

2013-10-23 11:09:50

本帖最后由 gk320830 于 2015-3-7 15:28 編輯

PCB設(shè)計原則和抗干擾措施印制電路板(PCB)是電子產(chǎn)品中電路元件和器件的支撐件.它提供電路元件和器件之間的電氣連接。隨著

2013-09-25 10:23:46

印制電路板(PCB)是電子產(chǎn)品中電路元件和器件的支撐件.它提供電路元件和器件之間的電氣連接。隨著電于技術(shù)的飛速發(fā)展,PGB的密度越來越高。PCB設(shè)計的好壞對抗干擾能力影響很大.因此,在進(jìn)行

2018-09-10 16:56:41

印制電路板(PCB)是電子產(chǎn)品中電路元件和器件的支撐件.它提供電路元件和器件之間的電氣連接。隨著電于技術(shù)的飛速發(fā)展,PGB的密度越來越高。PCB設(shè)計的好壞對抗干擾能力影響很大.因此,在進(jìn)行

2018-08-31 11:53:51

PCB設(shè)計中,接地是抑制噪聲和防止干擾的重要措施。根據(jù)電路的不同,有不同的接地方法,只有正確的接地才能減少或避免電路間的相互干擾。日常中主要的接地方式有兩種:單點接地和多點接地。如何在考慮EMC

2018-09-10 16:37:22

pcb 地線的干擾和抑制

2011-10-13 20:14:47

地線干擾與抑制 1.地線的定義 什么是地線?大家在教科書上學(xué)的地線定義是:地線是作為電路電位基準(zhǔn)點的等電位體。這個定義是不符合

2009-08-23 19:53:47

地線干擾與抑制1.地線的定義 什么是地線?大家在教科書上學(xué)的地線定義是:地線是作為電路電位基準(zhǔn)點的等電位體。這個定義是不符合實際情況的。實際地線上的電位并不是恒定的。如果用儀表測量一下地線上各點

2013-09-03 11:47:51

式中可以看出,當(dāng)兩根導(dǎo)線相距較遠(yuǎn)時,它們之間的互感很小,總電感相當(dāng)于單根導(dǎo)線電感的一半。因此我們可以通過多條接地線來減小接地阻抗。但要注意的是,多根導(dǎo)線之間的距離不能過近。3.地線干擾機(jī)理 3.1

2018-12-19 09:13:51

的互感。 從式中可以看出,當(dāng)兩根導(dǎo)線相距較遠(yuǎn)時,它們之間的互感很小,總電感相當(dāng)于單根導(dǎo)線電感的一半。因此我們可以通過多條接地線來減小接地阻抗。但要注意的是,多根導(dǎo)線之間的距離不能過近。 3.地線干擾

2018-11-26 16:54:02

前幾篇咱們說了FPGA內(nèi)部邏輯,本篇咱們再聊一聊7系列FPGA的供電部分。首先咱們說spartan7系列,通常咱們需要使用以下電源軌:1,VCCINTFPGA內(nèi)部核心電壓。其不損壞FPGA器件的范圍

2021-11-11 09:27:56

前言:物聯(lián)網(wǎng)的大部分設(shè)備都是電池供電的,設(shè)備本身低功耗對延長設(shè)備使用至關(guān)重要,今天就實際調(diào)試總結(jié)聊一聊stm32的低功耗調(diào)試。1、stm32在運行狀態(tài)下的功耗上圖截圖自stm32l15x手冊

2021-08-11 08:18:54

1、聊一聊串口常用的幾種方式查詢方式可靠性很高,要考慮下個數(shù)據(jù)包覆蓋上一個數(shù)據(jù)包的問題,小數(shù)據(jù)量,在10個字節(jié)以內(nèi),可以這樣考慮, 很簡單,很方便,很可靠。但是在數(shù)據(jù)量大的時候,程序阻塞的時間特別長

2022-07-21 15:17:09

這期來點輕松的,聊一聊你知道的和不知道的電流鏡。電流源可算是模擬集成電路中最基礎(chǔ)的內(nèi)容,也是有很多花樣的基本單元。電流源是籠統(tǒng)的叫法,具體會根據(jù)電流的流向,分別叫做電流源(Current

2021-06-24 06:56:35

前言今天聊一聊代碼,只有直立功能的代碼。代碼總體思路給定一個目標(biāo)值,單片機(jī)通過IIC和mpu6050通信,得知數(shù)據(jù)后,根據(jù)角度環(huán)計算出一個PWM值給電機(jī)驅(qū)動器,從而控制單機(jī)轉(zhuǎn)動。電機(jī)轉(zhuǎn)動,編碼器就會

2022-01-14 08:29:09

對于咱們電源工程師來講,我們很多時候都在看波形,看輸入波形,MOS開關(guān)波形,電流波形,輸出二極管波形,芯片波形,MOS管的GS波形,我們拿開關(guān)GS波形為例來聊一下GS的波形。我們測試MOS管GS波形

2021-11-16 09:15:19

聊下阻抗匹配,電路加一個阻抗匹配網(wǎng)絡(luò),搞成和負(fù)載一樣的阻抗,這樣豈不是多了一個假負(fù)載?不是損耗了效率嗎?而事實上剛好相反,哪個壇友分析下緣故

2018-10-31 17:55:14

Linux 下用UDP實現(xiàn)群聊單聊,能夠?qū)崿F(xiàn)單聊和群聊。程序不長,可以作為學(xué)習(xí)網(wǎng)絡(luò)的檢測。

2013-07-19 23:37:52

,因而元器件的布局影響到焊點的質(zhì)量,進(jìn)而影響到產(chǎn)品的成品率。而對于射頻電路PCB設(shè)計而言,電磁兼容性要求每個電路模塊盡量不產(chǎn)生電磁輻射,并且具有一定的抗電磁干擾能力,因此,元器件的布局還直接影響到電路本身

2010-02-03 11:55:43

感謝論壇本次的書籍試讀活動,有幸拜讀《PADS PCB設(shè)計指南》,和管理員溝通后,很快書籍就從出版社直發(fā)了。本人有一定的PADS的使用經(jīng)驗,不過有關(guān)PADS主要工作是原理圖的繪制,對于PCB的繪制

2023-05-15 15:56:19

既使在整個PCB板中的布線完成得都很好,但由于電源、 地線的考慮不周到而引起的干擾,會使產(chǎn)品的性能下降,有時甚至影響到產(chǎn)品的成功率。所以對電、 地線的布線要認(rèn)真對待,把電、地線所產(chǎn)生的噪音干擾降到

2016-12-07 22:25:19

的異常。地線干擾機(jī)理,公共阻抗干擾當(dāng)兩個電路共用一段地線時,由于地線的阻抗,一個電路的地電位會受另一個電路工作電流的調(diào)制。這樣一個電路中的信號會耦合進(jìn)另一個電路,這種耦合稱為公共阻抗耦合。在數(shù)字電路中

2018-12-03 22:18:58

電子設(shè)備的靈敏度越來越高,這要求設(shè)備的抗干擾能力也越來越強,因此PCB設(shè)計也變得更加困難,如何提高PCB的抗干擾能力成為眾多工程師們關(guān)注的重點問題之一。本文將介紹PCB設(shè)計中降低噪聲與電磁干擾的一

2018-03-10 21:32:11

的設(shè)計效果。布線的基本規(guī)則PCB設(shè)計的好壞對其抗干擾能力影響很大。因此,在PCB設(shè)計時,必須遵守設(shè)計的基本原則,并應(yīng)符合抗干擾設(shè)計的要求,使得電路獲得最佳得性能。印制導(dǎo)線得布設(shè)應(yīng)盡可能短;統(tǒng)一元器件得

2018-12-07 22:50:21

有較多的磁通量,因而在電路中感應(yīng)出較強的電流。因此,必須減少環(huán)路面積。最常見的環(huán)路如圖1 所示,由電源和地線所形成。在可能的條件下,可以采用具有電源及接地層的多層PCB設(shè)計。多層電路板不僅將電源和接地間

2015-02-03 14:27:03

高頻設(shè)計是否束手無策? 。。。。 YES? ——>還需要多多學(xué)習(xí)哦,或者你也可以來搶個沙發(fā),來和其他小伙伴聊一聊PCB設(shè)計過程中的壁壘、糗事。or 向我們的專家simon請教

2014-09-22 09:39:41

共用一段地線,就可能出現(xiàn)公共阻抗耦合的問題 4.地線干擾對策 4.1地環(huán)路對策 從地環(huán)路干擾的機(jī)理可知,只要減小地環(huán)路中的電流就能減小地環(huán)路干擾。如果能徹底消除地環(huán)路中的電流,則可以徹底解決地環(huán)路

2018-01-19 10:00:00

什么是地線?地線的阻抗是什么?地線干擾機(jī)理有哪些?應(yīng)對地線干擾的對策有哪些?

2021-04-20 06:05:35

。對于8Gbps及以上的高速應(yīng)用更應(yīng)該注意避免此類問題,為高速數(shù)字傳輸鏈路提供更多裕量。本文針對PCB設(shè)計中由小間距QFN封裝引入串?dāng)_的抑制方法進(jìn)行了仿真分析,為此類設(shè)計提供參考。那么,什么是小間距QFN封裝PCB設(shè)計串?dāng)_抑制呢?

2019-07-30 08:03:48

最好的設(shè)計效果。布線的基本規(guī)則PCB設(shè)計的好壞對其抗干擾能力影響很大。因此,在PCB設(shè)計時,必須遵守設(shè)計的基本原則,并應(yīng)符合抗干擾設(shè)計的要求,使得電路獲得最佳得性能。印制導(dǎo)線得布設(shè)應(yīng)盡可能短;統(tǒng)一

2018-11-23 16:07:58

在設(shè)計PCB的時候如何抑制反射干擾? 為了抑制出現(xiàn)在印制線條終端的反射干擾,除了特殊的需要之外,應(yīng)該盡可能的縮短印制線的長度以及采用慢速電路。 在必要的時候開業(yè)增加終端匹配,即是在傳輸線

2023-04-10 15:09:04

如何抑制電磁干擾PCB是産生電磁干擾(EMI)的源頭,所以PCB設(shè)計直接關(guān)系到電子産品的電磁兼容性(EMC)。 如果在高速PCB設(shè)計中對EMC/EMI予以重視,將有助縮短産品研發(fā)周期加快産品上市

2013-03-13 11:35:03

PCB是産生電磁干擾(EMI)的源頭,所以PCB設(shè)計直接關(guān)系到電子産品的電磁兼容性(EMC)。 如果在高速PCB設(shè)計中對EMC/EMI予以重視,將有助縮短産品研發(fā)周期加快産品上市時間。 EMC

2013-01-22 09:52:31

如何防止和抑制電磁干擾,提高PCB的電磁兼容性 ?PCB設(shè)計流程是怎樣的?如何進(jìn)行PCB布線 ?

2021-04-21 07:14:56

元器件上,且應(yīng)盡量遠(yuǎn)離不相連的元器件,以免在生產(chǎn)中出現(xiàn)虛焊、連焊、短路等現(xiàn)象。 在射頻電路PCB設(shè)計中,電源線和地線的正確布線顯得尤其重要,合理的設(shè)計是克服電磁干擾的最重要的手段。PCB上相當(dāng)多的干擾

2018-11-23 17:01:55

正常工作,因此,如何防止和抑制電磁干擾,提高電磁兼容性,就成為設(shè)計射頻電路PCB時的一個非常重要的課題。同一電路,不同的PCB設(shè)計結(jié)構(gòu),其性能指標(biāo)會相差很大。本人采用Protel99 SE軟件進(jìn)行掌上

2012-09-16 22:03:25

。 數(shù)字電路與模擬電路應(yīng)以地線隔離,數(shù)字地線與模擬地線都要分離,最后接電源地。 減少電磁干擾是PCB板設(shè)計重要的一環(huán),只要在設(shè)計時多往這一邊想自然在產(chǎn)品測驗如EMC測驗中便會更易合格。

2018-09-18 15:33:03

Fill會造成短路,為什么還用它呢?來聊一聊Altium中Fill,Polygon Pour,Plane的區(qū)別和用法

2021-04-25 06:29:06

(EMI)四個方面。電源噪聲的干擾,對高頻pcb設(shè)計影響甚遠(yuǎn)。電源噪聲:在高頻電路中,電源信號中含有的噪聲對高頻信號影響最大,一切電子信號的都是電平的高低起降來傳導(dǎo)的。如有次捷配電源被高噪聲所疊加

2018-09-13 14:59:30

解決方案詳解基于電磁兼容技術(shù)PCB板的設(shè)計解密PROTEL DXP軟件的PCB設(shè)計技巧簡述高速PCB設(shè)計中的常見問題及解決方法簡單介紹基于射頻開關(guān)模塊功能電路PCB板的設(shè)計PCB地線的干擾與抑制設(shè)計方法

2014-12-16 13:55:37

地掌握它,還需廣大電子工程設(shè)計人員去自已體會, 才能得到其中的真諦。 電源、地線的處理 既使在整個PCB板中的布線完成得都很好,但由于電源、 地線的考慮不周到而引起的干擾,會使產(chǎn)品的性能下降,有時甚至

2017-06-02 17:06:03

干擾是由電纜與地線構(gòu)成的環(huán)路電流產(chǎn)生的,因此成為地環(huán)路干擾。地環(huán)路中的電流還可以由外界電磁場感應(yīng)出來。3.2公共阻抗干擾當(dāng)兩個電路共用一段地線時,由于地線的阻抗,一個電路的地電位會受另一個電路工作電流

2015-01-14 13:58:40

電子工程設(shè)計人員去自已體會, 才能得到其中的真諦。一、電源、地線的處理 既使在整個 PCB板中的布線完成得都很好,但由于電源、 地線的考慮不周到而引起的干擾,會使產(chǎn)品的性能下降,有時甚至影響到產(chǎn)品

2018-08-24 17:07:54

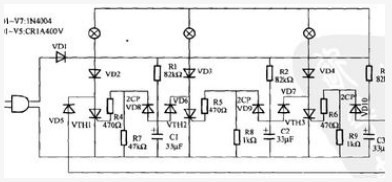

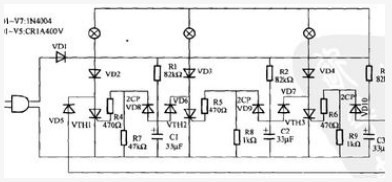

PCB板布局時的電源干擾與抑制:PCB板布局時的電源干擾與抑制內(nèi)容有穩(wěn)壓電源的原理與電流流向,穩(wěn)壓電源的干擾抑制與布局,電源線的布局等內(nèi)容。

2009-09-30 12:27:32 0

0 地線干擾與抑制1.地線的定義什么是地線?大家在教科書上學(xué)的地線定義是:地線是作為電路電位基準(zhǔn)點的等電位體。這個定義是不符合實際情況的。實際地線上

2010-06-07 16:02:10 97

97 本文簡要介紹了稱重儀表地線阻抗隨頻率升高而增大的特性,分析了地線環(huán)路及公共阻抗干擾機(jī)理及其解決方法。關(guān)鍵詞 地

2010-10-03 13:59:02 47

47 1.地線的定義什么是地線?大家在教科書上學(xué)的地線定義是:地線是作為電路電位基準(zhǔn)點的等電位體。這個定義是不符合實際情況的。實際地線上的電位并不是恒定的。如果用儀

2006-09-25 14:31:29 934

934 PCB設(shè)計考慮EMC的接地技巧

PCB設(shè)計中,接地是抑制噪聲和防止干擾的重要措施。根據(jù)電路的不同,有不同的接地方法,只有正確

2009-11-17 09:10:49 1326

1326 機(jī)房地線引起的干擾分析及其抑制方法

我站機(jī)房由微波機(jī)房和發(fā)射機(jī)房組成。發(fā)射機(jī)所用音視頻信號均由微波機(jī)房經(jīng)電纜傳輸過來,電纜長度約40多

2010-10-03 15:21:04 950

950 在PCB設(shè)計中,尤其是在高頻電路中,經(jīng)常會遇到由于地線干擾而引起的一些不規(guī)律、不正常的現(xiàn)象。本文對地線產(chǎn)生干擾的原因進(jìn)行分析,詳細(xì)介紹了地線產(chǎn)生干擾的三種類型,并根據(jù)

2011-04-28 15:00:11 0

0 PCB設(shè)計中地線干擾抑制方法詳解,感興趣的小伙伴們可以看看。

2016-07-26 16:29:36 0

0 圖解PCB地線干擾及抑制對策,感興趣的小伙伴們可以看看。

2016-07-29 17:46:24 0

0 地線干擾與抑制

2017-01-28 21:32:49 0

0 PCB 地線干擾的共阻干擾

2017-04-06 11:06:10 0

0 電子電路中,共阻抗干擾對電路的正常工作帶來很大影響。在PCB電路設(shè)計中,尤其在高頻電路的PCB設(shè)計中,必須防止地線的共阻抗所帶來的影響。通過對共阻抗干擾形式的分析,詳細(xì)介紹一點接地在電子電路

2017-11-28 09:58:52 0

0 瞬態(tài)干擾對PCB的正常工作構(gòu)成了嚴(yán)重的威脅,其抑制問題已經(jīng)得到越來越多PCB設(shè)計者的重視。文章對 PCB所受到的瞬態(tài)干擾及其危害進(jìn)行了分析并給出了相應(yīng)的抑制措施,重點介紹了抑制器件的選用,最后通過對實際例子的分析表明在PCB設(shè)計中合理的選用抑制器件或抑制電路能夠有效的抑制瞬態(tài)干擾。

2018-08-10 08:00:00 0

0 共阻干擾是由PCB上大量的地線造成。當(dāng)兩個或兩個以上的回路共用一段地線時,不同的回路電流在共用地線上產(chǎn)生一定壓降,此壓降經(jīng)放大就會影響電路性能;當(dāng)電流頻率很高時,會產(chǎn)生很大的感抗而使電路受到干擾。

2019-06-19 14:50:16 1397

1397 熱干擾是PCB設(shè)計中必須要排除的重要因素。設(shè)元器件在工作中都有一定程度的發(fā)熱,尤其是功率較大的器件所發(fā)出的熱量會對周邊溫度比較敏感的器件產(chǎn)生干擾,若熱干擾得不到很好的抑制,那么整個電路的電性能就會發(fā)生變化。

2019-04-17 14:44:27 799

799 在電子產(chǎn)品的PCB設(shè)計中,抑制或防止地線干擾是需要考慮的最主要問題之一。

2019-06-04 10:56:19 4908

4908

PCB設(shè)計中,接地是抑制噪聲和防止干擾的重要措施。

2019-10-25 17:22:07 2777

2777 圖解PCB地線干擾及抑制對策

2019-08-20 08:47:50 6054

6054 共阻干擾是由PCB上大量的地線造成。當(dāng)兩個或兩個以上的回路共用一段地線時,不同的回路電流在共用地線上產(chǎn)生一定壓降,此壓降經(jīng)放大就會影響電路性能;當(dāng)電流頻率很高時,會產(chǎn)生很大的感抗而使電路受到干擾。

2019-10-08 15:32:25 908

908

在PCB板上抑制干擾的途徑有:

1、減小差模信號回路面積。

2、減小高頻噪聲回流(濾波、隔離及匹配)。

3、減小共模電壓(接地設(shè)計)。高速PCB EMC設(shè)計的47個原則二、PCB設(shè)計原則歸納

2019-12-05 14:38:01 4846

4846 印制板的設(shè)計是制作電子產(chǎn)品的重要一環(huán),隨著電子技術(shù)的飛速發(fā)展,PCB的密度越來越高,PCB設(shè)計的好壞對抗干擾能力影響很大。如果設(shè)計不合理會產(chǎn)生電磁干擾,使電路性能受到影響,甚至無法正常工作。

2022-11-28 09:13:15 1275

1275 降低PCB設(shè)計中噪聲與電磁干擾24條

2023-07-04 16:57:23 327

327 印制線應(yīng)遠(yuǎn)離干擾源且不能切割磁力線;避免平行走線,雙面板可以交叉通過,單面板可以通過“飛線”跨過;避免成環(huán),防止產(chǎn)生環(huán)形天線效應(yīng);時鐘信號布線應(yīng)與地線靠近,對于數(shù)據(jù)總線的布線應(yīng)在每兩根之間夾一根地線或緊挨著地址引線放置;

2023-08-02 14:49:01 374

374 共阻干擾是由PCB上大量的地線造成。當(dāng)兩個或兩個以上的回路共用一段地線時,不同的回路電流在共用地線上產(chǎn)生一定壓降,此壓降經(jīng)放大就會影響電路性能;當(dāng)電流頻率很高時,會產(chǎn)生很大的感抗而使電路受到干擾。

2023-08-15 14:23:00 406

406 PCB布線是ESD防護(hù)的一個關(guān)鍵要素,合理的PCB設(shè)計可以減少故障檢查和返工所帶來不必要的成本。在PCB設(shè)計中,不但需要在靜電薄弱電路增加靜電抑制器件,還要克服放電電流產(chǎn)生的電磁干擾(EMI)電磁場效應(yīng)。

2023-09-26 10:57:16 650

650

地線干擾與抑制

2022-12-30 09:21:19 2

2 地線干擾與抑制

2023-03-01 15:37:50 0

0 和低阻抗。為了達(dá)到這個目標(biāo),應(yīng)盡量采用大面積的地層,通過填充銅的方式增加地線的面積。同時,要將地線與其他信號線盡可能分開,避免交叉干擾。 2. 平面層布線 平面層是抑制電磁輻射的另一個重要手段。在PCB設(shè)計中,應(yīng)盡量使用多層板,其中一層作為

2023-11-23 10:07:31 356

356 在做PCB板的時候,為了減小干擾,地線是否應(yīng)該構(gòu)成閉和形式? 在PCB設(shè)計中,地線是非常重要的一個元素,它在整個電路板上形成了一個電氣和電磁環(huán)境的參考面。為了減小干擾,地線在電路板設(shè)計中的布局和連接

2023-11-24 14:51:08 453

453 電路是一個等電位體的定義僅是人們對地線電位的期望。HENRY給地線了一個更加符合實際的定義,他將地線定義為:信號流回源的低阻抗路徑。這個定義中突出了地線中電流的流動。按照這個定義,很容易理解地線中電位差的產(chǎn)生原因。

2023-11-27 15:54:58 204

204

電子發(fā)燒友App

電子發(fā)燒友App

評論