前面我們分析了EMI的產(chǎn)生情況,這節(jié)里我們將針對高速PCB設(shè)計(jì),來分析如何進(jìn)行EMI控制。

2012-03-31 11:07:14 1590

1590 隨著信號(hào)上升沿時(shí)間的減小及信號(hào)頻率的提高,電子產(chǎn)品的EMI問題越來越受到電子工程師的關(guān)注,幾乎60%的EMI問題都可以通過高速PCB來解決

2015-09-05 14:29:00 1691

1691

解決EMI問題的辦法很多,現(xiàn)代的EMI抑制方法包括:利用EMI抑制涂層、選用合適的EMI抑制零配件和EMI仿真設(shè)計(jì)等。本文從最基本的PCB布板出發(fā),討論PCB分層堆疊在控制EMI輻射中的作用和設(shè)計(jì)技巧。

2016-01-20 10:03:57 3541

3541 隨著信號(hào)上升沿時(shí)間的減小及信號(hào)頻率的提高,電子產(chǎn)品的EMI問題越來越受到電子工程師的關(guān)注,幾乎60%的EMI問題都可以通過高速PCB來解決。以下是高速PCB設(shè)計(jì)抗EMI干擾的九大規(guī)則: 規(guī)則一:高速

2018-04-13 08:20:00 1567

1567

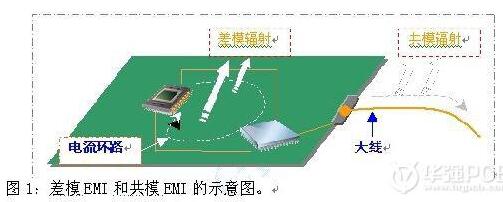

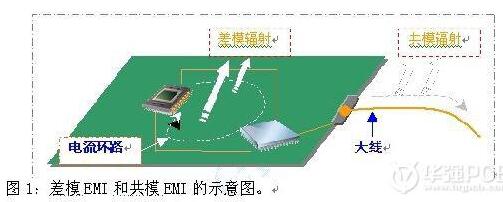

隨著IC器件集成度的提高、設(shè)備的逐步小型化和器件的速度愈來愈高,電子產(chǎn)品中的EMI問題也更加嚴(yán)重。從系統(tǒng)設(shè)備EMC/EMI設(shè)計(jì)的觀點(diǎn)來看,在設(shè)備的PCB設(shè)計(jì)階段處理好EMC/EMI問題,是使系統(tǒng)設(shè)備達(dá)到電磁兼容標(biāo)準(zhǔn)最有效、成本最低的手段。本文介紹數(shù)字電路PCB設(shè)計(jì)中的EMI控制技術(shù)。

2022-09-19 09:27:24 1257

1257 隨著信號(hào)上升沿時(shí)間的減小及信號(hào)頻率的提高,電子產(chǎn)品的EMI問題越來越受到電子工程師的關(guān)注,幾乎60%的EMI問題都可以通過高速PCB來解決。

2022-11-04 10:10:41 708

708 EMIPCB設(shè)計(jì)規(guī)范中來。C.EMI工程師對每一個(gè)外設(shè)口的EMI測試負(fù)有責(zé)任,不可漏測。D.每個(gè)PCB設(shè)計(jì)工程師有對該PCB設(shè)計(jì)規(guī)范作修改的建議權(quán)和質(zhì)疑的權(quán)力。EMI工程師有責(zé)任回答質(zhì)疑,對工程師的建議

2015-01-06 16:39:59

隨著信號(hào)上升沿時(shí)間的減小,信號(hào)頻率的提高,電子產(chǎn)品的EMI問題,也來越受到電子工程師的重視。高速pcb設(shè)計(jì)的成功,對EMI的貢獻(xiàn)越來越受到重視,幾乎60%的EMI問題可以通過高速PCB來控制解決。1

2021-12-31 06:22:08

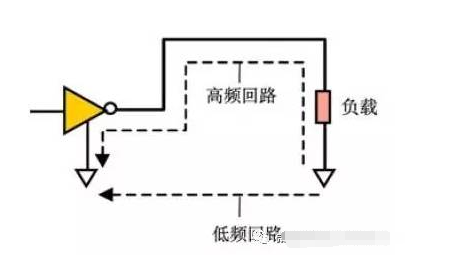

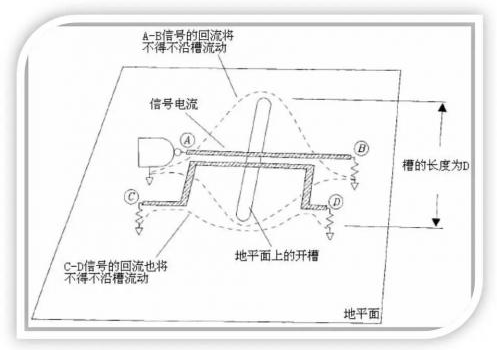

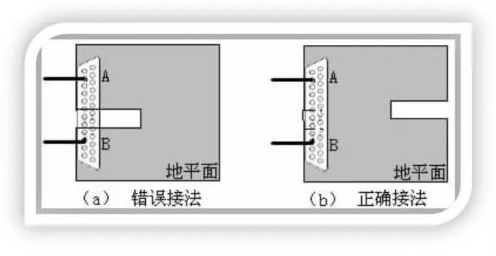

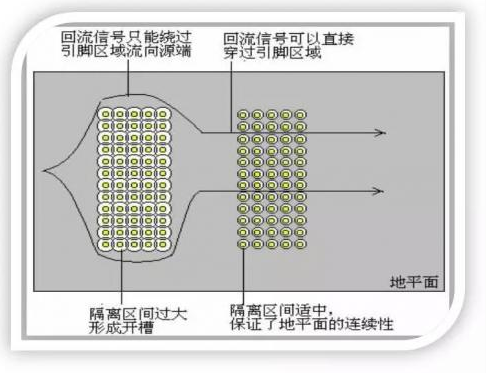

PCB 設(shè)計(jì)過程中開槽的形成 PCB 設(shè)計(jì)過程中開槽的形成包括: 對電源或地平面分割造成的開槽;當(dāng) PCB 板上存在多種不同的電源或地的時(shí)候,一般不可能為每一種電源網(wǎng)絡(luò)和地網(wǎng)絡(luò)分配一個(gè)完整的平面

2022-06-23 10:23:40

PCB 設(shè)計(jì)過程中開槽的形成PCB 設(shè)計(jì)過程中開槽的形成包括:對電源或地平面分割造成的開槽;當(dāng) PCB 板上存在多種不同的電源或地的時(shí)候,一般不可能為每一種電源網(wǎng)絡(luò)和地網(wǎng)絡(luò)分配一個(gè)完整的平面,常用

2020-12-17 09:49:40

或不重視的與印刷工藝相關(guān)的PCB不良設(shè)計(jì)予以歸納,以便相關(guān)設(shè)計(jì)人員盡快掌握好PCB設(shè)計(jì)。資料來自網(wǎng)絡(luò)資源

2019-06-13 22:09:58

引言 隨著IC器件集成度的提高、設(shè)備的逐步小型化和器件的速度愈來愈高,電子產(chǎn)品中的EMI問題也更加嚴(yán)重。從系統(tǒng)設(shè)備EMC/EMI設(shè)計(jì)的觀點(diǎn)來看,在設(shè)備的PCB設(shè)計(jì)階段處理好EMC/EMI問題,是使

2011-11-09 20:22:16

EMI問題是很多工程師在PCB設(shè)計(jì)遇到的最大挑戰(zhàn),由于電子產(chǎn)品信號(hào)處理頻率越來越高,EMI問題日益顯著,雖然有很多書籍對EMI問題進(jìn)行了探討,但是都不夠深入,《PCB設(shè)計(jì)中EMI控制原理與實(shí)戰(zhàn)

2011-05-19 15:58:44

得到IBIS模型。當(dāng)然,如果有SPICE模型,IBIS模型可以從SPICE模型來生成。目前,一般都可以從器件廠商那里拿到IBIS模型。應(yīng)用EMC/EMI仿真來提高PCB設(shè)計(jì)的質(zhì)量在PCB布局布線結(jié)束后,將

2014-12-22 11:52:49

布局布線

……

?

壇子里面的老司機(jī)分享,這些都是經(jīng)驗(yàn)之談,幫你少掉坑:

怎樣做一塊好的PCB板

如何解決多層PCB設(shè)計(jì)時(shí)的EMI

(轉(zhuǎn)載)PCB板去耦電容大小選擇與布置

PCB高級(jí)系列講座

花1萬元

2018-08-13 08:14:18

PCB 設(shè)計(jì)過程中開槽的形成 PCB 設(shè)計(jì)過程中開槽的形成包括: 對電源或地平面分割造成的開槽;當(dāng) PCB 板上存在多種不同的電源或地的時(shí)候,一般不可能為每一種電源網(wǎng)絡(luò)和地網(wǎng)絡(luò)分配一個(gè)完整的平面

2022-05-02 22:59:41

` 本帖最后由 jfzhangjin 于 2015-4-23 16:32 編輯

PCB設(shè)計(jì)工程師福利來咯~{:4_103:}細(xì)節(jié)體現(xiàn)態(tài)度,細(xì)節(jié)決定成敗,不管是多么高大上的產(chǎn)品,都離不開

2015-03-31 17:16:48

PCB怎樣入門?這里是PCB設(shè)計(jì)的入門

2019-05-11 14:22:20

(電磁兼容)和EMI(電磁干擾)的問題,所以對電子產(chǎn)品的電磁兼容分析顯得特別重要。與IC設(shè)計(jì)相比,PCB設(shè)計(jì)過程中的EMC分析和模擬仿真是一個(gè)薄弱環(huán)節(jié)。

2019-06-21 06:28:33

請問PCB設(shè)計(jì)規(guī)則怎樣設(shè)置?怎樣設(shè)置PCB的電氣規(guī)則檢查?比如說線寬,焊盤間的距離,線與線之間的間距,焊盤與線之間的間距怎樣定義設(shè)置?

2016-08-13 16:57:56

,不可避免地會(huì)引入EMC(電磁兼容)和EMI(電磁干擾)的問題,所以對電子產(chǎn)品的電磁兼容分析顯得特別重要。與IC設(shè)計(jì)相比,PCB設(shè)計(jì)過程中的EMC分析和模擬仿真是一個(gè)薄弱環(huán)節(jié)。

2019-07-22 06:45:44

的解決方案應(yīng)該屬于性能價(jià)格比較好的軟件,當(dāng)然Mentor的性能還是非常不錯(cuò)的,特別是它的設(shè)計(jì)流程管理方面應(yīng)該是最為優(yōu)秀的。 6、怎樣通過安排迭層來減少EMI問題? 首先,EMI要從系統(tǒng)考慮,單憑

2021-02-05 16:36:39

實(shí)時(shí)鉆頭表有哪些特征?在PCB設(shè)計(jì)中怎樣去放置實(shí)時(shí)鉆表?

2021-07-22 09:27:53

請問大神怎樣去編寫屬于自己的PCB設(shè)計(jì)規(guī)則檢查器?

2021-04-26 06:32:11

的PCB設(shè)計(jì)的方法:1、傳統(tǒng)繪制方法:在設(shè)計(jì)導(dǎo)電硅膠按鍵的PCB時(shí),對于其畫封裝可以采用軟件上面的“形狀”工具來繪畫,當(dāng)然也可以采用“線條”工具來畫,但一定要注意畫好以后的PCB,需要再選擇剛才的路徑

2019-11-21 14:39:59

怎樣通過安排迭層來減少EMI問題?為何要鋪銅?什么是“信號(hào)回流路徑”?如何對接插件進(jìn)行SI分析?請問端接的方式有哪些?采用端接(匹配)的方式有什么規(guī)則?PCB仿真軟件是如何進(jìn)行LAYOUT仿真的?PCB仿真軟件有哪些?

2021-04-25 09:23:14

請問:

AD9122 REFIO管腳沒有外接負(fù)載,如果沒有按手冊外接0.1uF電容濾波,對AD9122性能究竟會(huì)有什么不良影響,謝謝!

2023-12-15 07:14:59

EMC之PCB設(shè)計(jì)技巧

電磁兼容性(EMC)及關(guān)聯(lián)的電磁干擾(EMI)歷來都需要系統(tǒng)設(shè)計(jì)工程師擦亮眼睛,在當(dāng)今電路板設(shè)計(jì)和元器件封裝不斷縮小、OEM要求更高速系統(tǒng)的情況下,這兩大問題尤其令PCB布局

2023-12-19 09:53:34

allgro 16.3怎么做PCB的開槽請教大家,allgro 16.3怎么做pcb的開槽?就是需要把一小塊PCB的區(qū)域?qū)?yīng)的整個(gè)疊層全部被挖空,做出一個(gè)開槽。怎么操作才能實(shí)現(xiàn)呢?謝謝!

2014-10-20 17:16:52

在PCB設(shè)計(jì)和制作的過程中,你是不是也曾經(jīng)遇到過PCB吃錫不良的情況?對于工程師來說,一旦一塊PCB板出現(xiàn)吃錫不良問題,往往就意味著需要重新焊接甚至重新制作,所造成的后果非常令人頭痛。那么,PCB吃

2016-02-01 13:56:52

引言 隨著IC器件集成度的提高、設(shè)備的逐步小型化和器件的速度愈來愈高,電子產(chǎn)品中的EMI問題也更加嚴(yán)重。從系統(tǒng)設(shè)備EMC/EMI設(shè)計(jì)的觀點(diǎn)來看,在設(shè)備的PCB設(shè)計(jì)階段處理好EMC/EMI問題,是使

2019-09-16 22:37:29

解決EMI問題的辦法很多,現(xiàn)代的EMI抑制方法包括:利用EMI抑制涂層、選用合適的EMI抑制零配件和EMI仿真設(shè)計(jì)等。本文從最基本的PCB布板出發(fā),討論PCB分層堆疊在控制EMI輻射中的作用和設(shè)計(jì)技巧。

2019-07-25 07:02:48

多層板PCB設(shè)計(jì)時(shí)的EMI解決之道

2012-08-06 11:51:51

在PCB設(shè)計(jì)中,電磁兼容性(EMC)及關(guān)聯(lián)的電磁干擾(EMI)歷來是讓工程師們頭疼的兩大問題,特別是在當(dāng)今電路板設(shè)計(jì)和元器件封裝不斷縮小、OEM要求更高速系統(tǒng)的情況下。本文給大家分享如何在PCB設(shè)計(jì)中避免出現(xiàn)電磁問題。

2021-02-01 07:42:30

如何在PCB設(shè)計(jì)階段處理好EMC及其EMI的問題呢?有什么解決辦法嗎?

2023-04-06 15:52:59

在高速PCB設(shè)計(jì)時(shí)為了防止反射就要考慮阻抗匹配,但由于PCB的加工工藝限制了阻抗的連續(xù)性而仿真又仿不到,在原理圖的設(shè)計(jì)時(shí)怎樣來考慮這個(gè)問題?另外關(guān)于IBIS模型,不知在那里能提供比較準(zhǔn)確的IBIS

2012-03-03 12:41:55

作為一名合格的、優(yōu)秀的PCB設(shè)計(jì)工程師,我們不僅要掌握高速PCB設(shè)計(jì)技能,還需要對其他相關(guān)知識(shí)有所了解,比如高速PCB材料的選擇。這是因?yàn)椋?b class="flag-6" style="color: red">PCB材料的選擇錯(cuò)誤也會(huì)對高速數(shù)字電路的信號(hào)傳輸性能造成不良影響。

2021-03-09 06:14:27

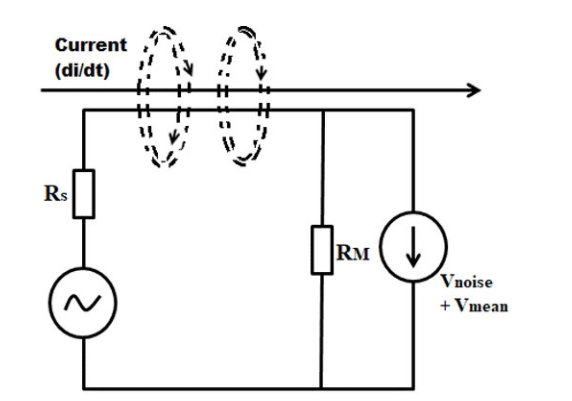

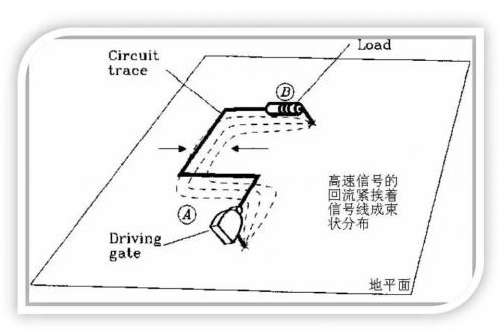

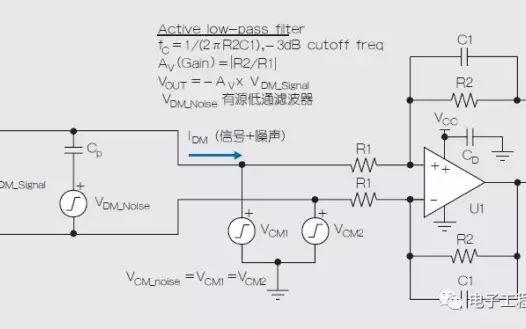

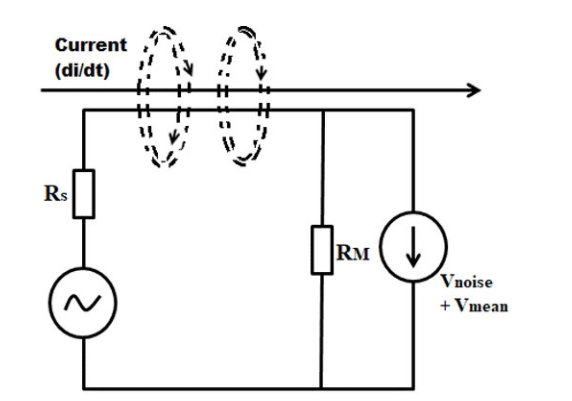

和方式,這里我們將針對高速PCB設(shè)計(jì),來分析如何進(jìn)行EMI控制。1、傳輸線RLC參數(shù)和EMI對于PCB板來說,PCB上的每一條走線都可以有用三個(gè)基本的分布參數(shù)來對它進(jìn)行描述,即電阻,電容和電感。在EMI

2019-05-20 08:30:00

詳解高速DSP系統(tǒng)PCB板的可靠性設(shè)計(jì)教你學(xué)會(huì)減少諧波失真的PCB設(shè)計(jì)方法闡述列車用高速數(shù)字PCB電路板抗干擾設(shè)計(jì)初學(xué)PCB的EMI設(shè)計(jì)心得以及高速PCB背板設(shè)計(jì)方案多層板PCB設(shè)計(jì)時(shí)的EMI解決方案

2014-12-16 13:55:37

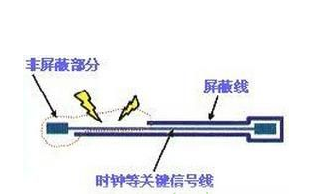

隨著信號(hào)上升沿時(shí)間的減小及信號(hào)頻率的提高,電子產(chǎn)品的EMI問題越來越受到電子工程師的關(guān)注,幾乎60%的EMI問題都可以通過高速PCB來解決。以下是九大規(guī)則:規(guī)則一:高速信號(hào)走線屏蔽規(guī)則在高速

2017-11-02 12:11:12

請問一下PCB設(shè)計(jì)需怎樣自查?

2021-04-21 06:49:21

本帖最后由 eehome 于 2013-1-5 10:00 編輯

靜電會(huì)對絕緣柵型場效應(yīng)管(MOS管)造成不良影響,如果柵極懸空會(huì)被擊穿。因?yàn)殪o電電壓很高,一般是幾百伏或者幾千伏,而管子?xùn)艠O

2012-07-11 11:38:36

隨著信號(hào)上升沿時(shí)間的減小及信號(hào)頻率的提高,電子產(chǎn)品的EMI問題越來越受到電子工程師的關(guān)注,幾乎60%的EMI問題都可以通過高速PCB來解決。

2023-09-25 08:04:42

隨著信號(hào)上升沿時(shí)間的減小及信號(hào)頻率的提高,電子產(chǎn)品的EMI問題越來越受到電子工程師的關(guān)注,幾乎60%的EMI問題都可以通過高速PCB來解決。以下是九大規(guī)則:

2019-07-25 06:56:17

隨著信號(hào)上升沿時(shí)間的減小及信號(hào)頻率的提高,電子產(chǎn)品的EMI問題越來越受到電子工程師的關(guān)注,幾乎60%的EMI問題都可以通過高速PCB來解決。以下是九大規(guī)則: 高速PCB設(shè)計(jì)解決EMI問題的九大規(guī)則

2016-01-19 22:50:31

PCB設(shè)計(jì)時(shí)怎樣抗靜電放電

靜電對于精密的半導(dǎo)體芯片會(huì)造成各種損傷,例如穿透元器件內(nèi)部薄的絕緣層;損毀MOSFET和CMOS元器件的柵極

2010-03-13 14:55:50 1661

1661 目前,EMI問題是很多工程師在PCB設(shè)計(jì)遇到的最大挑戰(zhàn),由于電子產(chǎn)品信號(hào)處理頻率越來越高,EMI問題日益顯著,雖然有很多書籍對EMI問題進(jìn)行了探討,但是都不夠深入,《PCB設(shè)計(jì)中EMI控

2011-09-05 14:29:17 0

0 PCB設(shè)計(jì)相關(guān)經(jīng)驗(yàn)分享及PCB新手在PCB設(shè)計(jì)中應(yīng)該注意的問題

2013-09-06 14:59:47 0

0 【PCB設(shè)計(jì)技巧】覆銅技巧【PCB設(shè)計(jì)技巧】覆銅技巧【PCB設(shè)計(jì)技巧】覆銅技巧

2016-02-26 16:59:59 0

0 如何快速解決PCB設(shè)計(jì)EMI問題

2017-01-14 12:48:43 0

0 應(yīng)用就非常重要了。但目前國內(nèi)國際的普遍情況是,與IC設(shè)計(jì)相比,PCB設(shè)計(jì)過程中的EMC分析和模擬仿真是一個(gè)薄弱環(huán)節(jié)。同時(shí),EMC仿真分析目前在PCB設(shè)計(jì)中逐漸占據(jù)越來越重要的角色。 PCB設(shè)計(jì)中的對EMC/EMI的分析目標(biāo)信號(hào)完整性分析包括同一布線網(wǎng)絡(luò)上同一信

2017-12-04 11:39:11 0

0 本文主要介紹的是pcb開窗,首先介紹了PCB設(shè)計(jì)中的開窗和亮銅,其次介紹了如何實(shí)現(xiàn)PCB走線開窗上錫,最后闡述了PCB設(shè)計(jì)怎樣設(shè)置走線開窗的步驟,具體的跟隨小編一起來了解一下。

2018-05-04 15:37:30 34498

34498

隨著IC器件集成度的提高、設(shè)備的逐步小型化和器件的速度愈來愈高,電子產(chǎn)品中的EMI問題也更加嚴(yán)重。從系統(tǒng)設(shè)備EMC/EMI設(shè)計(jì)的觀點(diǎn)來看,在設(shè)備的PCB設(shè)計(jì)階段處理好EMC/EMI問題,是使系統(tǒng)設(shè)備達(dá)到電磁兼容標(biāo)準(zhǔn)最有效、成本最低的手段。本文介紹數(shù)字電路PCB設(shè)計(jì)中的EMI控制技術(shù)。

2018-08-25 09:08:00 1820

1820

PCB設(shè)計(jì)紛繁復(fù)雜,各種意料之外的因素頻頻來影響整體方案的達(dá)成,如何能馴服性格各異的零散部件?怎樣才能畫出一份整齊、高效、可靠的PCB圖?今天就讓我們來盤點(diǎn)一下。

2018-09-23 09:36:00 6277

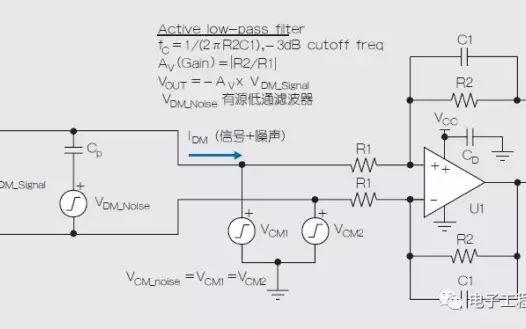

6277 由于PCB板上的電子器件密度越來越大,走線越來越窄,走線密度也越來越高,信號(hào)的頻率也越來越高,不可避免地會(huì)引入EMC(電磁兼容)和EMI(電磁干擾)的問題,所以對電子產(chǎn)品的電磁兼容分析以及

2018-10-16 10:18:00 2737

2737 PCB設(shè)計(jì)中怎樣消除反射噪聲

2019-08-17 20:31:00 2446

2446

優(yōu)秀PCB設(shè)計(jì)練習(xí)降低PCB的EMI有許多方法可以降低PCB設(shè)計(jì)的EMI基本原理:電源和地平面提供屏蔽頂層和

2019-02-28 15:04:20 3032

3032

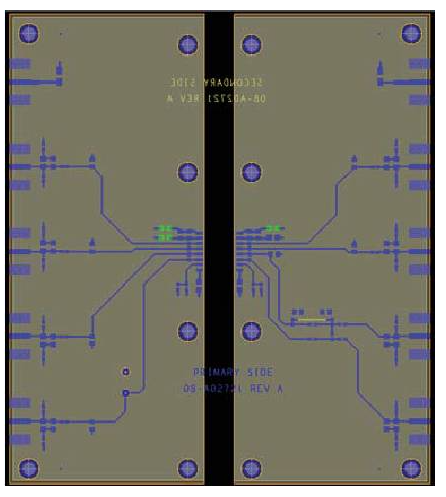

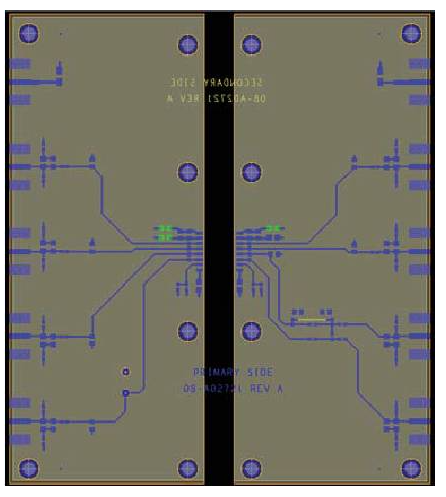

PCB布局、布線以及電源層的處理對整個(gè)電路板的EMI問題有著非常重要的影響。本文將通過實(shí)例分析討論如何利用EMIStream來解決板級(jí)EMI問題。隨著電子系統(tǒng)的復(fù)雜度越來越高,EMI問題也越來越多。為了使自己的產(chǎn)品能達(dá)到相關(guān)國際標(biāo)準(zhǔn),設(shè)計(jì)人員不得不往返于辦公室和EMC實(shí)驗(yàn)室,反復(fù)地測試、修改設(shè)計(jì)、再測試。

2019-06-14 14:58:54 2741

2741

隨著,信號(hào)上升沿時(shí)間的減小,信號(hào)頻率的提高,電子產(chǎn)品的EMI問題,也來越受到電子工程師的光注。高速PCB設(shè)計(jì)的成功,對EMI的貢獻(xiàn)越來越受到重視,幾乎60%的EMI問題可以通過高速PCB來控制解決。

2019-06-05 14:56:36 587

587

在PCB設(shè)計(jì)中,EMC/EMI主要分析布線網(wǎng)絡(luò)本身的信號(hào)完整性,實(shí)際布線網(wǎng)絡(luò)可能產(chǎn)生的電磁輻射和電磁干擾以及電路板本身抵抗外部電磁干擾的能力,并且依據(jù)設(shè)計(jì)者的要求提出布局和布線時(shí)抑制電磁輻射和干擾

2019-05-31 15:03:10 1474

1474 pcb出現(xiàn)上錫不良一般和PCB空板表面的潔凈度相關(guān),沒有污染的話基本上不會(huì)有上錫不良,二是, 上錫時(shí)本身的助焊劑不良,溫度等。

2019-04-24 15:30:33 11620

11620 PCB設(shè)計(jì)和制作過程有20道工序之多,上錫不良還真是個(gè)另人頭疼的問題,電路板上錫不良可能導(dǎo)致諸如線路沙孔、崩線、線路狗牙、開路、線路沙孔幼線;孔銅薄嚴(yán)重則成孔無銅;孔銅薄嚴(yán)重則成孔無銅孔銅薄嚴(yán)重

2019-04-24 15:34:02 7207

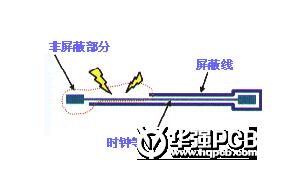

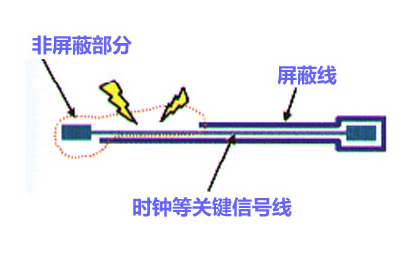

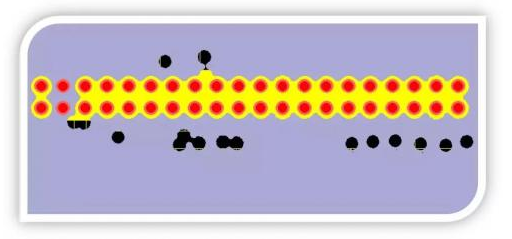

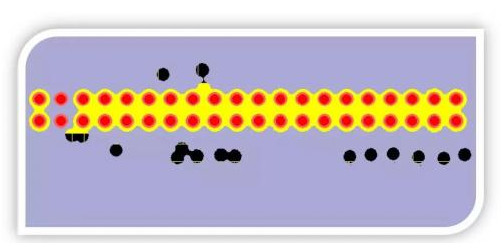

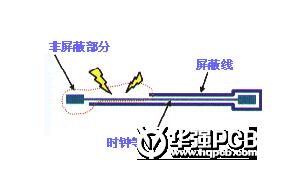

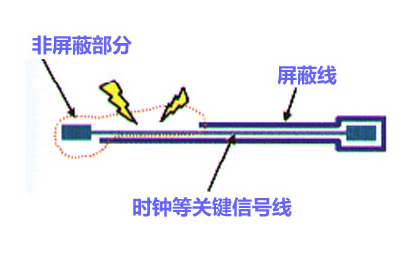

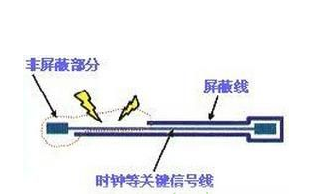

7207 在高速的PCB設(shè)計(jì)中,時(shí)鐘等關(guān)鍵的高速信號(hào)線,走線需要進(jìn)行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都會(huì)造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地。

2019-05-06 18:08:15 3981

3981 它易于學(xué)習(xí)且易于使用的界面用于簡單的布局,而且還具有用于更高級(jí)PCB設(shè)計(jì)的強(qiáng)大功能。

2019-08-15 19:20:00 772

772 解決EMI問題的辦法很多,現(xiàn)代的EMI抑制方法包括:利用EMI抑制涂層、選用合適的EMI抑制零配件和EMI仿真設(shè)計(jì)等。本文從最基本的PCB布板出發(fā),討論PCB分層堆疊在控制EMI輻射中的作用和設(shè)計(jì)技巧。

2019-08-15 06:36:00 1217

1217 出現(xiàn)上錫不良一般和PCB空板表面的潔凈度相關(guān),沒有污染的話基本上不會(huì)有上錫不良,二是, 上錫時(shí)本身的助焊劑不良,溫度等。

2020-04-09 16:53:41 3536

3536 PCB設(shè)計(jì)的自查流程介紹

2019-12-31 17:37:17 1524

1524 優(yōu)秀PCB設(shè)計(jì)練習(xí)降低PCB的EMI有許多方法可以降低PCB設(shè)計(jì)的EMI基本原理:電源和地平面提供屏蔽頂層和

2019-08-20 09:11:38 3845

3845 SI-list【中國】一篇文章,搞定以太網(wǎng)PCB設(shè)計(jì)

2019-08-20 10:38:55 3406

3406 高速PCB設(shè)計(jì)EMI有什么規(guī)則

2019-08-21 14:38:03 807

807

解決EMI問題的辦法很多,現(xiàn)代的EMI抑制方法包括:利用EMI抑制涂層、選用合適的EMI抑制零配件和EMI仿真設(shè)計(jì)等。

2019-08-26 08:55:42 371

371 EAGLE CAD怎樣做更簡單的PCB設(shè)計(jì)

2019-09-10 17:51:32 8049

8049

現(xiàn)代的EMI抑制方法包括:利用EMI抑制涂層、選用合適的EMI抑制零配件和EMI仿真設(shè)計(jì)等。

2019-09-04 10:36:01 557

557 低EMI DC/DC變換器PCB設(shè)計(jì)

2020-02-04 15:26:08 3835

3835 隨著信號(hào)上升沿時(shí)間的減小,信號(hào)頻率的提高,電子產(chǎn)品的EMI問題,也來越受到電子工程師的重視。高速pcb設(shè)計(jì)的成功,對EMI的貢獻(xiàn)越來越受到重視,幾乎60%的EMI問題可以通過高速PCB來控制解決。

2020-03-25 15:55:28 1400

1400

對電源或地平面分割造成的開槽;當(dāng)PCB板上存在多種不同的電源或地的時(shí)候,一般不可能為每一種電源網(wǎng)絡(luò)和地網(wǎng)絡(luò)分配一個(gè)完整的平面,常用的做法是在一個(gè)或多個(gè)平面上進(jìn)行電源分割或地分割。

2020-07-09 16:21:04 3037

3037

NCAB為工程師、設(shè)計(jì)師以及所有PCB設(shè)計(jì)與制造過程的參與者創(chuàng)建了一個(gè)工具,這個(gè)工具總結(jié)了一些可能對PCB成品產(chǎn)生不良影響的常見設(shè)計(jì)錯(cuò)誤,以及如何避免這些錯(cuò)誤的發(fā)生。 導(dǎo)致錯(cuò)誤的原因很復(fù)雜,例如

2020-09-25 14:29:49 1660

1660 PCB設(shè)計(jì)布局被認(rèn)為是促進(jìn)EMI在電路中傳播的主要問題之一。這就是為什么在開關(guān)電源中降低EMI的普遍而通用的技術(shù)之一是布局優(yōu)化。

2021-01-28 10:58:06 2089

2089

下文是硬件工程師在PCB設(shè)計(jì)早期容易忽略,卻很有用的幾個(gè)EMI設(shè)計(jì)指南,這些指南也在一些權(quán)威書刊中常常被提到。

2020-10-09 09:54:57 3137

3137 PCB設(shè)計(jì)盡量讓電源平面和地平面緊耦合,讓鄰近的兩個(gè)面之間形成耦合平面電容。

2021-04-20 11:23:18 5372

5372

“隨著IC器件集成度的提高、設(shè)備的逐步小型化和器件的速度愈來愈高,電子產(chǎn)品中的EMI問題也更加嚴(yán)重。從系統(tǒng)設(shè)備EMC/EMI設(shè)計(jì)的觀點(diǎn)來看,在設(shè)備的PCB設(shè)計(jì)階段處理好EMC/EMI問題,是使系統(tǒng)設(shè)備達(dá)到電磁兼容標(biāo)準(zhǔn)最有效、成本最低的手段。

2020-11-10 10:47:11 1714

1714

原文標(biāo)題:PPT|鋰電池K值概念、K值不良影響因素及不良分析方法 文章出處:【微信公眾號(hào):鋰電聯(lián)盟會(huì)長】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。 責(zé)任編輯:haq

2020-11-13 10:05:29 22921

22921 PCB設(shè)計(jì)之在真實(shí)世界里的EMI控制說明。

2021-06-23 14:53:34 0

0 串?dāng)_通常是EMI的主要貢獻(xiàn)者。 不良的PCB布局可能會(huì)增加內(nèi)部噪聲電路和I/O線路的耦合,從而“輸出”EMI,即電磁發(fā)射。

2022-11-01 14:26:15 1118

1118 隨著信號(hào)上升沿時(shí)間的減小,信號(hào)頻率的提高,電子產(chǎn)品的EMI問題,也來越受到電子工程師的重視。高速pcb設(shè)計(jì)的成功,對EMI的貢獻(xiàn)越來越受到重視,幾乎60%的EMI問題可以通過高速PCB來控制解決。

2022-11-11 11:44:51 528

528 深圳PCB制造廠家與您分享PCB設(shè)計(jì)中的EMC問題與哪些因素有關(guān)? PCB設(shè)計(jì)中與EMC問題有關(guān)的因素 1.系統(tǒng)設(shè)計(jì): 在進(jìn)行系統(tǒng)級(jí)EMC設(shè)計(jì)時(shí),首先要確定EMI干擾源,以便逐步更好地屏蔽EMI輻射源。 2.結(jié)構(gòu)影響: 非金屬機(jī)箱輻射騷擾發(fā)射超標(biāo),應(yīng)采取導(dǎo)電噴涂、局部屏蔽設(shè)計(jì)、電纜屏蔽

2023-09-06 09:30:05 610

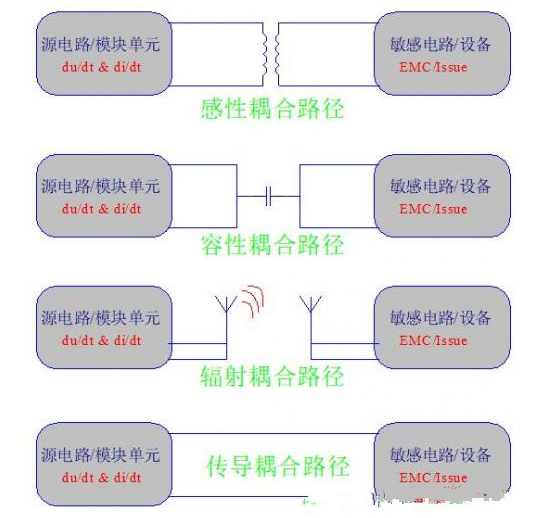

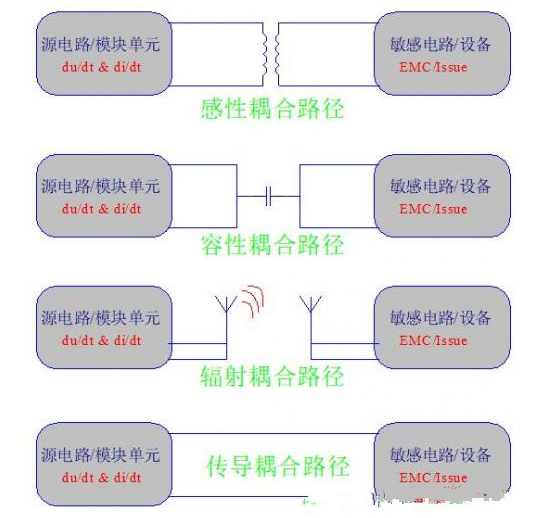

610 從上面的三要素中,我們對EMI的傳播路徑:空間耦合和傳導(dǎo)耦合比較熟悉;我們實(shí)際也是重點(diǎn)在運(yùn)用上述的理論來進(jìn)行我們的實(shí)踐指導(dǎo);在實(shí)際進(jìn)行電路設(shè)計(jì)時(shí)我們PCB的設(shè)計(jì)也很關(guān)鍵;基本60%的EMC問題都是PCB設(shè)計(jì)的問

2023-12-18 16:22:05 138

138

通孔過于密集形成開槽(通孔包括焊盤和過孔);通孔穿過地層或電源層而與之沒有電氣連接時(shí),需要在通孔周圍留一些空間以便進(jìn)行電氣隔離;但當(dāng)通孔之間的距離靠得太近時(shí),隔離環(huán)就會(huì)重疊起來,形成開槽。

2023-12-27 16:12:00 95

95

的不良影響。在進(jìn)行PCB布線設(shè)計(jì)時(shí),需要遵循一定的規(guī)則和原則,下面我們將會(huì)介紹PCB設(shè)計(jì)中的六大布線規(guī)則。 PCB設(shè)計(jì)六大布線規(guī)則 一:按照傳輸信號(hào)速度分類 在布線時(shí)需要按照信號(hào)傳輸速度的不同進(jìn)行分類布線。一般來說,傳輸速度越快的信號(hào)需要

2024-01-22 09:23:53 498

498

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論