Altera公司 (NASDAQ: ALTR)今天宣布,其28 nm Stratix? V GX FPGA已經(jīng)收錄在最新的PCI-SIG? Integrators名錄中,符合PCI Express? (PCIe?) 3.0規(guī)范(Gen3)要求。

2013-05-23 10:34:54 1803

1803 ? ? ? ? ? ? ?并未建立SRIO協(xié)議,僅僅通過(guò)收發(fā)器發(fā)送PRBS,在這種情況下是否能使用external line loopback方式來(lái)測(cè)試鏈路的信號(hào)完整性?

? ? ? ? 2、查看

2018-06-21 06:25:29

本帖最后由 eehome 于 2013-1-5 09:47 編輯

Altera Stratix V GX FPGA開(kāi)發(fā)板電路圖

2012-08-13 22:22:08

SoC FPGA以及開(kāi)發(fā)套件。Stratix V FPGA系列包括含有大量邏輯的E型號(hào),以及含有速率高達(dá)28 Gbps集成收發(fā)器的GX、GS和GT型號(hào)。Stratix V FPGA是唯一具有精度可調(diào)

2012-05-14 12:38:53

做了電路設(shè)計(jì)有一段時(shí)間,發(fā)現(xiàn)信號(hào)完整性不僅需要工作經(jīng)驗(yàn),也需要很強(qiáng)的理論指導(dǎo),壇友能提供一些信號(hào)完整性的視頻資料么?非常感謝!

2019-02-14 14:43:52

在altium designer中想進(jìn)行信號(hào)完整性的分析,可元件是自己造的,不知道仿真模型怎么建,哪些HC是啥意思也不知道

2012-11-01 21:43:04

多,下面就來(lái)了解了解吧。 信號(hào)完整性與電源完整性分析信號(hào)完整性(SI)和電源完整性(PI)是兩種不同但領(lǐng)域相關(guān)的分析,涉及數(shù)字電路正確操作。在信號(hào)完整性中,重點(diǎn)是確保傳輸?shù)?在接收器中看起來(lái)就像 1

2019-06-17 10:23:53

信號(hào)完整性100條經(jīng)驗(yàn)規(guī)則

2020-12-29 06:55:21

高速設(shè)計(jì)中的信號(hào)完整性和電源完整性分析

2021-04-06 07:10:59

信號(hào)完整性是指信號(hào)在通過(guò)一定距離的傳輸路徑后在特定接收端口相對(duì)指定發(fā)送端口信號(hào)的還原程度。在討論信號(hào)完整性設(shè)計(jì)的性能時(shí),如果指定不同的收發(fā)參考端口,就要用不同的指標(biāo)來(lái)描述信號(hào)還原程度。通常情況下指定

2015-01-07 11:33:53

信號(hào)完整性與電源完整性的仿真分析與設(shè)計(jì),不看肯定后悔

2021-05-12 06:40:35

最近在論壇里看到一則關(guān)于電源完整性的提問(wèn),網(wǎng)友質(zhì)疑大家普遍對(duì)信號(hào)完整性很重視,但對(duì)于電源完整性的重視好像不夠,主要是因?yàn)椋瑢?duì)于低頻應(yīng)用,開(kāi)關(guān)電源的設(shè)計(jì)更多靠的是經(jīng)驗(yàn),或者功能級(jí)仿真來(lái)輔助即可,電源

2021-11-15 09:07:04

的1在接收器中看起來(lái)就像 1(對(duì)0同樣如此)。在電源完整性中,重點(diǎn)是確保為驅(qū)動(dòng)器和接收器提供足夠的電流以發(fā)送和接收1和0。因此,電源完整性可能會(huì)被認(rèn)為是信號(hào)完整性的一個(gè)組成部分。實(shí)際上,它們都是關(guān)于數(shù)字電...

2021-11-15 07:37:08

先說(shuō)一下,信號(hào)完整性為什么寫(xiě)電源完整性? SI 只是針對(duì)高速信號(hào)的部分,這樣的理解沒(méi)有問(wèn)題。如果提高認(rèn)知,將SI 以大類(lèi)來(lái)看,SI&PI&EMI 三者的關(guān)系:所以,基礎(chǔ)知識(shí)系列里還是

2021-11-15 06:32:45

高速PCB設(shè)計(jì)有很多比較考究的點(diǎn),包括常規(guī)的設(shè)計(jì)要求、信號(hào)完整性的要求、電源完整性的要求、EMC的要求、特殊設(shè)計(jì)要求等等。本文主要是針對(duì)高速電路信號(hào)總線做了一些比較常規(guī)的要求列舉了一些檢查要點(diǎn),其實(shí)

2021-01-14 07:11:25

中國(guó)電子電器可靠性工程協(xié)會(huì)關(guān)于組織召開(kāi)“信號(hào)完整性仿真應(yīng)用”高級(jí)研修班的邀請(qǐng)函各有關(guān)單位:為了幫助廣大從業(yè)人員詳細(xì)了解信號(hào)完整性(SI)和電源完整性(PI)的基本概念、分析方法和應(yīng)用實(shí)例,幫助電子

2009-11-25 10:13:20

信號(hào)完整性關(guān)鍵名詞都有什么 ?

2021-03-05 08:09:37

信號(hào)完整性分析

2013-06-04 14:26:04

信號(hào)完整性分析

2013-06-04 14:36:09

信號(hào)完整性分析,很不錯(cuò)的教材可以下載看一看。

2016-06-23 18:45:23

信號(hào)完整性資料

2015-09-18 17:26:36

很不錯(cuò)的一本信號(hào)完整性教材。其實(shí)EMC、EMI問(wèn)題最終都是信號(hào)完整性問(wèn)題。

2011-12-09 22:49:23

手工連線面成的樣機(jī)同規(guī)范布線的最終印制板產(chǎn)品一樣都能正常工作。

但是現(xiàn)在時(shí)鐘頻率提高了,信號(hào)上升邊也已普遍變短。對(duì)大多數(shù)電子產(chǎn)品而言,當(dāng)時(shí)鐘頻率超過(guò)100MHz或上升邊小于1 ns時(shí),信號(hào)完整性效應(yīng)

2023-09-28 08:18:07

信號(hào)完整性分析與設(shè)計(jì)信號(hào)完整性設(shè)計(jì)背景???什什么是信號(hào)完整D??信信號(hào)完整性設(shè)計(jì)內(nèi)è??典典型信號(hào)完整性問(wèn)題與對(duì)2現(xiàn)在數(shù)字電路發(fā)展的趨ê??速速率越來(lái)越???芯芯片集成度越來(lái)越高£P(guān)C板板越來(lái)越

2009-09-12 10:20:03

信號(hào)完整性的定義信號(hào)完整性包含哪些內(nèi)容

2021-03-04 06:09:35

信號(hào)完整性基礎(chǔ)

2013-11-14 22:26:42

信號(hào)完整性處理的8個(gè)基本原則

2021-01-14 07:19:08

://pan.baidu.com/s/1jG0JbjK信號(hào)完整性小結(jié)1、信號(hào)完整性問(wèn)題關(guān)心的是用什么樣的物理互連線才能確保芯片輸出信號(hào)的原始質(zhì)量。2、信號(hào)完整性問(wèn)題一般分為四種:?jiǎn)我痪W(wǎng)絡(luò)的信號(hào)質(zhì)量、相鄰網(wǎng)絡(luò)間的串

2015-12-12 10:30:56

本文主要介紹信號(hào)完整性是什么,信號(hào)完整性包括哪些內(nèi)容,什么時(shí)候需要注意信號(hào)完整性問(wèn)題?

2021-01-25 06:51:11

請(qǐng)問(wèn)一下信號(hào)完整性的價(jià)值是什么?

2021-04-09 06:15:23

AD信號(hào)完整性分析的資料,需要用到AD信號(hào)完整性分析的同學(xué)可以下載下來(lái)看看,資料講得挺詳細(xì)的!

2016-04-19 16:53:48

Cadenc高速電路設(shè)計(jì)SI PI 信號(hào)完整性電源完整性仿真視頻教程下載鏈接地址:鏈接:http://pan.baidu.com/s/1pJiPpzl密碼:3yjv

2015-07-30 21:44:10

在低成本的 FPGA 中,Cyclone? IV GX 器件內(nèi)嵌多達(dá)八個(gè)全雙工收發(fā)器,運(yùn)行在 600Mbps 到 3.125 Gbps 的串行數(shù)據(jù)速率上。 表 1-1 列出了 Cyclone IV GX 收發(fā)器通道所支持的串行協(xié)議信息。

2017-11-14 10:54:41

E— 最低的功耗,通過(guò)最低的成本實(shí)現(xiàn)較高的功能性■ Cyclone IV GX— 最低的功耗,集成了 3.125 Gbps 收發(fā)器的最低成本的 FPGA1 Cyclone IV E 器件可以在 1.0

2017-11-13 11:22:50

Cyclone? IV GX 器件提供了多個(gè)復(fù)位信號(hào)來(lái)對(duì)收發(fā)器通道進(jìn)行獨(dú)立地控制。ALTGXTransceiver MegaWizard ?插件管理器對(duì)設(shè)計(jì)中例化的每個(gè)通道均提供了單獨(dú)的復(fù)位信號(hào)。此外,它對(duì)每個(gè)收發(fā)器模塊也提供了一個(gè)斷電 (power-down) 信號(hào)。

2017-11-14 10:56:40

信號(hào)完整性(Signal Integrity, SI)是指信號(hào)在信號(hào)線上的質(zhì)量,即信號(hào)在電路中以正確的時(shí)序和電壓作出響應(yīng)的能力。如果電路中信號(hào)能夠以要求的時(shí)序、持續(xù)時(shí)間和電壓幅度到達(dá)接收器,則可

2018-11-27 15:22:34

VNA是如何測(cè)量高速器件的信號(hào)完整性(SI)?

2021-05-11 06:49:40

`編輯推薦《國(guó)外電子與通信教材系列:信號(hào)完整性與電源完整性分析(第二版)》強(qiáng)調(diào)直覺(jué)理解、實(shí)用工具和工程素養(yǎng)。作者以實(shí)踐專(zhuān)家的視角指出造成信號(hào)完整性問(wèn)題的根源,并特別給出了設(shè)計(jì)階段前期的問(wèn)題解決

2017-09-19 18:21:05

為什么要在意電源系統(tǒng)的信號(hào)完整性?電源系統(tǒng)的噪聲余量分析電源噪聲是如何產(chǎn)生的呢?

2021-02-24 08:00:33

什么時(shí)候需要進(jìn)行信號(hào)完整性分析

2014-12-10 10:30:11

日前,Altera發(fā)布新系列Cyclone IV FPGA ,延續(xù)其收發(fā)器技術(shù)的領(lǐng)先優(yōu)勢(shì)。當(dāng)前移動(dòng)視頻、語(yǔ)音和數(shù)據(jù)訪問(wèn)以及高質(zhì)量3D圖像對(duì)低成本帶寬需求與日俱增,與此同時(shí),終端產(chǎn)品市場(chǎng),如智能電話等

2019-07-31 06:59:45

想了解什么是信號(hào)完整性的朋友,可以進(jìn)來(lái)看看

2013-04-24 14:11:10

首先我們定義下什么是電源和信號(hào)完整性?信號(hào)完整性 信號(hào)完整性(SI)分析集中在發(fā)射機(jī)、參考時(shí)鐘、信道和接收機(jī)在誤碼率(BER)方面的性能。電源完整性(PI)側(cè)重于電源分配網(wǎng)絡(luò) (PDN) 提供恒定

2021-12-30 06:33:36

何為信號(hào)完整性:信號(hào)完整性(Signal Integrity,簡(jiǎn)稱(chēng)SI)是指在信號(hào)線上的信號(hào)質(zhì)量。差的信號(hào)完整性不是由某一單一因素導(dǎo)致的,而是板級(jí)設(shè)計(jì)中多種因素共同引起的。當(dāng)電路中信號(hào)能以要求的時(shí)序

2021-12-30 08:15:58

如何保證脈沖信號(hào)傳輸?shù)?b class="flag-6" style="color: red">完整性,減少信號(hào)在傳輸過(guò)程中產(chǎn)生的反射和失真,已成為當(dāng)前高速電路設(shè)計(jì)中不可忽視的問(wèn)題。

2021-04-07 06:53:25

高速數(shù)字PCB設(shè)計(jì)信號(hào)完整性解決方法

2021-03-29 08:12:25

何為信號(hào)完整性?信號(hào)完整性包括哪些?干擾信號(hào)完整性的因素有哪些?如何去解決?

2021-05-06 07:00:23

高速PCB頻發(fā)故障,使得信號(hào)完整性問(wèn)題越來(lái)越受到工程師的重視。有關(guān)高速PCB信號(hào)完整性的相關(guān)內(nèi)容網(wǎng)絡(luò)上有很多,這方面的知識(shí)點(diǎn)很容易找到資源學(xué)習(xí),我本人也寫(xiě)過(guò)一本拙作《信號(hào)完整性揭秘》。但是,學(xué)習(xí)理論

2017-06-23 11:52:11

信號(hào)完整性(SI)問(wèn)題解決得越早,設(shè)計(jì)的效率就越高,從而可避免在電路板設(shè)計(jì)完成之后才增加端接器件。SI設(shè)計(jì)規(guī)劃的工具和資源不少,本文主要探索,究竟還有什么辦法可以確保信號(hào)完整性?

2019-08-02 07:52:35

之前在總結(jié)StratixIVGX的Transceiver模塊的時(shí)候說(shuō)道Altera的開(kāi)發(fā)板并未使用到CMU通道,其實(shí)這個(gè)說(shuō)法是不對(duì)的,今天在看其一款SI(即研究Transceiver信號(hào)完整性

2014-12-03 15:16:21

昨天在總結(jié)StratixIVGX的Transceiver模塊的時(shí)候說(shuō)道Altera的開(kāi)發(fā)板并未使用到CMU通道,其實(shí)這個(gè)說(shuō)法是不對(duì)的,今天在看其一款SI(即研究Transceiver信號(hào)完整性

2015-01-20 17:28:58

對(duì)任何優(yōu)秀的示波器系統(tǒng)來(lái)說(shuō),準(zhǔn)確重建波形的能力都是關(guān)鍵,這種能力稱(chēng)為信號(hào)完整性。示波器類(lèi)似于一臺(tái)攝像機(jī),它捕獲信號(hào)圖像,然后可以觀察和解釋信號(hào)圖像。信號(hào)完整性的核心有兩個(gè)關(guān)鍵問(wèn)題: 1、在拍攝

2016-03-02 14:57:52

信號(hào)完整性與電源完整性分析信號(hào)完整性(SI)和電源完整性(PI)是兩種不同但領(lǐng)域相關(guān)的分析,涉及數(shù)字電路正確操作。在信號(hào)完整性中,重點(diǎn)是確保傳輸?shù)?在接收器中看起來(lái)就像 1(對(duì)0同樣如此)。在電源

2021-11-15 06:31:24

有網(wǎng)友質(zhì)疑大家普遍對(duì)信號(hào)完整性很重視,但對(duì)于電源完整性的重視好像不夠,主要是因?yàn)椋瑢?duì)于低頻應(yīng)用,開(kāi)關(guān)電源的設(shè)計(jì)更多靠的是經(jīng)驗(yàn),或者功能級(jí)仿真來(lái)輔助即可,電源完整性分析好像幫不上大忙,而對(duì)于50M

2019-09-20 14:44:25

附件的產(chǎn)品資料是咱們針對(duì)Altera公司的Cyclone V (GX/SX)、Stratix IV、Stratix V和Arria V 系列產(chǎn)品的集成式電源解決方案,歡迎下載(有分別針對(duì)Altera

2018-12-05 09:14:07

高速信號(hào)的電源完整性分析在電路設(shè)計(jì)中,設(shè)計(jì)好一個(gè)高質(zhì)量的高速PCB板,應(yīng)該從信號(hào)完整性(SI——Signal Integrity)和電源完整性 (PI——Power Integrity )兩個(gè)方面來(lái)

2012-08-02 22:18:58

高速電路信號(hào)完整性分析與設(shè)計(jì)—信號(hào)完整性仿真仿真中有兩類(lèi)信號(hào)可稱(chēng)之為高速信號(hào):高頻率的信號(hào)(>=50M)上升時(shí)間tr很短的信號(hào):信號(hào)上升沿從20%~80%VCC的時(shí)間,一般是ns級(jí)或

2009-09-12 10:31:31

信號(hào)完整性設(shè)計(jì)在產(chǎn)品開(kāi)發(fā)中越來(lái)越受到重視,而信號(hào)完整性的測(cè)試手段種類(lèi)繁多,有頻域,也有時(shí)域的,還有一些綜合性的手段,比如誤碼測(cè)試。這些手段并非任何情況下都適合使用,都存在這樣那樣的局限性,合適選用,可以做到事半功倍,避免走彎路。

2019-08-26 06:32:33

高速數(shù)字硬件電路設(shè)計(jì)中信號(hào)完整性在通常設(shè)計(jì)的影響是什么?高速電路設(shè)計(jì)中信號(hào)完整性面臨的挑戰(zhàn)有哪些?怎么處理?

2021-04-22 06:26:55

® Stratix® IV family ofdevices.How to Contact AlteraFor the most up-to-date information about Altera products, see the following ta

2010-02-25 23:34:02 15

15 針對(duì)Altera Stratix IV EP4SGX360和EP4SGX530器件的電源參考設(shè)計(jì),具體電路如下圖:

2010-12-12 10:37:52 64

64 針對(duì)Altera Stratix IV EP4SGX70和EP4SGX110器件的電源參考設(shè)計(jì),電路圖如下:

2010-12-12 10:43:38 41

41 Altera新Cyclone IV FPGA拓展了Cyclone FPGA系列

Altera拓展其成功的Cyclone FPGA系列并延續(xù)其收發(fā)器技術(shù)領(lǐng)先優(yōu)勢(shì),于今天發(fā)布Cyclone IV FPGA新系列。在移動(dòng)視頻

2009-11-04 08:46:38 1221

1221 Altera開(kāi)始量產(chǎn)發(fā)售業(yè)界首款集成11.3-Gbps收發(fā)器的FPGA

Altera公司宣布,開(kāi)始量產(chǎn)發(fā)售Stratix IV GT EP4S100G2 FPGA,這是業(yè)界首款集成了11.3-Gbps收發(fā)器的FPGA。Stratix IV GT FPGA是目前

2009-11-05 09:47:42 618

618 Altera推出業(yè)界密度最大的Stratix IV EP4SE820 FPGA

Altera宣布,40-nm Stratix IV E FPGA高端密度范圍增大到業(yè)界領(lǐng)先的820K邏輯單元(LE)。Stratix IV EP4SE820 FPGA是業(yè)界同類(lèi)產(chǎn)品中密度最大

2009-11-11 16:50:00 838

838 Altera Stratix IV FPGA助推XDI dbX分析平臺(tái)

Altera公司日前宣布,XtremeData有限公司下一代dbX系列數(shù)據(jù)庫(kù)平臺(tái)設(shè)計(jì)采用了高性能Stratix IV FPGA,該系列專(zhuān)門(mén)用于對(duì)大型數(shù)據(jù)庫(kù)進(jìn)行全

2009-12-04 08:37:02 664

664 Altera推出面向Stratix IV FPGA的最新開(kāi)發(fā)套件

Altera公司近日宣布推出其面向 Stratix IV FPGA 的最新開(kāi)發(fā)套件。Stratix IV E FPGA 開(kāi)發(fā)套件具有業(yè)界最高密度、最高性能的 FPGA。該套

2009-12-09 08:45:26 792

792 Altera Stratix IV FPGA繼續(xù)廣受全球媒體好評(píng)

Altera公司今天宣布,40-nm Stratix® IV FPGA系列最近榮獲電子編輯媒體的多個(gè)獎(jiǎng)項(xiàng)。Stratix IV系列因其在密度、性能和功耗上的優(yōu)

2010-02-24 09:44:20 1198

1198 Stratix IV通過(guò)Interlaken通用性測(cè)試

Altera公司宣布,Stratix IV FPGA通過(guò)Interlaken聯(lián)盟的器件通用性測(cè)試。Altera認(rèn)證了與使用Interlaken協(xié)議的第三方組件的高性能FPGA接口。Stratix IV

2010-03-10 09:26:13 557

557 低功耗Cyclone IV FPGA

Altera公司宣布,開(kāi)始批量發(fā)售Cyclone IV FPGA。公司還宣布開(kāi)始提供基于Cyclone IV GX的收發(fā)器入門(mén)開(kāi)發(fā)套件。Altera的Cyclone IV FPGA設(shè)計(jì)用于無(wú)線、固網(wǎng)、廣播

2010-03-31 10:42:42 1432

1432 Altera公司(Nasdaq: ALTR)宣布,成功實(shí)現(xiàn)28-nm Stratix? V GX FPGA與PLX?技術(shù)公司(Nasdaq: PLXT) ExpressLane? PCI Express? (PCIe?) Gen3的互操作

2011-12-14 09:28:09 677

677 Altera 公司的Cyclone IV 系列 FPGA 包括兩個(gè)系列:Cyclone IV E和Cyclone IV GX,具有低成本、低功耗的FPGA 架構(gòu),6 K 到150 K 的邏輯單元,高達(dá)6.3 Mb 的嵌入式存儲(chǔ)器,小于1.5 W 的總功耗;Cyclone IV GX 器件提供

2012-05-31 09:08:54 8725

8725

本資料是關(guān)于Altera公司 Stratix V GX FPGA開(kāi)發(fā)板電路圖的資料。資料包括開(kāi)發(fā)板原理圖、PCB圖。

2012-08-10 15:55:44 139

139 信號(hào)完整性是指信號(hào)在通過(guò)一定距離的傳輸路徑后在特定接收端口相對(duì)指定發(fā)

送端口信號(hào)的還原程度。在討論信號(hào)完整性設(shè)計(jì)性能時(shí),如指定不同的收發(fā)參考端

口,則對(duì)信號(hào)還原程度會(huì)用不同的指標(biāo)來(lái)描述。

2016-02-19 16:41:51 0

0 Virtex-7 GTH 收發(fā)器與Altera Stratix V GX 收發(fā)器的功能對(duì)比情況

2018-06-06 01:45:00 3572

3572

設(shè)計(jì)人員呼吁提升10G+ 芯片到芯片和背板性能, 依賴(lài)接收機(jī)均衡來(lái)補(bǔ)償信號(hào)失真。觀看視頻, 并排比較 Xilinx? Virtex?-7 FPGA GTH 收發(fā)器 和 Altera Stratix V GX 收發(fā)器的均衡能力。

2018-05-23 15:47:00 3974

3974

必費(fèi)力地去手動(dòng)重新配置背板均衡。

通過(guò)具有自適應(yīng)傳播補(bǔ)償引擎(ADCE)的收發(fā)器,Stratix II GX FPGA:

自動(dòng)重新配置您的背板均衡設(shè)置

保持高速數(shù)據(jù)的最佳信號(hào)完整性

支持可插入多個(gè)卡位的真正通用卡設(shè)計(jì)

2018-06-22 03:56:00 1870

1870 在這一4分鐘的視頻演示中,您將看到Altera新的40-nm FPGA展示其性能達(dá)到1.5-Gbps的LVDS以及具有優(yōu)異信號(hào)完整性的8.5-Gbps收發(fā)器。為您展示的眼圖具有非常低的抖動(dòng),您還

2018-06-22 00:46:00 2693

2693 系列產(chǎn)品怎樣支持155 Mbps至11.3 Gbps的數(shù)據(jù)范圍。

滿(mǎn)足您各種系統(tǒng)需求的最佳性能和功耗配置。

Arria? II GX, Stratix? IV GX, and Stratix IV GT FPGA和HardCopy? IV GX ASIC的應(yīng)用

2018-06-22 01:18:00 2817

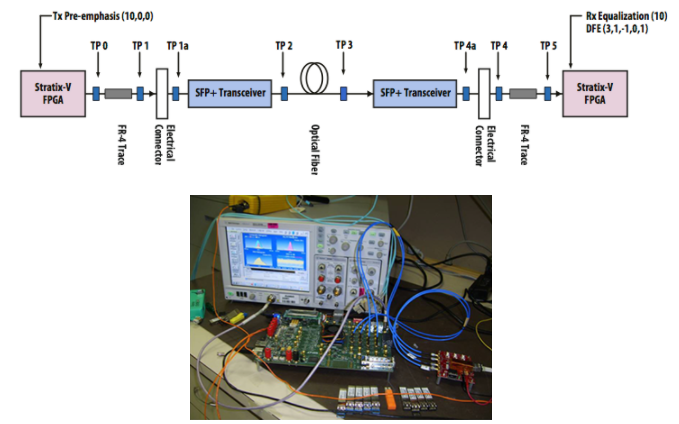

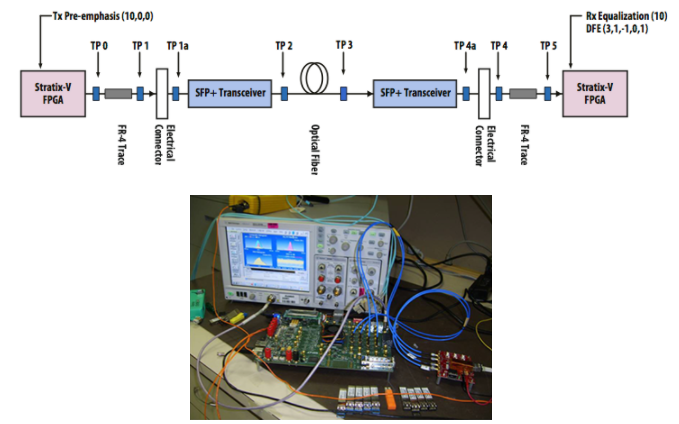

2817 Altera新的Stratix? IV GX版收發(fā)器信號(hào)完整性開(kāi)發(fā)套件支持對(duì)收發(fā)器互操作性和SERDES信號(hào)完整性進(jìn)行全面評(píng)估。

觀看5分鐘視頻,了解:

采用3英寸和40英寸電路板

2018-06-22 10:56:00 1880

1880

板上的Altera? Interlaken解決方案。

了解怎樣使用我們的Stratix IV GT版10G收發(fā)器信號(hào)完整性套件來(lái)評(píng)估信號(hào)完整性,產(chǎn)生并監(jiān)視PRBS碼型。

了解業(yè)界功耗最低的高密度、高性能40-nm FPGA能夠?yàn)槟?00G固網(wǎng)應(yīng)用帶來(lái)什么。

2018-06-22 10:01:00 3757

3757 關(guān)鍵詞:ALTERA , FPGA , Stratix , 密度 , 業(yè)界 Altera宣布,40-nm Stratix IV E FPGA高端密度范圍增大到業(yè)界領(lǐng)先的820K邏輯單元(LE

2018-10-24 20:40:01 419

419 Altera的Arria II GX、Stratix IV GT、Stratix IV GX FPGAs和HardCopy IV GX ASIC采用了通用收發(fā)器技術(shù),由一套通用開(kāi)發(fā)工具為其提供支持

2018-10-25 15:43:50 1393

1393 Altera的Arria II GX、Stratix IV GT、StraTIx IV GX FPGAs和HardCopy IV GX ASIC采用了通用收發(fā)器技術(shù),由一套通用開(kāi)發(fā)工具為其提供支持,幫助系統(tǒng)設(shè)計(jì)人員開(kāi)發(fā)完整的芯片系統(tǒng)(SoC)解決方案。

2018-10-27 08:17:00 3483

3483 Virtex-7 GTH收發(fā)器與Altera Stratix-V GX器件Battle Kits Demo

2018-11-30 06:31:00 2787

2787 個(gè)高速收發(fā)器,以及 1,067 Mbps (533 MHz) DDR3存儲(chǔ)器接口)達(dá)到了前所未有的水平,并具有優(yōu)異的信號(hào)完整性, 非常適合無(wú)線通信,固網(wǎng),軍事,廣播等其他最終市場(chǎng)中的高端數(shù)字應(yīng)用。本文介紹了Stratixreg; IV FPGA主要特性, Stratix IV GT器

2019-02-16 09:51:01 495

495

Altera公司日前宣布,開(kāi)始批量發(fā)售FPGA業(yè)界性能最好、具有背板功能的收發(fā)器。Altera的Stratix? V FPGA是業(yè)界唯一能夠提供14.1 Gbps收發(fā)器帶寬的FPGA,也是唯一

2019-05-27 10:33:26 1467

1467 Altera公司推出其面向Stratix? IV FPGA的最新開(kāi)發(fā)套件。Stratix IV E FPGA 開(kāi)發(fā)套件具有業(yè)界最高密度、最高性能的 FPGA。該套件為用戶(hù)提供了全面的設(shè)計(jì)環(huán)境,其中包括迅速開(kāi)始其高密度原型產(chǎn)品設(shè)計(jì)所需的硬件和軟件。

2020-08-30 08:19:01 826

826 SFP + SR,LR,LRM和Altera Stratix-V FPGA的收發(fā)器。 目的 本報(bào)告演示了Avago 10Gbs以太網(wǎng)SFP +收發(fā)器產(chǎn)品,AFBR-709SMZ(SFP + SR

2021-04-13 15:13:30 3107

3107

具有LVDS輸出的LTM9011 ADC的AN147-Altera Stratix IV FPGA接口

2021-05-09 21:19:53 14

14 wp02-將凌力爾特公司的DDR LVDS ADC與Altera Stratix IV FPGA接口

2021-05-23 11:13:28 1

1 Altera Stratix IV接口的WP02-VHDL

2021-06-07 14:41:22 7

7 信號(hào)完整性與電源完整性的仿真(5V40A開(kāi)關(guān)電源技術(shù)參數(shù))-信號(hào)完整性與電源完整性的仿真分析與設(shè)計(jì)!!!

2021-09-29 12:11:21 89

89

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論