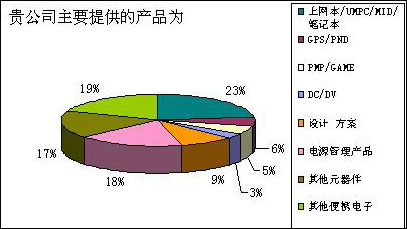

移動電話、便攜式媒體播放器、掌上游戲機和數碼相機等便攜式產品的激增,使得系統設計人員承受著越來越大的壓力。他們必須不停地開發提供擁有新特性和功能的產品,并盡量縮短產品的上市時間。那么,CPLD可微為便攜設計帶來哪些好處呢?在為便攜應用選擇邏輯解決方案時,需要考慮哪些主要設計因素呢?

手持產品得到了廣泛的應用,例如移動電話、便攜式媒體播放器、掌上游戲機和數碼相機等便攜式產品的激增,使得系統設計人員承受著越來越大的壓力。他們必須不停地開發提供擁有新特性和功能的產品,并盡量縮短產品的上市時間。根據市場情報公司iSuppli的預測,核心半導體產品在上述領域的收入可望由2008年的260億美元增長到2012年的300億美元,相當于4%的復合年增長率(核心器件是由iSuppli公司定義的,如ASSP,ASIC和可編程邏輯器件)。

因為要求待機功耗低、電路板尺寸小和成本低,便攜式產品的邏輯功能過去通常是由專用集成電路(ASIC)和專用標準產品(ASSP)來提供,可編程邏輯器件(PLD)的應用相當有限。然而,隨著可編程器件架構的改進、功耗的降低、并采用新的封裝使尺寸變小、成本降低,設計人員開始越來越多地使用PLD,因為與ASIC和ASSP相比,PLD在縮短上市時間和設計靈活性方面具有先天的優勢。

CPLD的應用

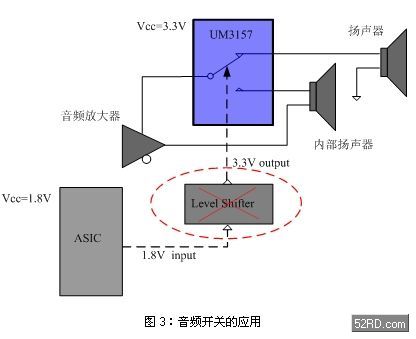

在便攜式產品中,復雜可編程邏輯器件(CPLD)一般用于電源上電時序、電平轉換、時序控制、接口轉換,I/O擴展和分立邏輯功能等。CPLD僅需幾微秒就能上電,這使得它能控制系統中其他器件的上電時序。

在便攜系統中,CPLD也被用來連接不同工作電壓的多個器件。例如,在移動電話中,微控制器需要與工作在不同電壓的外圍器件、定時器和存儲器連接。最新一代的CPLD可以與3.3V~1.5V之間的不同電壓連接,因為它們有一個獨立于輸出電壓(Vccio)的核心電源電壓(Vccint)。CPLD的每個I/O組可配置成與邏輯器件接口相對應的獨立工作電壓。圖1給出了典型便攜系統中的CPLD的功能。

圖1:典型便攜式系統中的CPLD的功能。

通用I/O擴展是CPLD可與微控制器、ASIC或ASSP協同工作的另一個領域,它增加可用I/O的總數目。CPLD額外的一個優點是能與外設接口,還能重復編程。CPLD也可以用做接口轉換,連接諸如I2C、SPI和存儲器的不同接口,以及在便攜系統中實現液晶面板的時序控制。

當為便攜式應用選擇邏輯解決方案時,設計人員應考慮的主要因素包括:上市時間、設計的靈活性、待機功耗,電路板尺寸以及系統集成的選擇。

上市時間和設計靈活性

越來越短的產品生命周期對手持設備設計人員提出了新的挑戰,他們必須提供消費者期望的新產品和新特性。對大批量產品來說,ASIC也許能提供較低的單價,但ASIC的一次性工程費用(NRE)很高,開發時間很長。如果ASIC的功能出錯,或由于行業標準或市場需求發生變化而需要重新開發設計時,就會再次產生非常高的費用,包括工程資源、新的掩膜板和軟件設計工具。此外,從開始實施新的修改方案到流片,再到批量生產,這過程需要很長時間,通常是幾個月到一年。

與ASIC相比,ASSP的NRE較低,因為許多客戶都在使用它們。不過,它們卻限制了設計人員提供產品差異性的能力。

CPLD使設計人員能夠進行隨心所欲地開發、測試和修改設計,而不會產生任何掩膜成本或設計費用。由于CPLD可重復編程的特性,即使設備已經安裝在現場,設計人員依然可以使用軟件設計工具在最后一刻修正錯誤并進行產品升級。因此,設計人員能應對不斷變化的要求和標準,并迅速給市場提供新的差異化產品,而無需做任何設計或重新設計電路板。

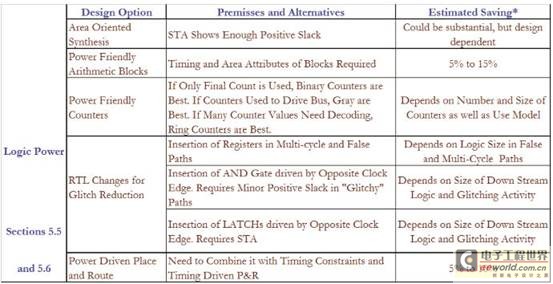

功耗

CPLD的功耗通常分為兩個部分:靜態功耗和動態功耗。靜態功耗是指器件中沒有信號跳變情況下消耗的功率。動態功耗是器件中有信號跳變情況下消耗的功率,且與內部電容,跳轉頻率和跳轉電壓成正比。對便攜式系統而言,待機時間是一個關鍵的設計因素,因為設計人員要盡量減少邏輯電路的靜態功耗,以盡量延長電池充電或更換的時間間隔。如今的低功耗CPLD的最大靜態功耗為10~150uA,主要取決于器件的邏輯密度。

為進一步減少整個系統的功耗,有些CPLD允許用戶有選擇性地關閉未使用的輸入引腳(稱為“輸入選通”),包括使能I/O引腳和輸入緩沖器之間的復用器,及其CPLD內的相關電路(如圖2所示)。激活使能信號時,所有的輸入被隔離或處于關閉狀態,從而使其中任何輸入變化都不會引起內部引腳的變化。因此,即使I/O引腳的輸入在變化,也不會影響器件的內部動態功耗。

舉個例子,在萊迪思半導體的ispMACH 4000ZE CPLD中,一個塊內的所有I/O引腳都共享一個PowerGuard(針對輸入選通,Lattice給予此特性的名稱)使能信號,稱為塊輸入使能(BIE)信號。BIE可以用宏單元邏輯在內部產生,也可通過用戶I/O從外部源或輸入引腳的方式來產生。為增加設計的靈活性,器件有多少塊就有多少塊輸入使能信號,數目從2至16不等。可以把兩個或更多的使能信號組合在一起,構成一個用戶使能信號。

以6宏單元的ispMACH406?ZE器件為例,除了兩個激活的輸入,其余的都使用了PowerGuard,使動態電流減少了99%。如圖3所示,動態ICC從2.9毫安減少至26微安。

有些CPLD可以通過軟件對每個引腳單獨控制,使其為“高”或者“低”,從而進一步減少I/O電流和系統總功率。電壓典型值為250mV~500mV的輸入滯后電路通常用來實現降噪和減緩輸入信號的變化,以提高信號的完整性。

由于主系統電源的典型值為1.8V,大多數便攜式系統都需要LVCMOS接口。這些系統要求能與工作在TTL或LVCMOS標準的其他器件相連接。目前所有CPLD都有獨立的核心電壓和I/O電壓,其中I/O電壓能支持1.5、1.8、2.5和3.3V LVCMOS電平。諸如ispMACH 4000ZE這樣的CPLD還能夠與傳統的5V電壓LVCMOS器件接口。

電路板尺寸

隨著便攜式產品的體積不斷縮小,設計人員必須在非常小的電路板上集成更多的邏輯功能。現在的CPLD可以采用超小型封裝,包括芯片級BGA(csBGA,0.5毫米間距),只需25平方毫米或49平方毫米的電路板面積。而傳統的薄型四方扁平封裝(TQFP封裝,0.8毫米間距)封裝需要100平方毫米或196平方毫米的電路板面積。

當電路板空間有限時,采用這些封裝非常理想。與傳統的TQFP封裝相比,這些封裝使電路板面積減少了75%以上,從而簡化了電路板布線并降低整個系統成本。圖4為ispMACH 4000ZE csBGA封裝示意圖。BGA封裝的熱電阻值(典型值為10度/瓦)比TQFP或PQFP封裝更低(典型值20度/瓦至40度/瓦)對于降低功耗和提高器件的可靠性,它們是更好的選擇。

系統集成

通過減少電路板上的元件,可使系統總成本降低。當使用多個電路板元件時,制造成本,包括裝配,包裝和運輸都會增加總的電路板成本。此外,電路板上的元件越多,故障率越高,這是由于焊球之間的殘留物和其它隨機故障所致。

減少元件也可以降低功耗。如今,低功耗CPLD用來整合外部時鐘源和標準分立邏輯器件,如7400系列邏輯器件。單個可編程邏輯器件可用于集成多個分立的74xxx器件,還能實現其它功能,如I/O擴展,電平轉換和時序控制。

針對系統集成,除了器件上邏輯密度為32~256的宏單元之外,ispMACH 4000ZE CPLD還具有片上用戶振蕩器和針對上電時序的定時器、鍵盤掃描和顯示控制器功能。振蕩器輸出的典型頻率為5MHz,而且還可進一步分頻為128(7位)、1024(10位)或1048576(20位),以工作在更低的頻率下。使用CPLD內的集成振蕩器的好處是能降低電路板成本、簡化庫存管理和使產品過期風險最小化,這些因素通常與使用分立元件有關。下表對可用于便攜式系統的最新一代CPLD系列進行了比較。

針對便攜式系統的CPLD系列的比較。

本文小結

CPLD正在被越來越廣泛地應用于便攜式產品,具有零待機功耗選擇、節省面積的超小型封裝和增強的系統集成功能等優點。與過去使用的ASIC和ASSP相比,CPLD為設計人員提供了一個有著顯著優勢的低成本系統解決方案。此外,CPLD使得設計人員能在更短的時間內根據消費者的需求增加新的特性和功能,使產品更快上市,而且風險更小。

電子發燒友App

電子發燒友App

評論