基于AD9640的無線接收機設計

在無線接收機射頻前端硬件的實際制作中,中頻頻率的選擇、帶通濾波器的中心頻率與3dB帶寬、外部無源器件的使用等設計考慮,都需要隨著不同的系統應用而仔細的規劃與調整,以便在適當的成本下達到規定的性能。本文以認知抗干擾為設計目標,主要討論了接收機鏈路的核心器件之一—高性能的ADC,敘述它們如何滿足對高性能的需求。此外,接收機系統的設計還包括器件的選擇和設計,整體排版布線以及調試過程等步驟。

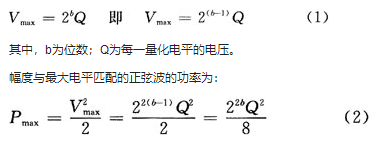

ADC設計

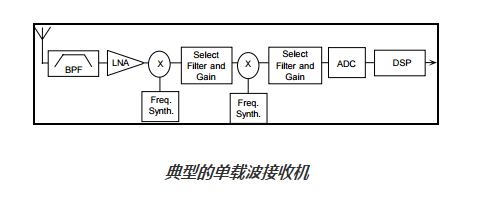

天線接收到的射頻信號必須經過A/D數字化,以便后面的數字處理芯片進行數字信號處理[1]。ADC影響接收機體系的功耗、工作頻率動態范圍、接收帶寬和總體成本,其性能更是能夠影響接收機結構的設計。理想情況下,在接收機的鏈路天線后直接進行數據轉換,ADC對射頻信號直接進行抽樣,這樣很大程度上繞過了模擬器件。而本文接收機體系結構的一個重要特點是將ADC盡量靠近射頻前端,在較高的中頻直接進行數字化,因此A/D設計是接收機設計的核心之一。

選定最優采樣頻率

如果對采樣輸出信號進行濾波的低通濾波器可以做到矩形系數為1,在無混疊的采樣率范圍內選定任何一個頻率都是可以的(不考慮采樣時鐘的抖動)。但是實際上,這樣的濾波器是做不出來的,即使是矩形系數接近于1的低通濾波器也很難實現。如果后續的低通濾波器在過渡帶里面沒有頻譜的平移轉換,那么,即使矩形系數大一些也不會改變原信號的頻譜結構,這也就意味著平移頻譜之間的間隔應該越大越好。對于無混疊的采樣率來說,并不是頻率越高間隔越大,頻譜間隔最大的無混疊采樣率在降低后續低通濾波器的設計難度上是最優的。

本文首先討論無混疊采樣率與平移的頻譜間隔的關系,然后結合方案選擇一個最優的采樣頻率。

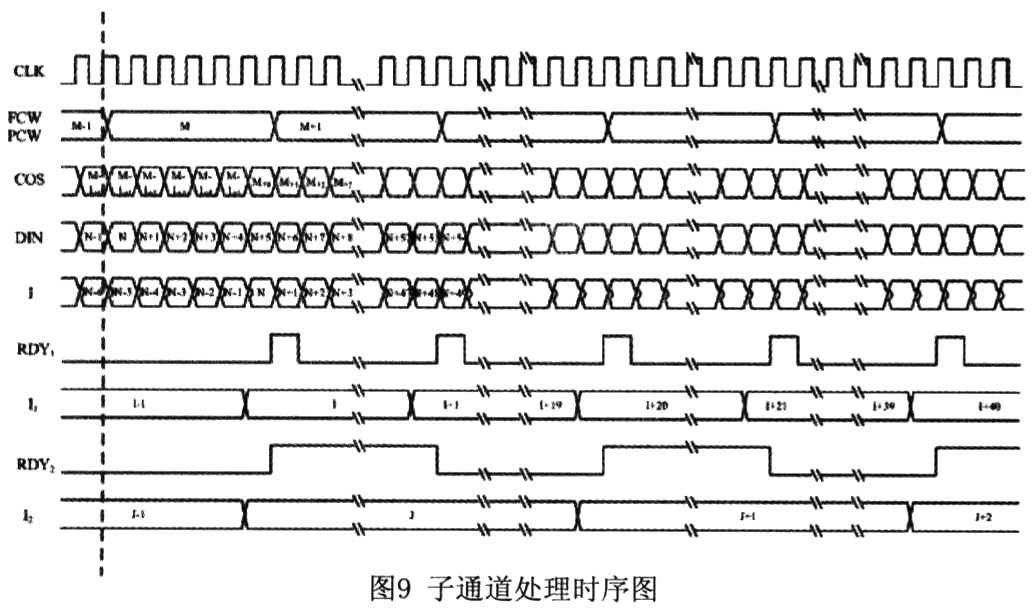

對圖1中虛線所示的頻譜塊,其左間距表示為:

-fH+(m-1)fs-[fH-(m-1)fs]=2(m-1)fs-2fH (m=1, 2, 3…)

右間距表示為:

fL-(-fL+mfs)=-mfs+2fL

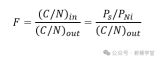

使頻譜間隔最大條件是頻譜塊的左間距等于右間距:

2mfs-2fH=-mfs+2fL

即

![]()

比如天線接收的信號是75MHz中頻,帶寬1MHz的信號,所以使頻譜間隔最大的采樣頻率為:fs=133.3333、66.6667、33.3333、26.6667MHz…(m=1, 2, 3, 4…)。注意,上面所指的頻譜間隔最大是對于相應的m而言的,對于不同的m來說,間隔的絕對值隨m的增大而減小。

由于超過100MHz的高精度A/D器件價格昂貴,我們選擇m=2,這時的無失真采樣頻率fs的范圍是50.3333MHz≤fs≤75.5100MHz。同時考慮到ADC采樣頻率與中頻濾波器的帶寬之間必須滿足一定的關系:

fs≥B+B×w

其中w是該中頻帶通濾波器的矩形系數,本文設為:w=3。此時,ADC采樣通帶不會發生混疊,但過渡帶將會混疊,直到ADC采樣頻率增大到上式右邊的兩倍后,過渡帶才不會混疊。從本質上看,還是會“混疊”的,但此時“混疊”的信號已被衰減得很微弱,比如衰減到比通帶信號小70dB以上。

最后考慮到后續DDC器件進行速率轉換后輸出速率為8MHz(由于ADC和后續算法處理要求),采樣得到的信號速率最好是2的整數倍,同時又考慮到采樣時對信號頻段確定和控制的方便,最優的采樣頻率選定為64MHz。這個采樣頻率產生的頻譜間隔對后續濾波器的設計也是足夠的。

器件選擇

綜合采樣精度和速率的要求對ADC進行選擇:16位的ADC可以達到大約96dB的信噪比,但是精度達到16位同時速度超過60 MHz 的ADC價格非常昂貴且不易購買到;14位的ADC可以達到大約84dB的信噪比,也可以滿足要求,還可以買到速度更快的產品。本設計選擇14位雙通道A/D器件AD9640[2]進行采樣。其主要性能為:可選最大采樣速率80、105、125、150MSPS;采樣精度14位;無雜散動態范圍85dB@125MSPS;信噪比71.8dB@ 125MSPS;低功耗750mW@125MSPS。

其中采樣速率的改變可通過改變輸入時鐘來實現,從而可實現在不改變硬件的情況下通過軟件來擴展。

設計高性能ADC之前的“前端”或輸入配置,是獲取所需系統性能的關鍵所在。整個設計的優化[3]取決于許多因素,其中包括應用的特點、系統劃分,以及ADC 的構架等。許多放大器都十分適合用于高速ADC 的前端電路。ADA4937 能被用于150MHz以下的頻率;由于它能處理很大的輸出共模電壓范圍,因此它的主要優勢是應用于ADC 的直流耦合應用中。對于窄帶或諧振應用,使濾波器與放大器的輸出阻抗匹配,來消除ADC 的輸入電容。通常使用一個多極點濾波器來消除感興趣頻率范圍外的寬帶噪聲。

接收機PCB設計

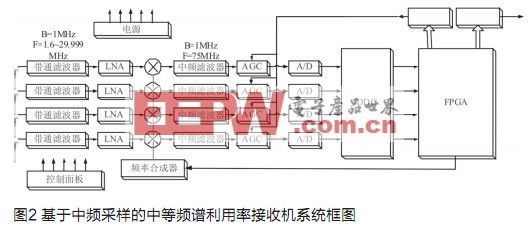

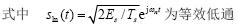

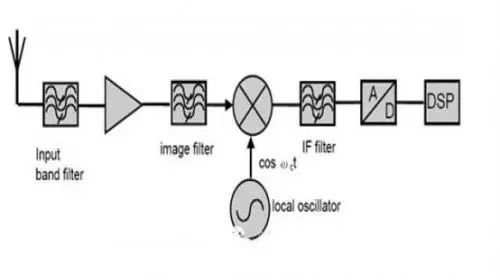

基于圖2的接收機框圖(圖中DDC使用四通道數字下變頻器AD6635)和PCB設計的基本要求,可以提出本文接收機PCB排版布線的總體要求如下:

● 所有電源在PCB板頂層或/和底層應留出散熱區[4];

● 所有盒子輸入輸出接口位于PCB板的底層;

● PCB板頂層和底層大面積敷銅并接地;

● 電源及其附屬元件靠近,獨立驅動電源平面,電源平面為電源分配網絡。元器件供電從電源平面獲取,根據需要在靠近管腳處濾波;

● 所有電源線進入盒子安裝“穿心電容”;

● 放大器直接接地,同時應該屏蔽所有高增益放大器以防止它們產生振蕩。

ADC布線

在PCB原理圖中,模擬地的網絡標號為AGND,數字地的網絡標號為GND。在將A/D轉換器的模擬地和數字地引腳連接在一起時,大多數的A/D轉換器是將AGND和DGND引腳通過最短的引線連接到同一個低阻抗的地上,任何與DGND連接的外部阻抗都會通過寄生電容將更多的數字噪聲耦合到芯片內部的模擬電路上。從而需要把A/D轉換器的AGND和DGND引腳都連接到模擬地上,但這種方法會產生諸如數字信號去耦電容的接地端應該接到模擬地還是數字地的問題。

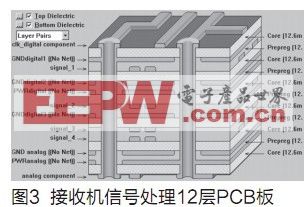

本設計的多通道接收機中A/D轉換器較多,如果在每一個A/D轉換器的下面都將模擬地和數字地連接在一起,則產生多點相連,模擬地和數字地之間的隔離就毫無意義。而如果不這樣連接,就又違反了廠商的要求。因此,最好的辦法是開始時就用統一地,將統一的地分為模擬部分和數字部分。這樣的布局布線既滿足了ADC器件廠商對模擬地和數字地引腳低阻抗連接的要求,同時又不會形成環路天線或偶極天線而產生電磁兼容(EMC)問題。本文中AD9640的PCB制版安排見圖3。

接收機排版布線

本設計中,接收機布線堅持2W原則:布線寬度為W,線間距不小于2W。PCB電路板分為模擬層和數字層兩個部分,共12層,制版安排見圖2,布線安排設計如下。

(1)模/數布線和元件排版分離。高速信號位于優質布線層clk-digital component和signal_1,高速信號線同低速信號線盡量遠離,重要的低速信號線位于低速信號層signal_2 和signal_3。首先,保證關鍵高速時鐘和信號線布放于層clk-digital component和signal_1;然后保證關鍵低速信號線位于層signal_2 和signal_3;其次,低速信號線進入高速布線層clk-digital component時應該遠離高速信號線(尤其是時鐘),高速信號線進入低速布線層signal_2 和signal_3應該遠離低速信號線;最后,上述原則無法實施時應該增加布線層。

(2)PCB板下三層為模擬電路,上七層為數字電路;層clk-digital component布線64MHz時鐘;層signal_1布線64MHz數字信號,包括AD9640采樣64MHz高速數字信號;層signal_2 和signal_3布線小于64MHz的所有其它數字信號;將數字地GNDdigital2用多個過孔連接到GNDdigital1上,GNDdigital2僅僅為隔離模數兩個系統,保護模擬信號免受數字干擾。GNDdigital1作為電源+5V的數字地;GNDdigital2作為+1.8V、+2.5V、+3.3V的數字地。

(3)FPGA、穩壓片等所有核心元件位于頂層clk-digital component。

(4)各層敷銅接地方法:

● 層clk-digital component、signal_1、signal_2 、signal_3的大面積敷銅,并通過多個過孔連接到GNDdigital1;

● 層analog component的大面積敷銅,并通過多個過孔連接到GND analog。

(5)電源布線:電源線根據使用區域大面積填充,形成分割的電源平面。模擬電源平面PWRanalog分割為3.3V和5V兩個部分,數字電源平面PWRdigital分割為1.8V、2.5V、3.3V、5V四個部分。

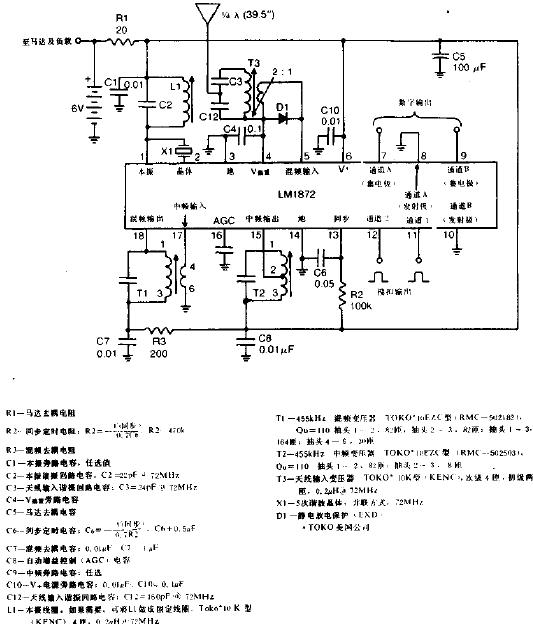

實物制造及測試

圖4示出所設計的接收機實物圖,將其放置在一定的溫度、濕度和振動壓力之下測試以檢查任何設計或工作的缺陷。

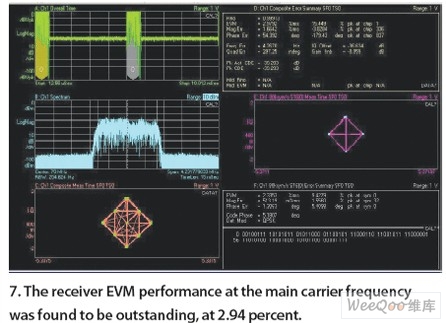

在本文設計接收機的調試過程中,用到儀器為:數字接口(Agilent N5102A),矢量信號源(Agilent E8267D),微波矢量分析儀(Agilent 89650A),示波器(Tektronix TDS 3032B),矢量信號分析儀(Agilent 89611A),邏輯分析儀(Agilent 16900A)。上述儀器,對接收機測試的連接圖如圖5所示。

矢量信號源產生接收機需要的各種調制信號輸入到射頻前端,經過測試可得,接收機體積小,性能穩定,且便于調試,實際ADC采樣速率為63.488MHz;進入FPGA數據速率為7.936MHz;FPGA處理主時鐘速率為63.488MHz; 2~30MHz帶寬、-113dBm~-36dBm的通信信號被接收的平均誤碼率為:Pe<10-5。因此,本接收機射頻前端抗干擾性強,電磁兼容性好,滿足設計要求。

電子發燒友App

電子發燒友App

評論