如何避免在DSP系統中出現噪聲和EMI問題

在任何高速數字電路設計中,處理噪聲和電磁干擾(EMI)都是一個必然的挑戰。處理音視頻和通信信號的數字信號處理(DSP)系統特別容易遭受這些干擾,設計時應該及早搞清楚潛在的噪聲和干擾源,并及早采取措施將這些干擾降到最小。良好的規劃將減少調試階段中的大量時間和工作的反復,從而會節省總的設計時間和成本。

如今,最快的DSP的內部時鐘速率高達數千兆赫,而發射和接收信號的頻率高達幾百兆赫。這些高速開關信號將會產生大量的噪聲和干擾,將影響系統性能并產生電平很高的EMI。而DSP系統也變得更加復雜,比如具有音視頻接口、LCD和無線通信功能,以太網和USB控制器、電源、振蕩器、驅動控制以及其他各種電路,所有這些都將產生噪聲,也都會受到相鄰元器件的影響。音視頻系統中特別容易產生這些問題,因為噪聲會引起敏感的模擬性能的下降,而對于離散的數據來說卻不明顯。

至關重要的是從設計的一開始就著手解決噪聲和干擾問題。許多設計第一次都沒有通過聯邦通信委員會(FCC)的電磁兼容測試。如果在早期的設計中在低噪聲和低干擾設計方法上花費一些時間,就會減少后續階段的重新設計成本和產品的上市時間的延遲。因此,從設計的一開始,開發工程師就應該著眼于:

- 選用在動態負載條件下具有低開關噪聲的電源;

- 將高速信號線間的串擾降到最小;

- 高頻和低頻退耦;

- 具有最小傳輸線效應的優良的信號完整性;

如果實現了這些目標,開發工程師就能有效避免噪聲和EMI方面的缺陷。

噪聲的影響及控制

對于高速DSP而言,降低噪聲是最重要的設計準則之一。來自任何噪聲源的過大的噪聲,都會導致隨機邏輯和鎖相環(PLL)失效,從而降低可靠性。還會導致影響FCC認證測試的輻射干擾。此外,調試一個噪聲很大的系統是極端困難的;因此,要消除噪聲-如果能夠徹底消除的話-則要求在電路板設計中花費大量的功夫。

在音視頻系統中,即便是比較小的干擾,也會對最終產品的性能產生顯著的影響。例如,音頻捕獲和回放系統中,性能將取決于所用的音頻編解碼的質量,電源的噪聲,PCB布線質量,以及相鄰電路間的串擾大小等。而且,采樣時鐘的穩定度也要求非常高,以避免出現不希望的雜音,如在回放和捕獲過程中的“砰砰”聲和“咔嚓”聲。

在視頻系統中,主要的挑戰是消除色彩失真,60Hz“嗡嗡”聲以及音頻敲擊聲。這些對高質量視頻的系統都是有害的,例如安全監控方面的應用。實際上,上述這些問題通常都與視頻電路板的設計不良有關。具體包括:電源噪聲傳到視頻的DAC輸出上;音頻回放引起電源的瞬變;音頻信號耦合到了高阻抗的視頻電路的信號線上。

這些典型的視頻問題源包括:同步和像素時鐘的過沖和欠沖;影響色彩的編解碼和像素時鐘的抖動;缺少端接電阻的圖像失真;音視頻隔離較差引起的閃爍。

音視頻應用容易產生的噪聲干擾問題,對于所有要求具有很低誤碼率的通信系統來說也是常見的。在通信系統中,輻射不僅僅產生EMI問題,還會阻塞其他的通信信道,從而引起虛假的信道檢測。采用適當的電路板設計技術、屏蔽技術以及RF和混合的模擬/數字信號的隔離等技術,就可以解決這些挑戰。

在高速DSP系統中有許多潛在的開關噪聲源,包括:信號線間的串擾;傳輸線效應引起的反射;退耦電容不合適所引起的電壓降低;高電感的電源線,振蕩器和鎖相環電路;開關電源;線形調整器不穩定性所引起的大容性負載;磁盤驅動器。

這些問題由電耦合和磁耦合共同產生。電耦合的產生是由于相鄰信號和電路的寄生電容和互感所引起,而磁耦合的形成是由于相鄰的信號線形成輻射天線所導致。如果輻射干擾足夠強的話,將會導致能夠摧毀其他系統的EMI問題。

當高速DSP系統中的噪聲無法根本消除時,則應該將其減到最小。電子元器件內部都有噪聲,故仔細地選擇器件特性,并選用適當的器件是至關重要的。除了器件的正確選擇外,還有兩種通用的技術,即PCB布線和回路退耦可以幫助控制系統噪聲。一個優秀的PCB布線將降低噪聲通道產生的可能性。另外,還減小了能夠傳播到印制線和電流回路上的輻射,退耦避免相鄰電路產生的噪聲影響。最好的方法是從源頭上濾除噪聲,不過也可以使相鄰的電路對噪聲不敏感或者消除噪聲的耦合通道。

現在我們討論幾種可以解決由系統噪聲和EMI引起的許多常見問題的技術。

保持電流回路最短

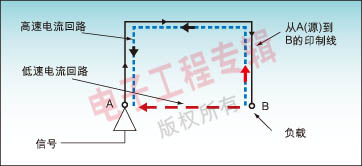

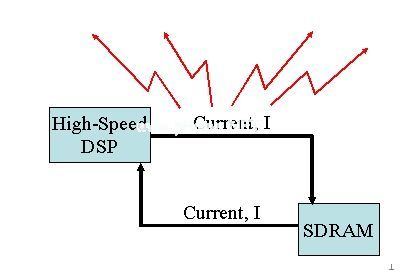

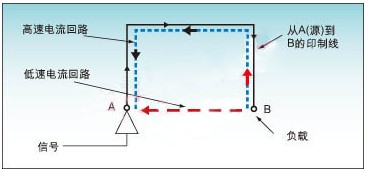

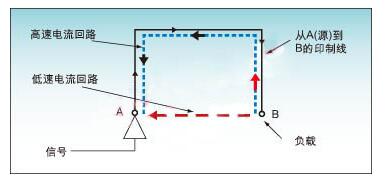

低速信號電流沿阻抗最小,即最短的路徑返回源端。而高速信號則是沿電感最小的路徑返回:這樣的最小的回路面積位于信號線的下面,如圖1所示。

圖1:高速信號與低速信號電流的比較。

因此,高速信號設計的目標之一就是為信號電流提供最小的電感回路。這可以利用電源平面和地平面來實現。電源平面通過形成自然的高頻退耦電容將寄生電感降到最小。而地平面形成一個屏蔽面,即眾所周知的鏡像平面,能夠提供最短的電流回路。

一種有效的PCB布線方法就是將電源平面和地平面靠在一起。這樣形成了高平板電容和低阻抗,有利于降低噪聲和輻射。為了屏蔽,最好的選擇是:關鍵信號最好布到靠近地平面一邊,而其余的則應靠近電源平面一側。

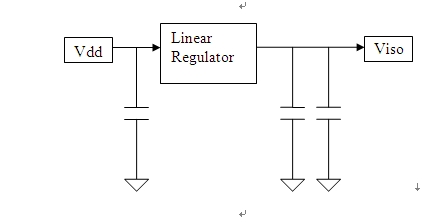

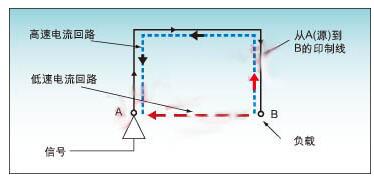

在高速視頻系統中,保持回路短的目的意味著視頻地不能被隔離。而必須被隔離的音頻地,絕不能在數據輸入點處短接到數字地上,如圖2所示。

圖2:音頻地隔離。

電源隔離和鎖相環

如何實現最佳供電是控制噪聲和輻射的最大挑戰。動態負載開關環境很復雜,包括的因素有:進入和退出低功率模式;由總線競用和電容器充電所引起的很大的瞬態電流;由于退耦和布線不合理引起較大的電壓下降;振蕩器使線性調節器輸出過載。

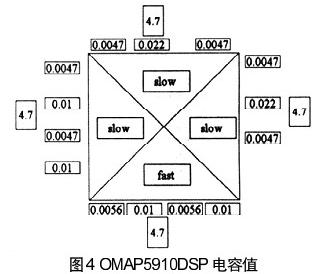

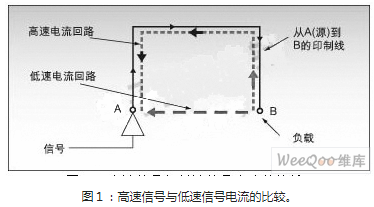

圖3給出了一個設計電流回路的實例,其中利用了電源線退耦。該例中的退耦電容盡可能靠近DSP。如果沒有退耦,動態電流回路將較大,這將加大電源電壓的降幅,從而產生電磁輻射。

圖3:電源退耦。

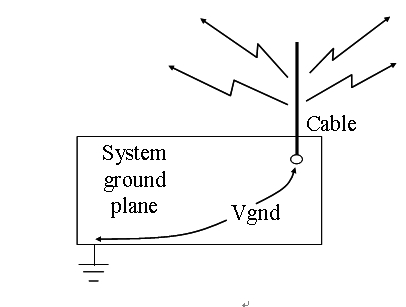

為PLL供電時,電源隔離是非常重要的,因為PLL對噪聲非常敏感,并且對于穩定系統來說,要求抖動非常低。你還需要選擇模擬的還是數字的PLL,模擬PLL對噪聲的敏感度比數字PLL要低。

圖4:PLL電源隔離。

如圖4所示的具有低截至頻率的∏型濾波器經常被用來將PLL與系統中的其他高速電路隔離開。一個較好的辦法是利用一個低壓差(LDO)電壓調整器來獨立產生PLL的電源電壓,如圖5所示。該方法雖增加了成本,但確保了低噪聲和優異的PLL性能。

圖5:利用LDO實現PLL電源的隔離。

串擾及傳輸線效應

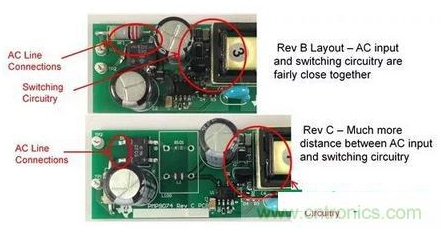

信號間的干擾,即串擾,可以通過電磁輻射在印制線間傳播。這也可能由電源和地平面上的無用信號以電氣的形式產生。串擾與印制線間距的平方成反比。因此,為了將串擾減到最小,單端信號的布線間距應至少是印制線寬度的2倍。對于像以太網和USB這類的差分信號,印制線間距需要與印制線寬度相同,目的是能夠與差分阻抗相匹配。關鍵信號可以用地和電源平面進行屏蔽,或者在改板時增加與信號并行的地線。

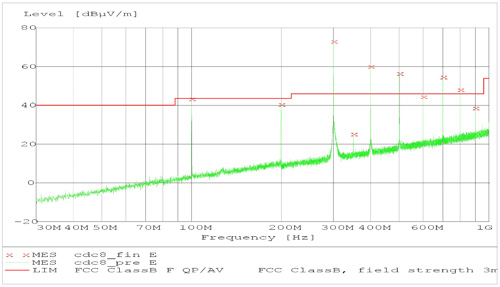

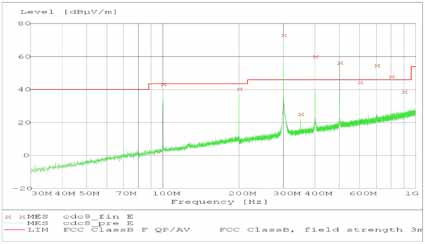

有些信號還產生引起串擾的高頻諧波。由于輻射的能量正比于信號的上升和下降時間,較慢的上升或下降時間引起的干擾將較小。圖6顯示出視頻干擾的實例,這些干擾可能由內部時鐘的輻射所引起。在北美地區第二頻道中,18.432MHz的音頻時鐘的三次諧波,將產生如圖中左側所示的干擾。通過在音頻時鐘印制線上增加一個串聯電阻來放慢時鐘的上升和下降時間,減小了干擾,其結果如圖6中的右側所示。不過,設計師需要了解定時裕度,以便于將上升和下降沿降低到系統所允許的限度內。

圖6:解決音視頻串擾。

與串擾相關的是傳輸線效應,這種效應在高速印制線變成產生輻射干擾的發射器時產生。通常,當信號的上升時間小于傳播延遲的2倍時,印制線才發射信號。這就暗示出了一個經驗,即為了減小傳播延遲,印制線的長度應盡可能短。另一個是合理的信號端接將減慢信號的上升時間,從而將反射引起的過沖和欠沖減到最小。圖7顯示了如何利用并行端接來校正電平并將傳輸線效應減到最小。

圖7:利用端接將傳輸線效應減到最小。

設計師可能會質疑,既然芯片內部已經集成了電阻,在外部端接負載電阻是否還有其重要性。實際上,除了控制傳輸線效應外,外部電阻還可以實現信號完整性的精密調整。DSP無法與電路板阻抗完全匹配,因此端接負載可以減小源電流,以及上升和下降時間。

與外部端接負載電阻一樣,外部的上拉和下拉電阻也是重要的。對于無連接的引腳來說,雖然內部的上拉和下拉電阻是足夠的,但高速開關噪聲能夠傳過來,并會誤觸發連接端上的內部邏輯。

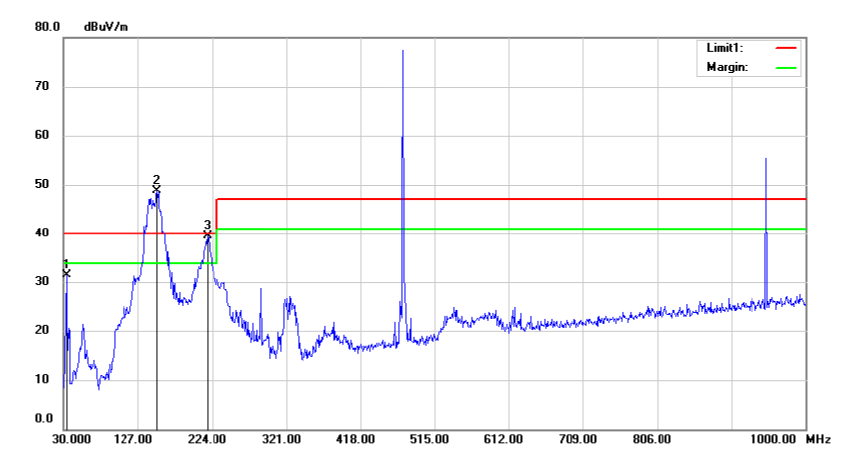

控制EMI

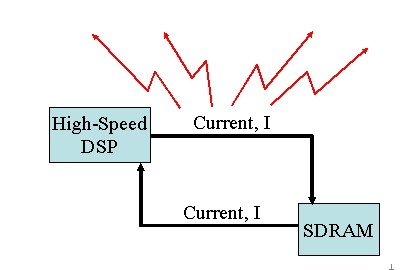

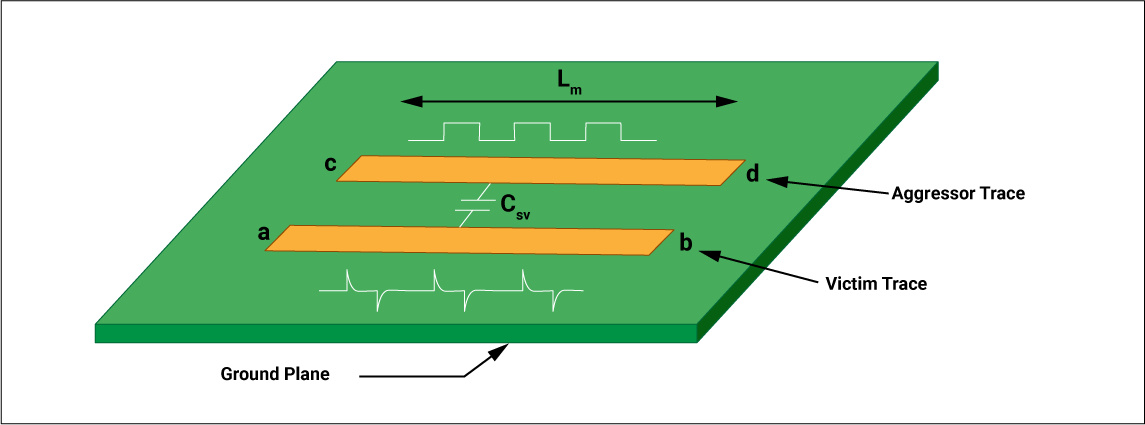

能夠輻射到系統外的輻射被認為是EMI,這可能使設計無法通過FCC認證。有兩種可能的輻射:一種是發射源是一條直線型的信號印制線,或者電纜的共模輻射,另一種是其信號和回路構成一個大電流環路的差分模式輻射。共模輻射隨著頻率的升高而降低,而差分模式輻射則隨著頻率的升高而增強,直到其飽和點。這兩種模式的輻射如圖8和9所示。

圖8:共模輻射。

圖9:差模輻射。

如何處理EMI取決于輻射源。對于共模輻射,當EMI來自外部電纜時(例如圖8所示的情況),可以在電纜上加一個扼流圈。如果導致EMI的是內部傳輸線,則通常用端接負載的方式,不過在信號印制線間加入一條地線也有助于減小輻射。另一種可能的方案是將信號的印制線長度減短至小于信號波長(或信號頻率的倒數)的1/20。例如,為了避免傳輸輻射,500MHz的印制線應該短于1.18英寸。

對于差分模式輻射,所輻射的能量是電流、環路面積和頻率的函數。減小輻射的方法包括:端接負載來降低源電流,用合適的電流通道來提供可以減小回路面積的回路,或者降低頻率。

在計算退耦電阻時,還應考慮動態電流。高速電流可能隨時變化,這種瞬變也會引起輻射。此外,改變電容器的值時要防止自諧振限制頻率范圍。PCB分層是一個好方案,因為電源層對高頻形成自然的退耦,而地層則提供最短的回路。把高速信號隔離起來,并使其遠離其他信號。如果可能的話,不要把地層隔開。盡管噪聲和輻射是由系統設計中的復雜的無用功能引起的,但通過上述的一些簡單方法還是可以控制的。

本文小結

高速的DSP視頻系統中有許多潛在的噪聲和輻射源,它們可以擾亂系統的工作,或者使設計通不過FCC的認證。所幸的是,對噪聲和輻射的規劃和掌握可以幫助系統設計師將這些問題減到最小。早期的努力將節省大量的調試工作和后期的麻煩。PCB布局和回路退耦是設計師可以限制系統噪聲和EMI的兩種常用技術。具備了這些技術,DSP視頻設計師就能有效地解決系統的噪聲和輻射。

電子發燒友App

電子發燒友App

評論