。靜態時序分析工具很好地解決了這兩個問題。它不需要激勵向量,可以報出芯片中所有的時序違例,并且速度很快。 通過靜態時序分析,可以檢查設計中的關鍵路徑分布;檢查電路中的路徑延時是否會導致setup違例;檢查電路中是否由

2020-11-25 11:03:09 8918

8918

在fpga工程中加入時序約束的目的: 1、給quartusii 提出時序要求; 2、quartusii 在布局布線時會盡量優先去滿足給出的時序要求; 3、STA靜態時序分析工具根據你提出的約束去判斷

2020-11-25 11:39:35 5320

5320

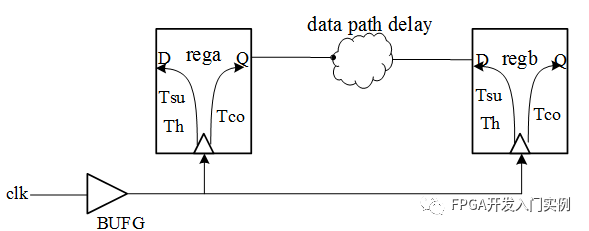

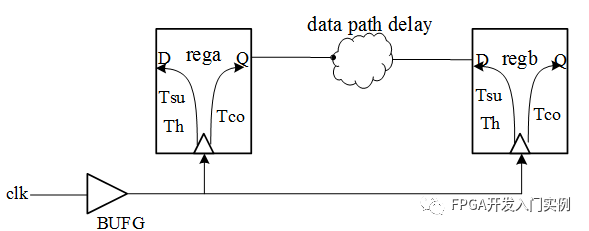

靜態時序分析包括建立時間分析和保持時間分析。建立時間設置不正確可以通過降低芯片工作頻率解決,保持時間設置不正確芯片無法正常工作。

2022-08-22 10:38:24 3289

3289 同步電路設計中,時序是一個主要的考慮因素,它影響了電路的性能和功能。為了驗證電路是否能在最壞情況下滿足時序要求,我們需要進行靜態時序分析,即不依賴于測試向量和動態仿真,而只根據每個邏輯門的最大延遲來檢查所有可能的時序違規路徑。

2023-06-28 09:35:37 490

490

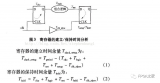

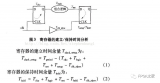

下圖是一個經典時序分析模型,無論寄存器A與寄存器B是否在同一個芯片中,下列概念均適用。

2023-07-03 15:37:08 656

656

互通性測試,向商用邁出了堅實的一步。 然而對于手機芯片企業來說,僅僅克服多頻段兼容和多模兼容還遠遠不夠,一顆5G基帶芯片的研發還需要攻克包括系統散熱、架構和高速率低時延等在內的多個難關。5G終端的處理

2019-09-17 09:05:06

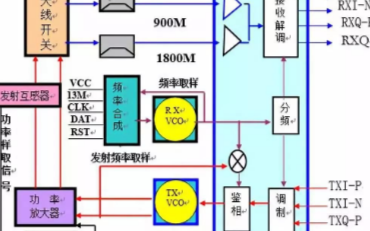

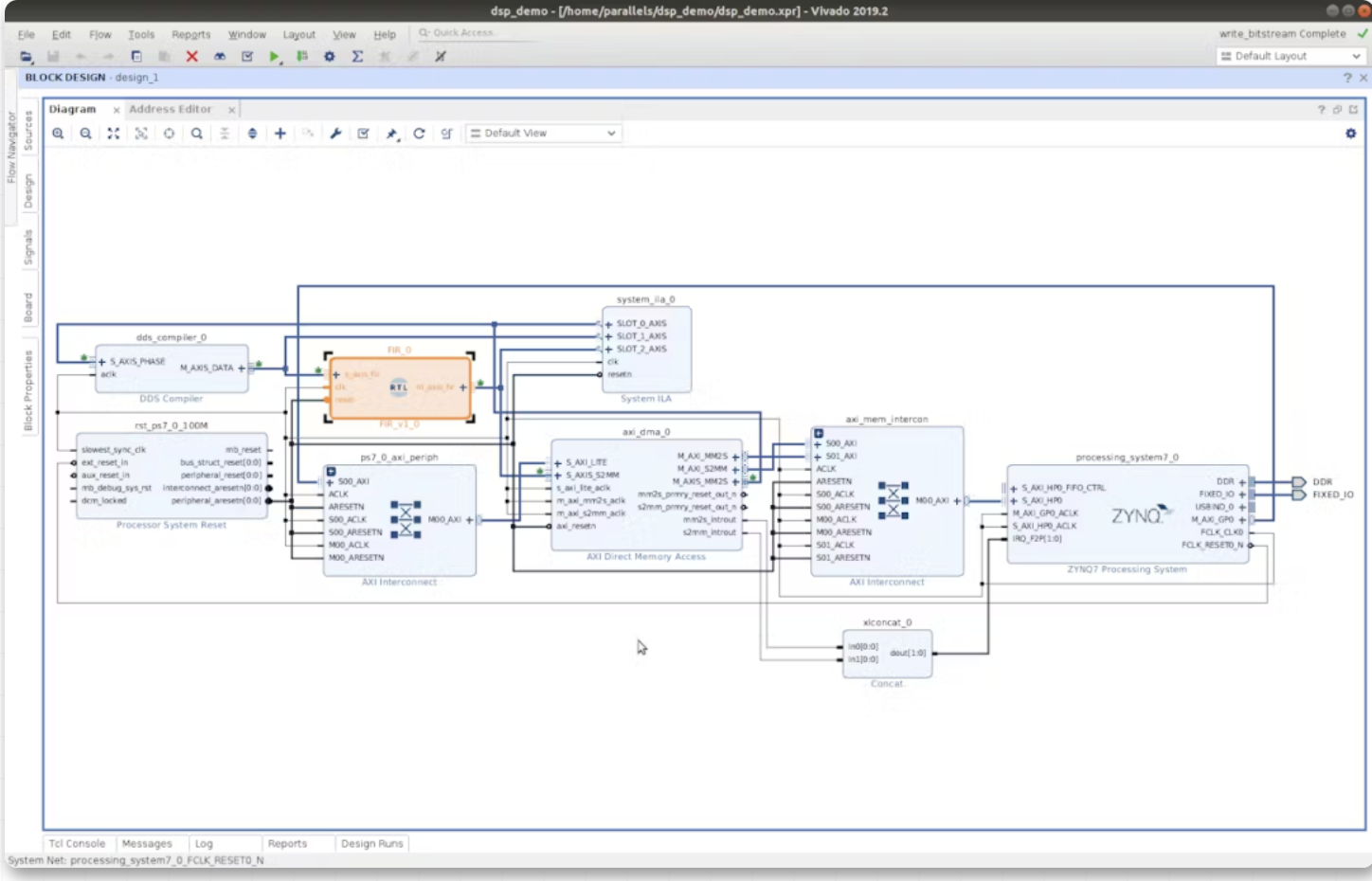

AD6900是一款低功耗無線數字基帶芯片,它的高級電源管理系統滿足了GSM、GPRS和EDGE終端的嚴格要求,還支持對計算量要求很大的多媒體功能。集成了BlackfinDSP處理

2021-04-13 07:30:36

數字基帶信號處理實驗 一、實驗目的 1、熟悉該系統的時鐘信號與各種定時信號的產生方法。 &

2009-10-11 08:54:51

數字芯片設計流程:功能驗證之前與工藝庫沒多大聯系,驗證芯片設計的功能是否正確,針對抽象的代碼進行功能驗證理想值。一致性驗證確保生成的網表和代碼設計功能一致;DFT之后是數字后端。靜態時序分析,從邏輯

2021-11-10 06:14:28

芯片要求如圖片中的時序,通過數組生成如圖數字波形后,芯片不能輸出,數字時鐘為默認的1k左右,感覺這個地方可能有問題,請大神指點

2016-05-06 11:51:28

數字信號時序分析裝置畢業設計,本人來自中國地質大學通信工程專業,2020學年大二上的通信與信號處理的實習題目便是參考2018年TI杯G題——數字信號時序分析裝置,此實習需要自學stm32單片機,具有

2021-08-09 08:33:45

在進行數字電路系統的設計時,時序是否能夠滿足要求直接影響著電路的功能和性能。本文首先講解了時序分析中重要的概念,并將這些概念同數字系統的性能聯系起來,最后結合FPGA的設計指出時序約束的內容和時序

2020-08-16 07:25:02

(path groups):時序路徑可以根據與路徑終點相關的時鐘進行分類,因此每個時鐘都有一組與之相關的 時序路徑 。靜態時序分析和報告通常分別在每個時序路徑組中單獨執行。注意: 除了上述與時鐘相關的時序

2023-04-20 16:17:54

靜態時序分析STA是什么?靜態時序分析STA的優點以及缺點分別有哪些呢?

2021-11-02 07:51:00

靜態時序分析與邏輯設計

2017-12-08 14:49:57

本文提出新的Π模型方法,結合了門的等效電容來計算門的延時,我們的方法結合門的互連線負載的拓撲結構和門負載三階矩求解的方法,采用中提出的等效電容的求解公式,求出門延時計算模型,相比上述兩種方法,在靜態時序分析中更為合理。

2021-04-23 07:04:07

不能保證100%的覆蓋率。如果到了門級的仿真將非常消耗時間。 靜態時序分析靜態時序分析只能分析時序要求而不能進行功能驗證。不需要測試向量,能比動態時序分析快地多的完成分析。靜態時序分析只能對同步電路

2021-09-04 14:26:52

某16K x 4的存儲體由16個字長為1的 DRAM芯片在位方向和字方向同時擴展而成,DRAM芯片中所有的記憶單元排列成行列相等的存儲矩陣。分析:由題得,16個DRAM芯片需要先在位方向擴展為4位得

2022-03-02 06:18:45

1. 適用范圍 本文檔理論適用于Actel FPGA并且采用Libero軟件進行靜態時序分析(寄存器到寄存器)。2. 應用背景 靜態時序分析簡稱STA,它是一種窮盡的分析方法,它按照同步電路設計

2012-01-11 11:43:06

基本的時序分析理論1本文節選自特權同學的圖書《FPGA設計實戰演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 何謂靜態時序分析(STA,Static

2015-07-09 21:54:41

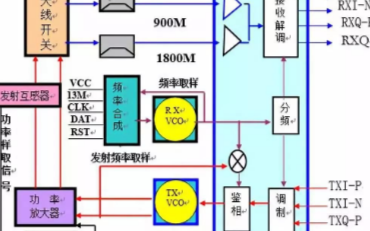

MTK手機基帶各種電路的分析和介紹

2012-08-16 15:24:10

MTK手機基帶各種電路的分析和介紹

2014-04-10 10:37:16

,SX1301動態數據速率(DDR),SX1308動態數據速率調整(ADR)。SX1308數字基帶芯片是一個巨大的數字信號處理引擎,專門設計用于在ISM全球范圍內提供突破性網關功能,集成了LoRa集中器IP

2021-04-03 10:07:30

自己做了一個工程,靜態時序分析的結果CLK信號的SLACK是負值(-7.399ns),書上說該值是負值時說明時序不對,但是我感覺時序仿真的結果是對的。是不是時序仿真波形正確就不用管靜態時序分析的結果了?請高手指點

2010-03-03 23:22:24

iphone高通基帶和英特爾基帶,聲明:針對蘋果與高通基帶芯片專利糾紛,來了興致,收集一波信息.以下信息對百度百科的基帶芯片進行整理;維基百科沒有基帶芯片介紹;1 簡介基帶芯片是用來合成即將發射

2021-07-28 06:42:24

靜態時序分析與邏輯設計

2015-05-27 12:28:46

為什么靜態時序分析受組件(符號)名稱的影響?我在示意圖中有一個ISR,當我把它稱為“CuttIsIr”時,靜態時序分析返回一個警告“設置時間違反”,但是當我稱之為“UTHISISR”時,一切都

2019-07-30 10:42:26

挑戰。這些收發器可為模擬RF信號鏈提供數字接口,允許輕松集成到ASIC或FPGA,進行基帶處理。基帶處理器(BBP)允許在終端應用和收發器設備之間的數字域中處理用戶數據。

2019-09-19 06:20:59

摘要:介紹了靜態時序分析在數字集成電路設計中的應用,并以100M以太網卡芯片設計為例,具體描述了以太網卡芯片設計中的靜態時序分析流程及其時序問題。 關鍵詞:靜態時序分析 100M以太網卡 數字

2018-08-28 11:58:31

各位好,初次使用pt對fpga進行靜態時序分析,想請教下需要哪些文件。是不是需要:1、在ise或qutartus生成的網表2、SDC文件3、.db文件.db文件必須且只能從dc生成嗎,要是從.lib轉化而來,這個lib文件在fpga設計時又從哪里得到問題貌似比較多,謝謝回答

2014-12-18 16:15:12

關于靜態分析和時序約束的文章

2014-07-17 12:12:35

華為靜態時序分析與邏輯設計

2014-05-20 22:55:09

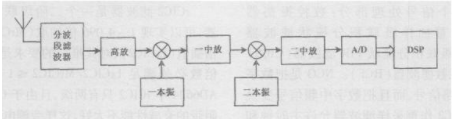

隨著數字技術的進步,高速、超大規模集成電路廣泛使用,3G移動終端基帶信號處理系統正朝著靈活、高度集成化、模塊化、通用化的方向發展。基帶信號處理器是數字技術與通信技術相結合的產物,它能靈活處理數字基帶

2019-07-03 06:18:48

畢業設計題目,毫無頭緒,求指導。主要內容:通信原理》課程中,數字基帶信號傳輸碼型是最重要的教學內容之一。在傳輸系統中,需要各種不同的傳輸碼型及其相互變換。該設計要求分析通信系統基帶傳輸的常用碼型

2015-02-28 18:09:14

對基帶信號進行數字化處理時為什么需使用輸入濾波器?

2023-12-21 06:55:35

來至網友的提問:對基帶信號進行數字化處理時為什么需使用輸入濾波器?

2018-12-12 09:07:39

以下針對目前項目所用到的SRAM時序進行分析,同時也對SRAM應用在STM32F4上進行詳細解說。以此也可以類推出NAND/PSRAM等時序的應用技巧。時序當前用到的是模式A,其中讀時序如下。圖片截

2022-01-07 07:20:20

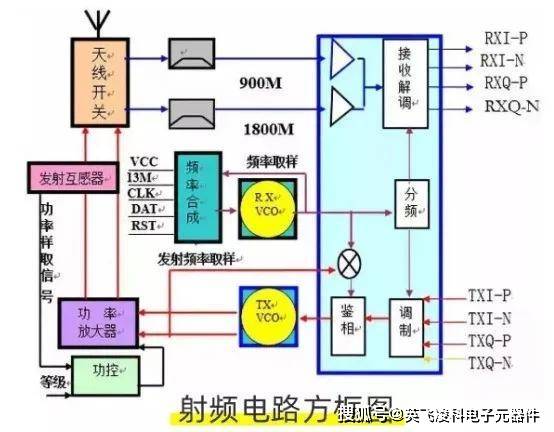

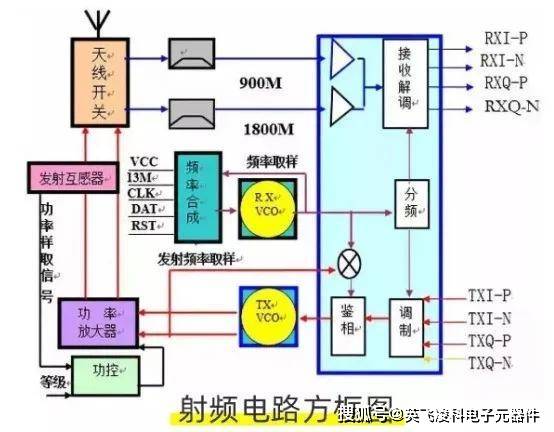

射頻芯片和基帶芯片的關系是什么?射頻芯片是什么工作原理?

2021-06-15 09:16:25

靜態時序分析(Static Timing Analysis,STA)是流程成功的關鍵環節,驗證設計在時序上的正確性。STA過程中設計環境和時序約束的設定、時序結果的分析和問題解決都需要設計工程師具有

2020-09-01 16:51:01

而又美好,那么我們這么多學費就沒白交哈~ 下面我們進入正題,今天我們講時序一、從靜態時序分析說起 我理解的靜態時序分析,就是我們在不加激勵的情況下,通過對電路進行時序的延遲計算,預計電路的工作流

2015-03-31 10:20:00

高速電路信號完整性分析與設計—時序計算引入:在數字電路中,從一個芯片發信息A到另一個芯片變成信息B,那么這個數字系統失敗;如何保證信息不變?關鍵點,就是在傳輸過程的任意點都保持時序的正確性。時序概念

2009-09-12 10:28:42

同步時序數字電路的分析二進制同步計數器 分析步驟: 1.確定電路是否是同步時序數字電路 2.確定觸發器的驅動方程 3.做出狀態轉換表 4.做出分析結論 BC

2008-10-20 10:10:43 30

30 時序約束與時序分析 ppt教程

本章概要:時序約束與時序分析基礎常用時序概念QuartusII中的時序分析報告

設置時序約束全局時序約束個別時

2010-05-17 16:08:02 0

0 靜態時序概念,目的

靜態時序分析路徑,方法

靜態時序分析工具及邏輯設計優化

2010-07-09 18:28:18 129

129 本文首先以Synopsys公司的工具Prime Time SI為基礎,介紹了ASIC設計中主流的時序分析方法:靜態時序分析及其基本原理和操作流程;接著分析了它與門級仿真之間的關系,提出了幾個在T

2010-08-02 16:44:16 10

10

AD6900數字基帶處理器在多媒體的設計與應用

多媒體處理,

2010-03-11 15:08:45 901

901

摘要

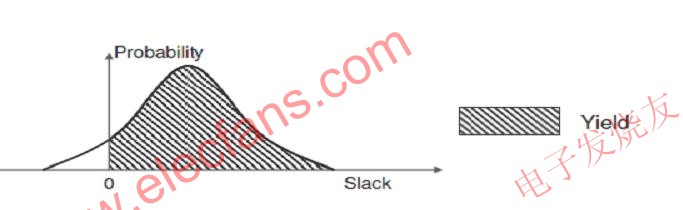

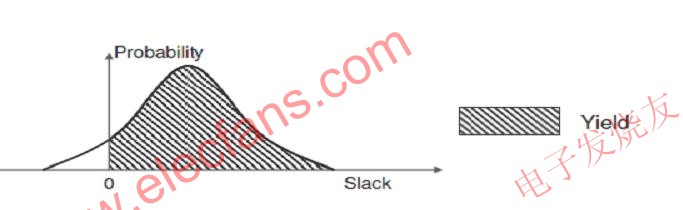

是否曾想過為什么一個設計能夠以高于設計團隊承諾的頻率工作?為何該設計團隊不能將這個更高的頻率當作要實現的目標?

過去,靜態時序分

2010-09-25 09:37:15 4313

4313

在制程進入深次微米世代之后,芯片(IC)設計的高復雜度及系統單芯片(SOC)設計方式興起。此一趨勢使得如何確保IC質量成為今日所有設計從業人員不得不面臨之重大課題。靜態時序

2011-05-11 16:53:43 0

0 介紹了采用STA (靜態時序分析)對FPGA (現場可編程門陣列)設計進行時序驗證的基本原理,并介紹了幾種與STA相關聯的時序約束。針對時序不滿足的情況,提出了幾種常用的促進 時序收斂的方

2011-05-27 08:58:50 70

70 在制程進入深次微米世代之后,芯片(IC)設計的高復雜度及系統單芯片(SOC)設計方式興起。此一趨勢使得如何確保IC質量成為今日所有設計從業人員不得不面臨之重大課題。靜態時序

2011-05-27 09:02:19 90

90 討論了靜態時序分析算法及其在IC 設計中的應用。首先,文章討論了靜態時序分析中的偽路徑問題以及路徑敏化算法,分析了影響邏輯門和互連線延時的因素。最后通過一個完整的IC 設計

2011-12-20 11:03:16 95

95 本內容介紹了手機基帶相關內容,手機基帶是什么,手機基帶版本等

2012-05-24 14:48:32 5527

5527 _靜態時序分析(Static_Timing_Analysis)基礎及應用[1]。

2016-05-09 10:59:26 31

31 華為靜態時序分析與邏輯設計,基礎的資料,快來下載吧

2016-09-01 15:44:10 56

56 靜態時序分析基礎及應用

2017-01-24 16:54:24 7

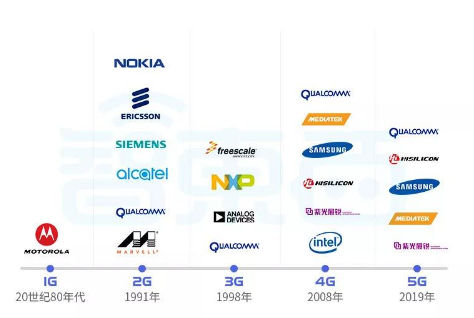

7 目前基帶芯片在我們生活中已經得到廣泛的運用,本文主要詳細介紹了基帶芯片的定義與組成,其次也羅列出了基帶芯片的六大產商。

2017-12-16 11:54:55 42090

42090 STA的簡單定義如下:套用特定的時序模型(Timing Model),針對特定電路分析其是否違反設計者給定的時序限制(Timing Constraint)。以分析的方式區分,可分為Path-Based及Block-Based兩種。

2018-04-03 15:56:16 10

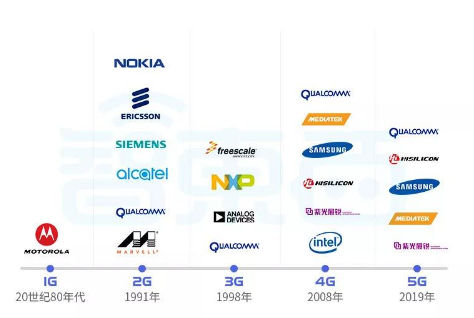

10 隨著5G網絡的即將商用,手機芯片廠商紛紛搶先推出了自家的5G芯片。手機芯片可以分為射頻芯片、基帶調制解調器以及核心應用處理器,此前高通、英特爾、三星、華為先后展示了自家的5G基帶芯片,并宣布預計將在2019年商用。

2019-01-11 10:09:06 3992

3992 靜態時序分析中的“靜態”一詞,暗示了這種時序分析是一種與輸入激勵無關的方式進行的,并且其目的是通過遍歷所有傳輸路徑,尋找所有輸入組合下電路的最壞延遲情況。這種方法的計算效率使得它有著廣泛的應用,盡管它也存在一些限制。

2019-11-22 07:11:00 2088

2088 靜態時序或稱靜態時序驗證,是電子工程中,對數字電路的時序進行計算、預計的工作流程,該流程不需要通過輸入激勵的方式進行仿真。

2019-11-22 07:09:00 2103

2103 靜態時序分析是一種驗證方法,其基本前提是同步邏輯設計(異步邏輯設計需要制定時鐘相對關系和最大路徑延時等,這個后面會說)。靜態時序分析僅關注時序間的相對關系,而不是評估邏輯功能(這是仿真和邏輯分析

2019-11-22 07:07:00 3179

3179 20 X 5G版也將在本周五正式上市。在期待了半年時間后,5G手機終于來了!

5G手機與4G手機相比,在硬件上最大的區別在于5G基帶芯片。當下,5G基帶芯片領域的第一戰已經打響!頭部的五家大廠憑借

2019-07-24 08:54:37 9869

9869

德克薩斯州AUSTIN-IC表征提供商Silicon Metrics Corp.將推出基于SiliconSmart Models的產品線。該系列產品包括該公司為邏輯設計人員提供的首個產品 - 一種可延長靜態時序分析儀精度的時序簽核工具。

2019-08-13 11:37:41 2870

2870 靜態時序分析簡稱STA,它是一種窮盡的分析方法,它按照同步電路設計的要求,根據電路網表的拓撲結構,計算并檢查電路中每一個DFF(觸發器)的建立和保持時間以及其他基于路徑的時延要求是否滿足。

2019-09-01 10:45:27 2942

2942

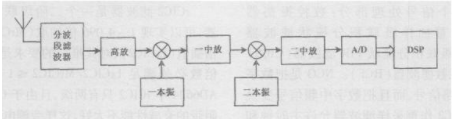

傳統來說,一部可支持打電話、發短信、網絡服務、APP應用的手機,一般包含五個部分部分:射頻部分、基帶部分、電源管理、外設、軟件。 射頻部分:一般是信息發送和接收的部分; 基帶部分:一般是信息處理

2020-06-29 10:54:19 19965

19965

在手機終端中,最重要的核心就是射頻芯片和基帶芯片。射頻芯片負責射頻收發、頻率合成、功率放大;基帶芯片負責信號處理和協議處理。那么射頻芯片和基帶芯片是什么關系?

2020-07-08 10:17:40 5315

5315 靜態時序分析是檢查芯片時序特性的一種方法,可以用來檢查信號在芯片中的傳播是否符合時序約束的要求。相比于動態時序分析,靜態時序分析不需要測試矢量,而是直接對芯片的時序進行約束,然后通過時序分析工具給出

2020-11-11 08:00:00 58

58 在手機終端中,最重要的核心就是射頻芯片和基帶芯片。射頻芯片負責射頻收發、頻率合成、功率放大;基帶芯片負責信號處理和協議處理。那么射頻芯片和基帶芯片是什么關系?

2020-11-20 09:42:16 18653

18653

傳統來說,一部可支持打電話、發短信、網絡服務、APP 應用的手機,一般包含五個部分部分:射頻部分、基帶部分、電源管理、外設、軟件。射頻部分:一般是信息發送和接收的部分;基帶部分:一般是信息處理的部分

2020-12-29 04:37:00 65

65 本文檔的主要內容詳細介紹的是華為FPGA硬件的靜態時序分析與邏輯設計包括了:靜態時序分析一概念與流程,靜態時序分析一時序路徑,靜態時序分析一分析工具

2020-12-21 17:10:54 18

18 進行靜態時序分析,主要目的就是為了提高系統工作主頻以及增加系統的穩定性。對很多數字電路設計來說,提高工作頻率非常重要,因為高工作頻率意味著高處理能力。通過附加約束可以控制邏輯的綜合、映射、布局和布線,以減小邏輯和布線延時,從而提高工作頻率。

2021-01-08 16:47:25 15

15 任何學FPGA的人都跑不掉的一個問題就是進行靜態時序分析。靜態時序分析的公式,老實說很晦澀,而且總能看到不同的版本,內容又不那么一致,為了徹底解決這個問題,我研究了一天,終于找到了一種很簡單的解讀辦法,可以看透它的本質,而且不需要再記復雜的公式了。

2021-01-12 17:48:08 19

19 靜態時序分析的前提就是設計者先提出要求,然后時序分析工具才會根據特定的時序模型進行分析,給出正確是時序報告。

進行靜態時序分析,主要目的就是為了提高系統工作主頻以及增加系統的穩定性。對很多數字

2021-01-12 17:48:07 15

15 在制程進入深次微米世代之后,晶片(IC)設計的高復雜度及系統單晶片(SOC)設計方式興起。此一趨勢使得如何確保IC品質成為今日所有設計從業人員不得不面臨之重大課題。靜態時序分析(Static

2021-01-14 16:04:02 3

3 本文檔的主要內容詳細介紹的是時序分析的靜態分析基礎教程。

2021-01-14 16:04:00 14

14 近日,市場研究機構Strategy Analytics在其官方微信公眾號發布的最新研究報告指出,2020年Q3,5G基帶芯片出貨量增長了十倍以上。5G基帶芯片處理器收益首次超過4G,并占總基帶收益的50%以上。

2021-02-01 15:09:42 1639

1639 AD6528:用于智能手機和無線的GSM/GPRS數字基帶處理器初步數據表

2021-04-25 13:40:06 7

7 本文在分析軟件無線電的寬帶數字中頻和數字下變頻的基本模型基礎上,結合ADI公司推出的接收信號處理器芯片AD6624的工作原理,提出CDMA基站反向鏈路中基帶信號處理的設計方案,并詳細討論了基帶濾波器的設計方法,同時給出了仿真結果。

2021-05-25 10:14:02 2708

2708

片內時序約束,要想實現高速信號的有效傳輸就必須進行片外靜態時序分析。本文作為在高速信號處理時信號輸入輸出的理論參考,之所以說作為理論參考是因為由于高速信號處理,具體的一些參數無法實際計算出來,只能在理論參考的方向

2021-06-18 16:22:26 1183

1183

一、前言 無論是FPGA應用開發還是數字IC設計,時序約束和靜態時序分析(STA)都是十分重要的設計環節。在FPGA設計中,可以在綜合后和實現后進行STA來查看設計是否能滿足時序上的要求。

2021-08-10 09:33:10 4767

4767

知名蘋果產業鏈研究員、天風國際分析師郭明錤透露,蘋果為 iPhone 自研的 5G 基帶芯片或遭遇失敗。

2022-07-18 16:13:02 12383

12383 另一種是手動的方式,在大型設計中,設計人員一般會采用手動方式進行靜態時序分析。手動分析方式既可以通過菜單操作(個人理解:通過鼠標點擊和鍵盤輸入)進行分析,也可以采用Tcl腳本(工具控制語言,個人理解運用代碼控制)進行約束和分析。

2022-08-19 17:10:25 1354

1354 靜態時序分析簡稱STA,它是一種窮盡的分析方法,它按照同步電路設計的要求,根據電路網表的拓撲結構,計算并檢查電路中每一個DFF(觸發器)的建立和保持時間以及其他基于路徑的時延要求是否滿足。STA作為

2022-09-27 14:45:13 1808

1808 對于建立時間和保持時間本文就不再過多敘述,可參考【FPGA】幾種時序問題的常見解決方法-------3,可以說在數字高速信號處理中最基本的概念就是建立時間和保持時間,而我們要做的就是解決亞穩態問題和傳輸穩定問題。

2022-12-13 11:03:58 225

225 任何學FPGA的人都跑不掉的一個問題就是進行靜態時序分析。靜態時序分析的公式,老實說很晦澀,而且總能看到不同的版本,內容又不那么一致,為了徹底解決這個問題,終于找到了一種很簡單的解讀辦法,可以看透

2023-03-14 19:10:03 443

443 任何學FPGA的人都跑不掉的一個問題就是進行靜態時序分析。靜態時序分析的公式,老實說很晦澀,而且總能看到不同的版本,內容又不那么一致,為了徹底解決這個問題,我研究了一天,終于找到了一種很簡單的解讀辦法,可以看透它的本質,而且不需要再記復雜的公式了。

2023-05-29 10:24:29 348

348

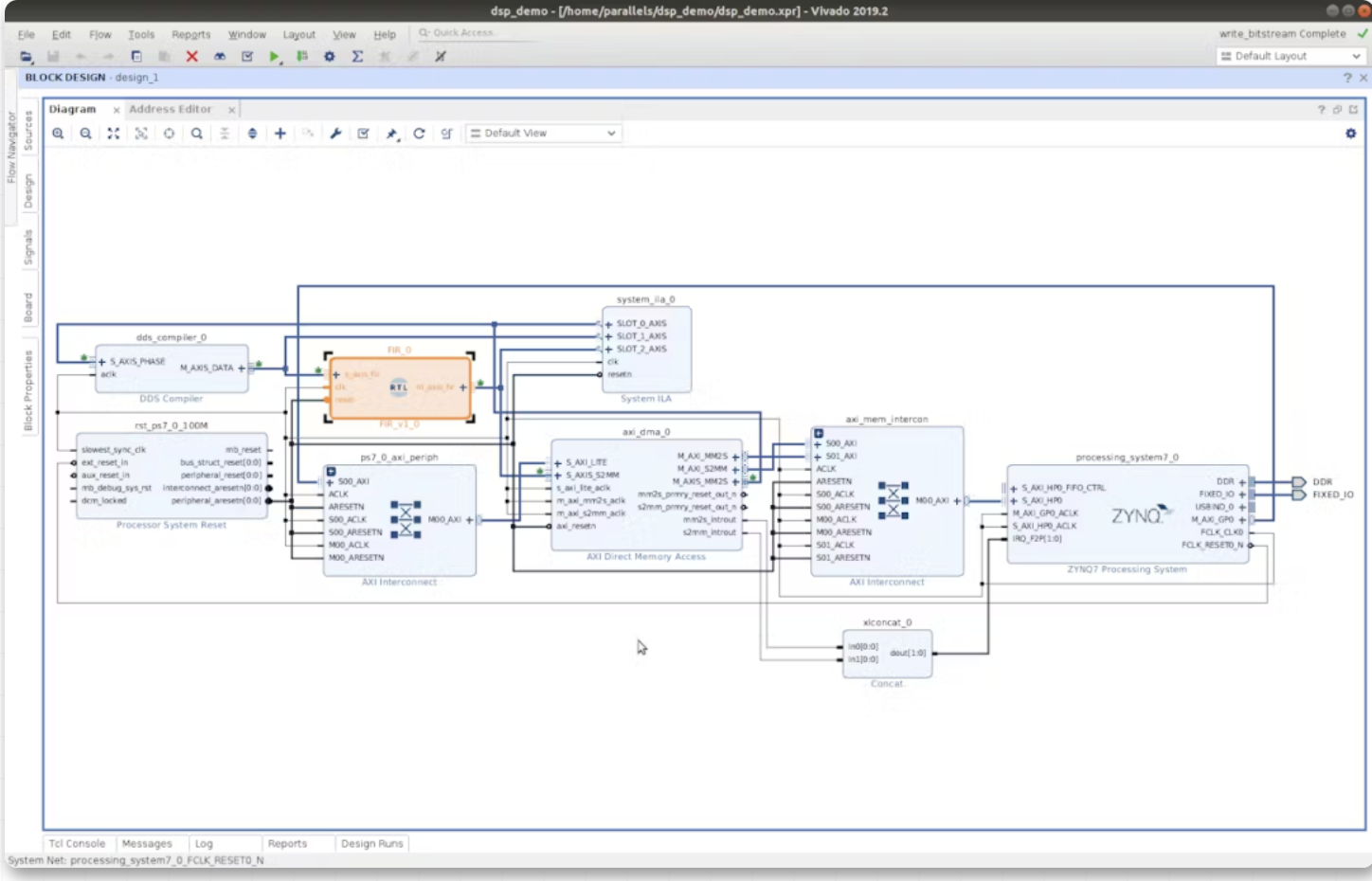

當在目標 FPGA 芯片中布局和布線時,首先在 Vivado 中確定時序要求.

2023-06-20 17:31:27 389

389

靜態時序分析(Static Timing Analysis, 以下統一簡稱 **STA** )是驗證數字集成電路時序是否合格的一種方法,其中需要進行大量的數字計算,需要依靠工具進行,但是我們必須了解其中的原理。

2023-06-27 11:43:22 523

523

引言 在同步電路設計中,時序是一個非常重要的因素,它決定了電路能否以預期的時鐘速率運行。為了驗證電路的時序性能,我們需要進行 靜態時序分析 ,即 在最壞情況下檢查所有可能的時序違規路徑,而不需要測試

2023-06-28 09:38:57 714

714

??本文主要介紹了靜態時序分析 STA。

2023-07-04 14:40:06 528

528

正如“聚合”的意思(字典)“兩個或多個事物聚集在一起的發生”。所以我們可以假設它也與 2 個時鐘路徑聚集在一起有關。 (了解時鐘路徑請參考另一篇博客-靜態時序分析基礎:第1部分“時序路徑”)

2023-08-08 10:31:44 524

524

。用通俗的話來說,射頻相當于話筒,基帶則相當于發出的聲音。 射頻芯片是專門負責處理高頻信號的芯片。在無線通信系統中,原始的電信號(基帶信號)首先經過數字信號處理器(DSP)的處理,然后經過數字模擬轉換器(DAC)轉換

2023-10-25 15:02:29 1748

1748 在手機終端中,最重要的核心就是射頻芯片和基帶芯片。射頻芯片負責射頻收發、頻率合成、功率放大;基帶芯片負責信號處理和協議處理。那么射頻芯片和基帶芯片是什么關系?

射頻芯片和基帶芯片的區別主要

2024-01-06 16:16:17 1506

1506

電子發燒友App

電子發燒友App

評論