本文首先闡述了FPGA的原理了,其次分析了FPGA比CPU和GPU快的原理,最后闡述了CPU與GPU的區(qū)別。

2018-05-31 09:00:29 15956

15956

DSP這幾年有點背,逐漸遠離主流 話題 ,所以有人就有了這樣的問題:DSP會被FPGA取代嗎? 網(wǎng)友一:獨立的DSP不會被FPGA替代,但是會被增強了信號處理功能的 ARM 處理器替代。現(xiàn)在基本已

2022-11-29 10:25:02 4007

4007

DSP+FPGA架構(gòu)的最大特點是結(jié)構(gòu)靈活、有較強的通用性、適合于模塊化設(shè)計,從而能夠提高算法效率,同時其開發(fā)周期短、系統(tǒng)易于維護和升級,適合于實時視頻圖像處理,電機控制,數(shù)據(jù)采集。單DSP核心的系統(tǒng)

2016-09-24 10:41:18

本帖最后由 yicunyu 于 2016-7-18 16:45 編輯

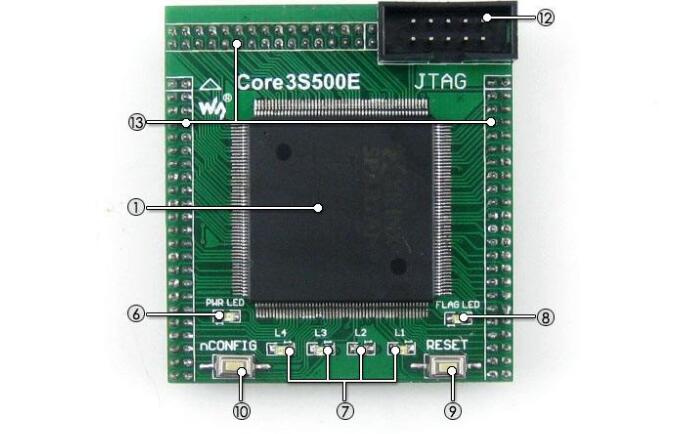

DSP28335+FPGA的數(shù)據(jù)采集系統(tǒng),DSP采用TI公司的TMS320F28335,FPGA使用 ALTERA

2016-07-16 14:32:23

和效率在數(shù)字信號處理這塊基本無人能出其右)FPGA呢相對來說可以運用的面比較廣泛(不過也是近期的事情。其實FPGA很早就有。只是當(dāng)初設(shè)計領(lǐng)域都是通信方面的。現(xiàn)在有集成CPU和DSP以及公司提供的軟核的強力支持,設(shè)計面越來越廣)

2017-04-21 14:23:27

硬件DSP:是ASIC,如同CPU/GPU一樣,適合量產(chǎn),降低成本,缺點是(硬件)設(shè)計一旦確定,便不易于修改。FPGA :通過HDL 快速設(shè)計,但成本較高,用于ASIC的prototype設(shè)計。與DSP比較軟件-編程語言DSP:DSP寫...

2021-07-28 09:06:55

隨著模擬IC市場中眾多垂直細分行業(yè)的飛速發(fā)展,傳統(tǒng)DSP器件遭遇了各種替代性信號處理平臺的競爭,FPGA即為典型代表。憑借高密度、低功耗和低成本的優(yōu)勢,FPGA不僅在通信、消費類、嵌入式等廣泛

2019-06-27 07:06:16

本人剛?cè)腴TFPGA,不知道如何實現(xiàn)FPGA+DSP,FPGA+ARM接口設(shè)計,網(wǎng)上查詢有的說FPGA+DSP可以通過EMIF,IP核實現(xiàn),FPGA+ARM可以通過SPI,有沒有具體硬件參考的?

2016-08-27 11:30:26

FPGA從1984 年到今天,發(fā)展經(jīng)歷了30 多年時間。它可以替代其他 PLD 或者各種中小規(guī)模數(shù)字邏輯芯片在數(shù)字系統(tǒng)中廣泛應(yīng)用,也是實現(xiàn)具有不同邏輯功能ASIC 的有效辦法。

FPGA 融合了

2023-11-02 17:22:20

求推薦一本有關(guān)FPGA和DSP的經(jīng)典書籍(深入版)

2016-07-23 14:18:45

,新一代基站設(shè)施成為二者競爭的焦點,同時Femtocell的發(fā)展?jié)摿σ参?b class="flag-6" style="color: red">FPGA和DSP廠商。 飛思卡爾是第一個向市場推出商用四核心DSP的廠商。飛思卡爾現(xiàn)在在市場上主推的產(chǎn)品是第二代四核DSP

2019-07-19 06:10:44

FPGA是什么?有何功能?ARM是什么?有何功能?DSP是什么?有何功能?FPGA與DSP有何關(guān)系?

2021-10-21 07:17:53

發(fā)揮更大的功能應(yīng)用。除此之外,用FPGA實現(xiàn)ASIC的前期的設(shè)計驗證,FPGA實現(xiàn)DSP的功能,實現(xiàn)CPU的功能,MCU的功能,內(nèi)存控制器,用于工業(yè)的PWM,SVPWM,Clarke,Park的正

2019-05-07 01:28:40

的廉價產(chǎn)品;其次,對于DSP的投入將是可持續(xù)發(fā)展,并且無論是人才還是開發(fā)平臺都是極易得到的。 鄭小龍進一步強調(diào),FPGA作為硬件可編程平臺近年來也獲得了較大的發(fā)展,特別是也有集成了嵌入式CPU核心

2014-01-09 17:52:31

競爭冒險:在組合電路中,當(dāng)邏輯門有兩個互補輸入信號同時向相反狀態(tài)變化時,輸出端可能產(chǎn)生過渡干擾脈沖的現(xiàn)象,稱為競爭冒險。那么 FPGA 產(chǎn)生競爭冒險的原因是什么呢? 信號在 FPGA 器件內(nèi)部通過

2024-02-21 16:26:56

FPGA中競爭冒險問題的研究

2012-08-04 16:16:06

FPGA怎么實現(xiàn):實時兩路視頻數(shù)據(jù)的融合,即實時模糊兩路圖像交接處的縫隙?

2016-02-23 13:54:54

FPGA的方案選擇 幸運的是,需要高性能DSP功能的便攜式設(shè)備設(shè)計者還有其它選擇。最近FPGA開始達到了應(yīng)用所要求的成本競爭力。優(yōu)選的FPGA方案可用來處理計算量繁重的高端DSP算法,同時還可

2011-02-17 11:21:37

應(yīng)用。另外用FPGA實現(xiàn)ASIC的前期的設(shè)計驗證,FPGA實現(xiàn)DSP的功能,實現(xiàn)CPU的功能,MCU的功能,內(nèi)存控制器,用于工業(yè)的PWM,SVPWM,Clarke,Park的正逆變換的實現(xiàn),VGA控制

2019-04-10 08:00:00

摘 要:以現(xiàn)場可編程門陣列(以下簡稱FPGA)在設(shè)計中由于其內(nèi)部構(gòu)成,容易引起競爭問題。以我們在實驗教學(xué)中的應(yīng)用與實踐為主線,詳細介紹了消除競爭冒險的各種方法。關(guān)鍵詞:現(xiàn)場可編程

2009-04-21 16:44:44

請問一下各位牛人,我看spartan那個fpga里面有dsp 資源,我需要做一些浮點運算,請問fpga里面的dsp是怎么才能使用的啊,謝謝

2019-10-15 13:37:46

可編程器件門電路數(shù)有限的缺點。可以毫不夸張的講,FPGA能完成任何數(shù)字器件的功能,上至高性能CPU,下至簡單的74電路,都可以用FPGA來實現(xiàn)。FPGA如同一張白紙或是一堆積木,工程師可以通過傳統(tǒng)

2021-09-08 17:49:20

芯片的處理器實現(xiàn)這兩種功能,將加速個人通信機、智能電話、無線網(wǎng)絡(luò)產(chǎn)品的開發(fā),同時簡化設(shè)計,減小PCB體積,降低功耗和整個系統(tǒng)的成本。 3、DSP 和高檔CPU的融合:大多數(shù)高檔GPP如PenTIum

2017-06-29 11:37:24

應(yīng)用。另外用FPGA實現(xiàn)ASIC的前期的設(shè)計驗證,FPGA實現(xiàn)DSP的功能,實現(xiàn)CPU的功能,MCU的功能,內(nèi)存控制器,用于工業(yè)的PWM,SVPWM,Clarke,Park的正逆變換的實現(xiàn),VGA控制

2019-08-11 08:00:00

控制密集型,許多人都用dsp高算法,用fpga 作外圍控制電路。去年xilinx在北京介紹FPGA和DSP融合的時候,大有席卷DSP和FPGA市場之勢。但后來在實際中發(fā)現(xiàn)其阻力也是不小的,關(guān)鍵是很難搭配

2018-10-10 18:02:03

這幾年有點背,逐漸遠離主流話題,所以有人就有了這樣的問題:DSP會被FPGA取代嗎?小編總結(jié)了各個網(wǎng)友的回答: 網(wǎng)友一:獨立的DSP不會被FPGA替代,但是會被增強了信號處理功能的ARM處理器替代

2021-07-16 08:12:03

我在做fpga與dsp的SRIO通信,我用的是論壇上提供的SRIO test程序,目前dsp端能夠?qū)崿F(xiàn)端口0的外部回環(huán)測試。fpga端的協(xié)議還沒做通,我想用dsp直接給fpga發(fā)包,fpga根據(jù)收到

2018-06-21 10:45:13

今天和大俠簡單聊一聊FPGA的競爭冒險和毛刺問題,話不多說,上貨。

FPGA從1984 年到今天,發(fā)展經(jīng)歷了30 多年時間。它可以替代其他 PLD 或者各種中小規(guī)模數(shù)字邏輯芯片在數(shù)字系統(tǒng)中廣

2023-05-30 17:15:28

我需要在視頻切換時,進行淡入淡出的切換效果,具體算法很簡單,就是yuv數(shù)據(jù)按照一定比例融合。對于1080數(shù)據(jù),像素非常多,每像素都要運算,總運算量是每秒千萬級別的,導(dǎo)致vpss所在的m3的cpu

2019-08-26 08:44:23

DSP與CPU有什么區(qū)別啊?

2019-09-06 05:38:32

和航空航天等嵌入式應(yīng)用領(lǐng)域,目前的市場需求是:以更低成本、更低功耗、更小尺寸處理日益復(fù)雜的功能。這些市場需求正推動著FPGA、CPU、DSP等不同技術(shù)走向融合。 對FPGA技術(shù)來說,早期研發(fā)在5年前就已開始

2011-07-21 10:52:00

Altera公司用FPGA做DSP算法的工具

2006-03-25 13:46:45 39

39 混合CPU_FPGA系統(tǒng)的調(diào)試方法:

2009-07-23 10:44:07 7

7 介紹了一種基于DSP和FPGA的GPS-B碼時統(tǒng)終端系統(tǒng)的設(shè)計方案,提出了一種利用FPGA對IRIG-B碼進行解碼的設(shè)計方法。詳細論述了具體的設(shè)計方案及軟硬件的實現(xiàn)。通過將快速的DSP與FPGA相結(jié)

2010-02-24 13:48:49 22

22 FPGA實現(xiàn)DSP應(yīng)用

摘要:具有系統(tǒng)級性能的FPGA在半導(dǎo)體工藝的線寬達到深亞微米后更進一步按信號處理的要求改進器件結(jié)構(gòu)和性能,不僅可實現(xiàn)VLSI DSP,且具有系統(tǒng)

2010-04-01 15:39:54 14

14 FPGA的DSP應(yīng)用

近年來由于多媒體技術(shù)和無線通信的發(fā)展,對DSP應(yīng)用的要求不斷地增長,但是這些應(yīng)用對信號處理要求高,需要采用處理速度高的硬件來實現(xiàn)DSP,所以,隨著CMOS工藝的

2010-04-07 14:25:58 16

16 The FPGA Development Platform provides all the tools neccesaary to design, build, and execute your

2010-07-01 15:38:55 14

14 用可再配置FPGA實現(xiàn)DSP功能

2010-07-16 17:56:43 10

10 本文首先簡單介紹某小型基于DSP和FPGA的導(dǎo)航計算機系統(tǒng),然后根據(jù)其子系統(tǒng)輸出的有效信息設(shè)計可行的信息融合算法;針對其子系統(tǒng)有效輸出結(jié)果的時間不同步性,結(jié)合系統(tǒng)實際情

2010-08-06 17:01:05 21

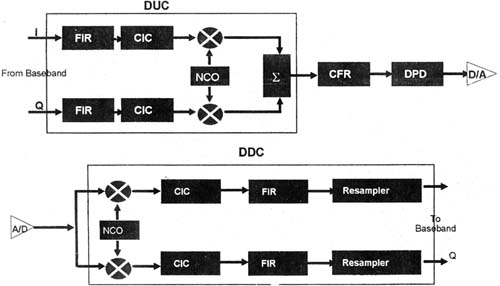

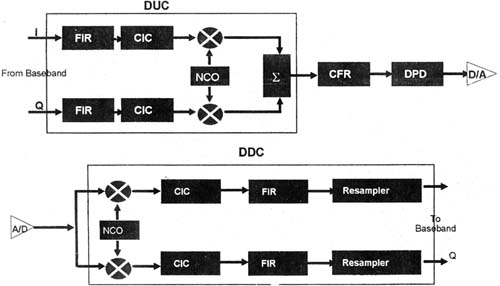

21 FPGA和DSP組合在無線基站中的應(yīng)用

在自動控制產(chǎn)品中,CPD+DSP+MCU的構(gòu)架是目前最為流行的成熟方案,而在通訊產(chǎn)品中,大量使用FPGA設(shè)計,合理使用FPGA

2009-10-12 11:20:11 975

975

基于DSP和FPGA的通用圖像處理平臺設(shè)計

摘要:設(shè)計一種基于DSP和FPGA架構(gòu)的通用圖像處理平臺,運用FPGA實現(xiàn)微處理器接口設(shè)計,并對圖像數(shù)據(jù)進行簡單預(yù)處理,利用DSP

2010-02-01 11:10:21 1379

1379

安富利推出Xilinx Virtex-6 FPGA DSP開發(fā)工具套件安富利公司旗下運營機構(gòu)安富利電子元件宣布推出Xilinx Virtex -6 FPGA DSP開發(fā)工具套件。這套件是為DSP設(shè)計而打造,是Xilinx目標(biāo)設(shè)計平

2010-04-24 09:56:31 1331

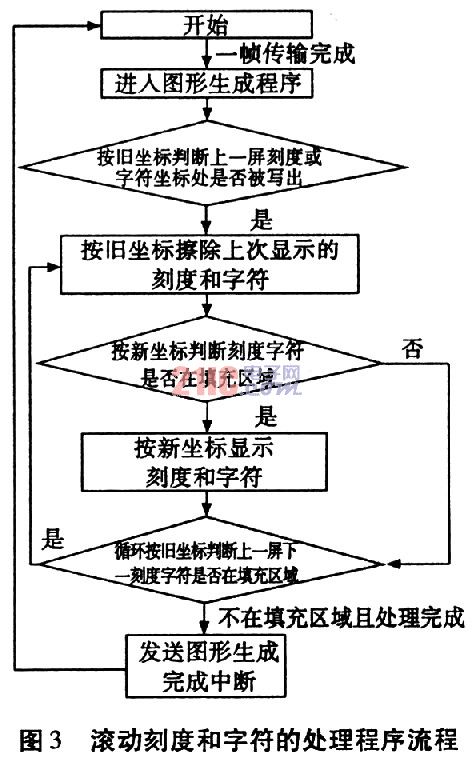

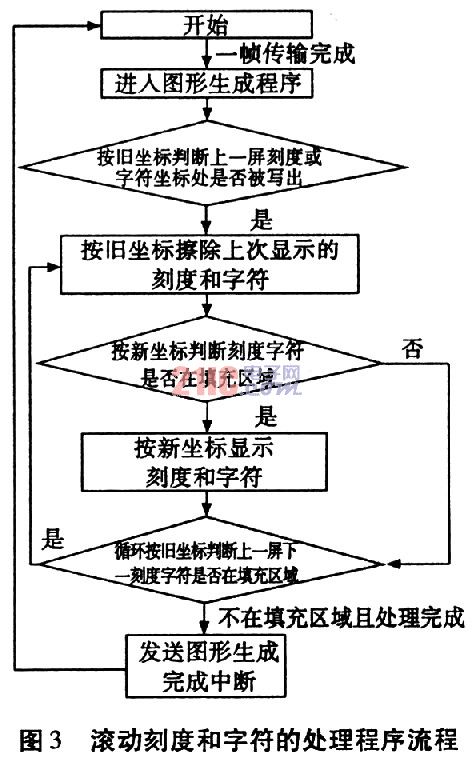

1331 本文設(shè)計了基于DSP與FPGA的系統(tǒng)結(jié)構(gòu),采用了軟硬件填充的圖形處理方法,先由DSP軟件完成圖形輪廓生成,然后FPGA硬件圖形處理器根據(jù)圖形輪廓完成耗時的圖形填充,使系統(tǒng)在實時性

2010-07-01 11:02:38 988

988

ARM、DSP、FPGA的技術(shù)特點和區(qū)別

2010-09-03 21:41:26 2310

2310 摘要:為了實現(xiàn)高速HDLC通訊協(xié)議,設(shè)計了DSP+FPGA結(jié)構(gòu)的485通訊接口,接口包括DSP、FPGA、485轉(zhuǎn)換等硬件電路,以及DSP與FPGA之間的數(shù)據(jù)交換程序和FPGA內(nèi)部狀態(tài)機;其中DSP用于實現(xiàn)數(shù)據(jù)控制,FPGA用于實現(xiàn)HDLC通訊協(xié)議,DSP與FPGA之間采用XINTF方式,通過雙FI

2011-02-25 17:24:34 98

98 System Generator 工具由 MathWorks 與 Xilinx 合作開發(fā)而成,DSP 設(shè)計人員可使用 MATLAB 和Simulink 工具在 FPGA 內(nèi)進行開發(fā)和仿真來完善 DSP 設(shè)計。 該工具為系統(tǒng)級 DSP 設(shè)計與 FPGA 硬件實現(xiàn)的融合起

2011-05-11 18:36:23 224

224 電子發(fā)燒友為您提供了ARM、DSP、FPGA三者的定義與其之間的區(qū)別!

2011-06-23 10:34:39 3664

3664 為滿足導(dǎo)航系統(tǒng)設(shè)計的小型化、實時性要求,本文提出了一種基于FPGA + DSP 的實現(xiàn)方案。該方案的設(shè)計思路是:將FPGA 映射到DSP EMIF 的一段地址空間,并用FPGA 來完成多通道信號的采集; DSP 根

2011-09-13 14:32:08 77

77 Alter FPGA的設(shè)計流程以及DSP設(shè)計.

2012-03-16 15:52:07 127

127 設(shè)計了一種基于DSP與FPGA的運動控制器。該控制器以DSP為控制核心,用FPGA構(gòu)建運動控制器與傳感器以及電機驅(qū)動器的接口電路。充分發(fā)揮了DSP強大的運算能力和FPGA的并行處理能力。具有

2012-10-26 15:21:51 93

93 DSP之cpu_timer教程,很好的DSP自學(xué)資料,快來學(xué)習(xí)吧。

2016-04-15 16:16:02 13

13 基于DSP和FPGA的SVPWM算法及其在變頻調(diào)速中的應(yīng)用。

2016-04-18 09:47:49 20

20 基于DSP與FPGA的運動控制器設(shè)計,下來看看。

2016-05-10 11:24:33 29

29 異步FIFO在FPGA與DSP通信中的運用

2016-05-19 11:17:11 0

0 dsp fpga 電路 打標(biāo)機上用的主板

2016-06-27 15:24:08 7

7 基于DSP和FPGA技術(shù)的細胞圖像采集系統(tǒng)設(shè)計

2016-08-26 12:57:52 15

15 基于FPGA的多幅圖像融合疊加的設(shè)計與實現(xiàn)

2016-08-30 15:10:14 11

11 基于FPGA和DSP的圖像多功能卡的設(shè)計與實現(xiàn)

2016-09-22 12:32:08 28

28 基于DSP和FPGA的多頻聲納采集系統(tǒng)設(shè)計_劉寅

2017-03-19 11:45:23 0

0 基于FPGA和DSP網(wǎng)絡(luò)單向時延測量系統(tǒng)設(shè)計與實現(xiàn)_唐旭

2017-03-19 11:38:26 0

0 基于雙DSP和雙FPGA的高速圖像處理系統(tǒng)設(shè)計_吳雷

2017-03-16 09:28:51 2

2 FPGA與ARM、DSP的區(qū)別

2017-03-15 08:00:00 9

9 隨著模擬 IC 市場中眾多垂直細分行業(yè)的飛速發(fā)展,傳統(tǒng) DSP 器件遭遇了各種替代性信號處理平臺的競爭,FPGA 即為典型代表。憑借高密度、低功耗和低成本的優(yōu)勢,FPGA 不僅在通信、消費類、嵌入式

2017-09-13 20:49:50 9

9 基于異步FIFO在FPGA與DSP通信中的運用

2017-10-19 10:30:56 10

10 基于FPGA和多DSP的多總線并行處理器設(shè)計

2017-10-19 13:40:31 4

4 基于FPGA和DSP的高速圖像處理系統(tǒng)

2017-10-19 13:43:31 19

19 基于FPGA的VME總線與DSP通信接口設(shè)計

2017-10-19 13:49:30 26

26 基于DSP與FPGA的便攜式超聲探傷儀

2017-10-19 14:21:56 7

7 DSP和FPGA的HDLC協(xié)議通訊電路設(shè)計

2017-10-19 14:46:11 7

7 基于DSP的FPGA配置方法研究與實現(xiàn)

2017-10-19 16:15:19 36

36 摘要 利用異步FIFO實現(xiàn)FPGA與DSP進行數(shù)據(jù)通信的方案。FPGA在寫時鐘的控制下將數(shù)據(jù)寫入FIFO,再與DSP進行握手后,DSP通過EMIFA接口將數(shù)據(jù)讀入。文中給出了異步FIFO的實現(xiàn)

2017-10-30 11:48:44 1

1 今天,FPGA越來越多地應(yīng)用在多種DSP中。我們預(yù)計這一趨勢在未來幾年會更加明顯。美國調(diào)查機構(gòu)Berkeley設(shè)計技術(shù)公司做了上述預(yù)測。以Xilinx和Altera為主的兩大FPGA廠商多年前就涉足

2017-11-06 10:48:09 1

1 今天,FPGA越來越多地應(yīng)用在多種DSP中。我們預(yù)計這一趨勢在未來幾年會更加明顯。美國調(diào)查機構(gòu)Berkeley設(shè)計技術(shù)公司做了上述預(yù)測。以Xilinx和Altera為主的兩大FPGA廠商多年前就涉足

2017-11-06 13:58:57 7

7 的ASIC相比,它們提供的產(chǎn)品在多個方面都更勝一籌,例如具有更快的產(chǎn)品上市速度,以及更多的設(shè)計靈活性。然而截至目前,在與DSP的競爭中,人們卻普遍認(rèn)為,FPGA在性價比方面的表現(xiàn)遠不如DSP。 不過,技術(shù)咨詢公司Berkeley Design Technology(BDTI)一項最新但是具有

2017-11-06 13:59:20 1

1 CPU+FPGA的并行處理是目前的發(fā)展趨勢這種處理方式將大行其道。

2018-01-02 15:54:07 15989

15989 FPGA仿真篇-使用腳本命令來加速仿真二 基于FPGA的HDMI高清顯示借口驅(qū)動 基于FPGA灰度圖像高斯濾波算法的實現(xiàn) FPGA為什么比CPU和GPU快 基于Xilinx FPGA的視頻圖像采集

2018-02-20 20:49:00 1478

1478 CPU和GPU都屬于馮·諾依曼結(jié)構(gòu),指令譯碼執(zhí)行,共享內(nèi)存。FPGA之所以比CPU、GPU更快,本質(zhì)上是因為其無指令,無共享內(nèi)存的體系結(jié)構(gòu)所決定的。

2018-04-02 17:52:31 95602

95602 本文首先分析了FPGA是否會取代DSP,其次介紹了FPAG結(jié)構(gòu)特點與優(yōu)勢及DSP的基本結(jié)構(gòu)和特征,最后闡述了FPGA與DSP兩者之間的區(qū)別。

2018-05-31 09:51:25 35710

35710

如下圖,FPGA作為協(xié)處理器,CPU把指令寫入內(nèi)存,FPGA從內(nèi)存讀取指令執(zhí)行,并把計算結(jié)果寫入內(nèi)存。這種模式的優(yōu)點是簡單易行,協(xié)處理器和CPU分離。瓶頸在于共享內(nèi)存,限制了性能,同時由于通過內(nèi)存

2018-06-20 15:17:10 12724

12724 FPGA是一種可編程的硅芯片,DSP是數(shù)字信號處理,當(dāng)系統(tǒng)設(shè)計人員在項目的架構(gòu)設(shè)計階段就面臨到底采用FPGA還是DSP的重要問題。本文將首先分別介紹FPGA和DSP的特點,然后再從內(nèi)部資源、編程語言、功能多個角度解析兩者的不同。

2018-09-29 16:43:35 30755

30755 隨著模擬IC市場中眾多垂直細分行業(yè)的飛速發(fā)展,傳統(tǒng)DSP器件遭遇了各種替代性信號處理平臺的競爭,FPGA即為典型代表。憑借高密度、低功耗和低成本的優(yōu)勢,FPGA不僅在通信、消費類、嵌入式等廣泛領(lǐng)域中行使DSP的職能,并且已經(jīng)快速滲透到諸多新興應(yīng)用領(lǐng)域之中。

2018-11-05 17:53:15 1775

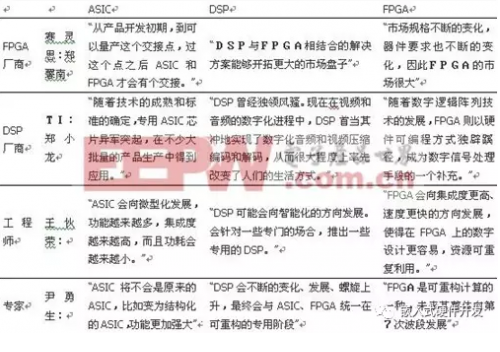

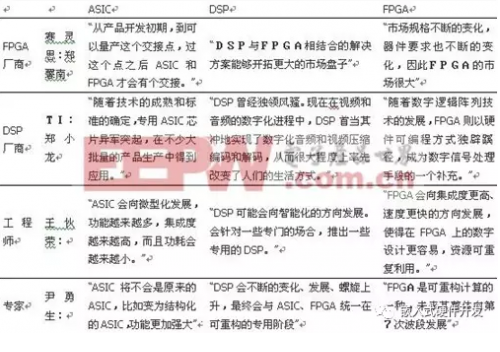

1775 在相當(dāng)長的一段時間內(nèi),FPGA、ASIC、DSP三者不同的技術(shù)特征造就了它們不同的應(yīng)用領(lǐng)域,DSP在數(shù)字信號方面是絕對的霸主,ASIC是專業(yè)定制領(lǐng)域的牛人,而FPGA由于其價格高、功耗大,主要

2018-11-17 11:30:34 741

741

本文檔的主要內(nèi)容詳細介紹的是FPGA視頻教程之FPGA設(shè)計中如何避免冒險競爭。

2019-03-22 17:04:08 12

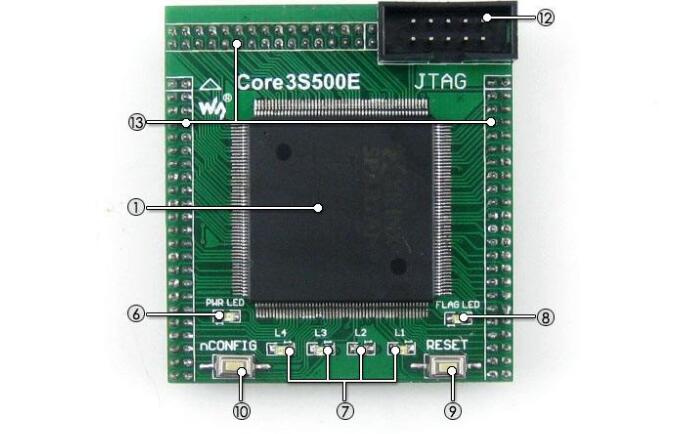

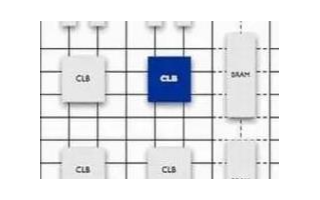

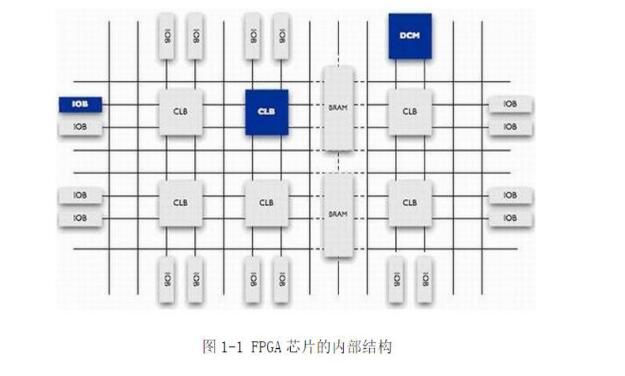

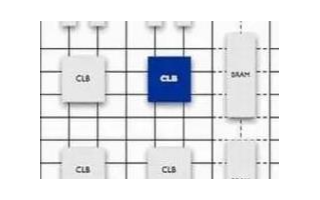

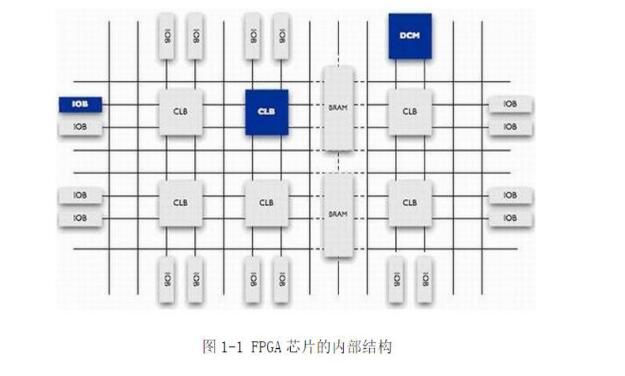

12 與其他計算載體如CPU與GPU相比,FPGA具有高性能、低能耗以及可硬件編程的特點。圖1介紹了FPGA的硬件架構(gòu),每個FPGA主要由叁個部分組成:輸入輸出邏輯,主要用于FPGA與外部其他部件,比如傳感器的通信。

2019-10-21 14:56:17 2474

2474 目前數(shù)字電路系統(tǒng)設(shè)計領(lǐng)域公認(rèn)的基礎(chǔ)性技術(shù)分別是CPU、DSP和FPGA。其中FPGA技術(shù)發(fā)展迅速,正在逐漸融合CPU和DSP的功能。FPGA不僅可以解決電子系統(tǒng)小型化、低功耗、高可靠性等問題,而且其開發(fā)周期短、投入少,芯片價格又在不斷下降。

2020-07-14 14:09:48 722

722 從CPU的總體結(jié)構(gòu)到局部功能的實現(xiàn)采用了自頂向下的設(shè)計方法和模塊化的設(shè)計思想, 利用Xilinx 公司的Spartan II 系列FPGA, 設(shè)計實現(xiàn)了八位CPU軟核。在FPGA 內(nèi)部不僅實現(xiàn)

2020-08-19 17:43:19 5

5 型到大型的幾乎所有數(shù)字電路系統(tǒng),dsp主要完成復(fù)雜的數(shù)字信號處理,如fft,通常一個復(fù)雜系統(tǒng)可以由單片機、arm、fpga、dsp中的一種或幾種構(gòu)成,各有優(yōu)勢和不足。 dsp通常用于運算密集型,fpga用于控制密集型,許多人都用dsp高算法,用fpga作外圍控制

2020-10-25 09:50:06 3085

3085 我們知道,FPGA的頻率一般只有幾百MHz,而CPU的頻率卻高達數(shù)GHz。那么,有不少網(wǎng)友心中就有一個疑問:為什么FPGA主頻比CPU慢,但卻可以用來幫CPU做加速?。 今天,EDN就和大家

2020-11-20 09:56:16 3581

3581 基于FPGA和DSP的機載圖形顯示系統(tǒng)

2021-06-08 10:48:08 36

36 基于FPGA和DSP的圖像采集監(jiān)測通信平臺

2021-06-16 09:38:29 20

20 CPU、MCU、MPU及DSP的區(qū)別CPU(Central Processing Unit,中央處理器)發(fā)展出來三個分枝,一個是DSP(Digital Signal Processing

2021-10-28 11:20:59 23

23 它們之間的關(guān)系CPU是最基本的存在,因為某些原因,在CPU的外部又包裹了部分附加功能,和CPU一起共同構(gòu)成MCU、DSP、SOC等這些芯片,因此它們都是從CPU的基礎(chǔ)上擴展而來,基本關(guān)系我們可以

2021-10-28 15:51:14 35

35 CPU、MCU、MPU、DSP的區(qū)別?CPU(CentralProcessing Unit,中央處理器)發(fā)展出來三個分枝,一個是DSP(Digital Signal Processing

2021-10-28 16:51:10 57

57 FPGA,arm,stm32,dsp特點對比

2021-11-19 13:21:02 24

24 廣州星嵌DSP/ARM/FPGA 選型手冊2023

2023-05-05 10:24:22 15

15 fpga與dsp通訊怎樣同步時鐘頻率?dsp和fpga通信如何測試? 在FPGA與DSP通訊時,同步時鐘頻率非常重要,因為不同的設(shè)備有不同的時鐘頻率,如果兩者的時鐘頻率不同步,會導(dǎo)致通訊數(shù)據(jù)的錯誤

2023-10-18 15:28:13 1060

1060

電子發(fā)燒友App

電子發(fā)燒友App

評論