8月21日,臺積電在其官方博客上宣布,自2018年開始量產(chǎn)的7nm工藝,其所生產(chǎn)的芯片已經(jīng)超過10億顆。此外,臺積電官網(wǎng)還披露了一個消息,其6nm工藝制程于8月20日開始量產(chǎn)。 先看7nm

2020-08-23 08:23:00 5211

5211 從芯片的制造來看,7nm就是硅材料芯片的物理極限,而臺積電更先進的7nm工藝也將開始進入試產(chǎn)階段。

2016-10-21 10:23:23 881

881 從芯片的制造來看,7nm就是硅材料芯片的物理極限,到了7nm節(jié)點即使是finfet也不足以在保證性能的同時抑制漏電,所以工業(yè)界用砷化銦鎵取代了單晶硅溝道來提高器件性能。

2016-10-21 14:46:30 6088

6088 芯片的7nm工藝我們經(jīng)常能聽到,但是7nm是否真的意味著芯片的尺寸只有7nm呢?讓我們一起來看看吧!

2023-12-07 11:45:31 1603

1603

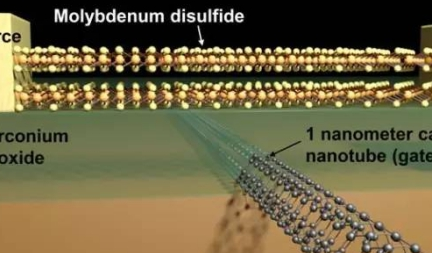

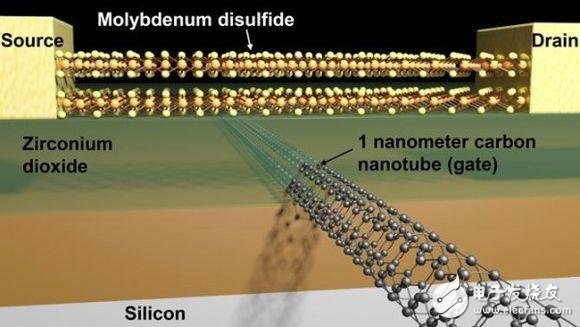

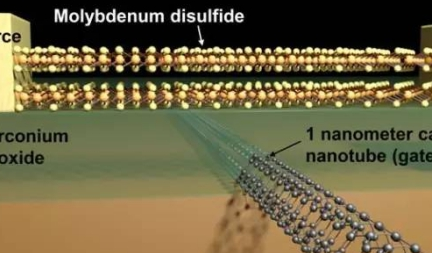

隸屬美國能源部的勞倫斯伯克利國家實驗室Ali Javey 團隊即宣稱,突破了物理極限,成功創(chuàng)造1 納米晶體管。

2016-10-09 09:52:06 1615

1615

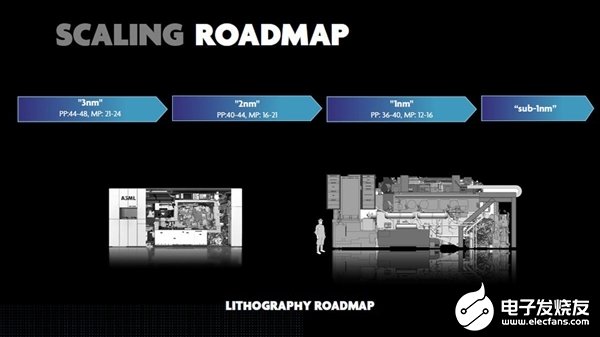

3nm工藝,外媒的報道顯示,臺積電是計劃每平方毫米集成2.5億個晶體管。 作為參考,采用臺積電7nmEUV工藝的麒麟9905G尺寸113.31mm2,晶體管密度103億,平均下來是0.9億/mm2,3nm工藝晶體管密度是7nm的3.6倍。這個密度形象化比喻一下,就是將奔騰4處理器縮小到

2020-04-20 11:27:49 4113

4113 自然期刊,這對于1nm以下的半導體制程來說是一次巨大的突破。 ? 當前主流半導體制程已經(jīng)發(fā)展至3nm和5nm,乃至IBM也在近期推出了2nm,但單位面積內(nèi)所能容納的晶體管數(shù)目也已經(jīng)逼近硅的物理極限,雖說制程突破受制于生產(chǎn)設備,卻也

2021-05-18 09:00:00 5549

5549 很多晶體管組成的。芯片制程是指在芯片中,晶體管的柵極寬度。因為在整個芯片中,晶體管的柵極是整個電路中最窄的線條。如果柵極寬度為10nm,則稱其為10nm制程。納米數(shù)越小,比如從10nm到 7nm,就可以

2019-12-10 14:38:41

GPU和CPU產(chǎn)品依舊在使用五年前的14nm工藝或者其改進版本。新的10nm、7nm工藝雖然已經(jīng)上市,但是綜合頻率、功耗、晶體管密度等因素來看,其表現(xiàn)依舊不能令人滿意。進入2020年,也就是21世紀20

2020-07-07 11:38:14

智能座艙芯片行業(yè)銷售模式及銷售渠道

**10 **研究成果及結(jié)論

表格目錄

表 1:按產(chǎn)品類型細分,全球7nm智能座艙芯片市場規(guī)模2019 VS 2023 VS 2030(萬元)

表 2:按應用細分

2024-03-16 14:52:46

7nm新工藝的加持:RX 5500 XT可輕輕松松突破2GHz

2021-06-26 07:05:34

國內(nèi)的通富微電成為AMD 7nm芯片的封測廠商之一

2020-12-30 07:48:47

技(Synopsys, Inc., 納斯達克股票市場代碼: SNPS)近日宣布,在設計人員的推動下,F(xiàn)usion Design Platform?已實現(xiàn)重大7nm工藝里程碑,第一年流片數(shù)突破100,不僅

2020-10-22 09:40:08

XX nm制造工藝是什么概念?為什么說7nm是物理極限?

2021-10-20 07:15:43

的晶體管制程從14nm縮減到了1nm。那么,為何說7nm就是硅材料芯片的物理極限,碳納米管復合材料又是怎么一回事呢?面對美國的技術(shù)突破,中國應該怎么做呢?XX nm制造工藝是什么概念?芯片的制造...

2021-07-28 07:55:25

7nm 設計挑戰(zhàn)高級節(jié)點存在許多設計挑戰(zhàn),例如:老化效應隨著晶體管器件的開啟和關閉,有兩個主要的物理效應會影響可靠性:負偏壓溫度不穩(wěn)定性 ( NBTI )熱載體注入 (HCI)電路設計人員了解到

2022-11-04 11:08:00

從7nm到5nm,半導體制程芯片的制造工藝常常用XXnm來表示,比如Intel最新的六代酷睿系列CPU就采用Intel自家的14nm++制造工藝。所謂的XXnm指的是集成電路的MOSFET晶體管柵極

2021-07-29 07:19:33

來源:wikichip) 盡管EUV光刻機相當之貴,接近1.2億美元一臺,但半導體廠商還是愿意去投入,因為7nm以及以上的工藝的確需要EUV光刻機,幾時同樣的7nm工藝,使用EUV光刻技術(shù)之后晶體管

2020-07-07 14:22:55

nm晶圓廠進入生產(chǎn)狀態(tài)。臺積電的5nm制程分為N5及N5P兩個版本。N5相較于當前的7nm制程N7版本在性能方面提升了15%、功耗降低了30%,晶體管密度提升了80%。N5P版本性能較N5提升7

2020-03-09 10:13:54

,共同致力于有機、透明與軟性的電子研究。 “有機半導體將成為信息時代的‘原油’,屆時,摩爾定律也將在7nm節(jié)點達到極限,”TU Dresden有機組件研究主席Stefan Mansfield表示

2018-11-12 16:15:26

、65nm、45nm、32nm、22nm、14nm、10nm、到現(xiàn)在的7nm(對應都是MOS管柵長),目前也有了很多實驗室在進行一些更小尺寸的研究。隨著MOS管的尺寸不斷的變小,溝道的不斷變小,出現(xiàn)各種

2020-12-10 06:55:40

10月7日,沉寂已久的計算技術(shù)界迎來了一個大新聞。勞倫斯伯克利國家實驗室的一個團隊打破了物理極限,將現(xiàn)有最精尖的晶體管制程從14nm縮減到了1nm。晶體管的制程大小一直是計算技術(shù)進步的硬指標。晶體管

2016-10-08 09:25:15

求一份tsmc 7nm standard cell library求一份28nm或者40nm 的數(shù)字庫

2021-06-25 06:39:25

Cavium芯片基站設計表明了并行發(fā)展趨勢。可能有些令人吃驚的是,晶體管問題也影響了模擬電路性能。例如,F(xiàn)PGA供應商Altera宣布,其28 nm工藝代芯片至芯片收發(fā)器最大速率從28 Gbps增加到

2014-09-01 17:26:49

10nm、7nm等到底是指什么?芯片工藝從目前的7nm升級到3nm后,到底有多大提升呢?

2021-06-18 06:43:04

本帖最后由 eehome 于 2013-1-5 10:10 編輯

高清圖詳解英特爾最新22nm 3D晶體管

2012-08-05 21:48:28

高清圖詳解英特爾最新22nm_3D晶體管

2012-08-02 23:58:43

目前的GS464V升級到LA664,因此單核性能有較大提升,達到市場上主流設計。至于未來的工藝,龍芯表示目前公司針對7nm的工藝制程對不同廠家的工藝平臺做評估,不過他們沒有透露什么時候跟進7nm工藝

2023-03-13 09:52:27

臺積電稱其已解決造成40nm制程良率不佳的工藝問題

據(jù)臺積電公司高級副總裁劉德音最近在一次公司會議上表示,臺積電40nm制程工藝的良率已經(jīng)提升至與現(xiàn)有65nm制程

2010-01-21 12:22:43 893

893 摩爾定律是指IC上可容納的晶體管數(shù)目,約每隔18個月便會增加一倍,性能也將提升一倍。然而事情的發(fā)展總歸會有一個權(quán)限,5nm則是硅芯片工藝的極限所在,事實上,隨著10nm、7nm芯片研發(fā)消息不斷報出

2016-12-22 10:23:11 42226

42226 據(jù)韓國ETnews報道稱,在7nm工藝上,三星已經(jīng)深知落后臺積電不少,后者除了手握蘋果、聯(lián)發(fā)科、華為客戶外,還憑借7nm工藝把高通新一代驍龍?zhí)幚砥饔唵螕屪撸@是三星所不能忍。

2017-06-27 14:20:53 647

647 隨著智能手機的發(fā)展,半導體工藝也急速提升,從28nm、16nm、10nm到7nm這些半導體代工廠們每天爭相發(fā)布最新的工藝制程,讓很多吃瓜群眾一臉懵逼不知道有啥用。

2018-06-10 01:38:00 46910

46910 驍龍855芯片突破制程工藝,采用7nm制程,比較前身更加節(jié)能。如果高通在2019年推出驍龍855,那么它有可能就是A13芯片,2019年的iPhone手機也會采用這個芯片。

2017-10-12 18:25:00 3387

3387 臺積電已經(jīng)在著手將其7nm制程工藝擴大到大規(guī)模生產(chǎn),臺積電的7nm制程工藝被稱作N7,將會在今年下半年開始產(chǎn)能爬坡。

2018-06-12 15:14:41 3315

3315 ,第46屆Cowen技術(shù)大會上,AMD技術(shù)總監(jiān)Mark Papermaster再一次向外公布朝向7nm工藝技術(shù)的發(fā)展,他表示7nm技術(shù)將會在晶體管密度和功耗上提升巨大,他還透露稱目前研發(fā)的7nm產(chǎn)品有三款,之后的產(chǎn)品都會應用7nm,下半年將會正式采樣。 本文引用地址: AMD現(xiàn)階段的12nm工藝

2018-07-06 10:33:00 826

826 勞倫斯伯克利國家實驗室的一個團隊打破了物理極限,將現(xiàn)有最精尖的晶體管制程從14nm縮減到了1nm。晶體管的制程大小一直是計算技術(shù)進步的硬指標。晶體管越小,同樣體積的芯片上就能集成更多,這樣一來處理器的性能和功耗都能會獲得巨大進步。

2018-06-22 15:44:04 4459

4459 2018年下半年,芯片行業(yè)即將迎來全新7nm制程工藝,而打頭陣的無疑是移動芯片,目前已知的包括蘋果Apple A12/華為麒麟980以及高通驍龍855都是基于7nm工藝,制程工藝似乎成為手機芯片升級換代的一大核心點,那么7nm制程工藝好在哪,對用戶來說有何價值呢?

2018-08-13 15:26:41 6720

6720 與16nm FF工藝相比,臺積電的7nm工藝(代號N7)將提升35%的性能,降低65%的能耗,同時晶體管密度是之前的三倍。2019年初則會推出EUV工藝的7nm+(代號N7+)工藝,晶體管密度再提升20%,功耗降低10%,不能性能沒有變化。

2018-08-17 10:28:30 18700

18700 據(jù)國際電子商情,近日,臺積電公布了3nm制程工藝計劃,目前臺南園區(qū)的3nm晶圓工廠已經(jīng)通過了環(huán)評初審,臺積電

2018-08-17 14:27:36 2951

2951 高通宣布,即將推出新一代旗艦移動平臺——驍龍855,該平臺將采用7nm制程工藝。

2018-08-24 15:22:54 3988

3988 作為全球首款TSMC 7nm 制程工藝的手機芯片,相比上一代產(chǎn)品麒麟970,它的芯片面積縮小了,晶體管密度卻提升到1.6 倍,性能也相應能提升20%,能效比提升40%。麒麟980相比當年的麒麟920,晶體管密度已經(jīng)提升6.8倍,性能提升2.5倍,能效則提升4.0倍。

2018-09-10 15:07:39 6187

6187 晶圓代工巨頭企業(yè)臺積電、三星和GF(格芯),在半導體工藝的發(fā)展上越來越迅猛,10nm制程才剛剛應用一年半,7nm制程便已經(jīng)好似近在眼前。

2018-09-28 14:49:55 4147

4147 電子產(chǎn)品趨勢更趨向微型化和低功耗的,這也就促使晶圓代工廠工藝的升級來支持。隨著晶圓工藝開發(fā)到7nm、5nm,但是設計7NM工藝的廠家不多,因為7nm晶圓工藝制程的門檻高。為什么7nm工藝制程這么

2018-10-23 15:08:13 230

230 和1Xnm半導體工藝的百花齊放相比,個位數(shù)的制程就顯得單調(diào)許多了,很多在10Xnm大放異彩的半導體公司都在7nm制程處遭遇到了苦頭。

2018-10-26 15:40:31 16638

16638 還是路線圖都在按計劃進行。 根據(jù)臺積電提供的數(shù)據(jù),7nm相比于目前的14/12nm可以將晶體管密度提高一倍,同等

2018-11-29 15:35:02 186

186 AMD日前發(fā)布了全球首款采用7nm工藝核心的游戲卡Radeon VII,定位直指RTX 2080,將在2月7日解禁發(fā)售。該顯卡制程工藝領先一代,晶體管密度提升100%,相同功耗下性能提升25%;同樣頻率下功耗降低50%。

2019-02-11 11:53:23 2862

2862 XX nm制造工藝是什么概念?芯片的制造工藝常常用90nm、65nm、40nm、28nm、22nm、14nm來表示。現(xiàn)在的CPU內(nèi)集成了以億為單位的晶體管,這種晶體管由源極、漏極和位于他們之間的柵極所組成,電流從源極流入漏極,柵極則起到控制電流通斷的作用。

2019-02-20 11:08:02 31991

31991 臺積電計劃在明年第一季度開始量產(chǎn)5nm芯片,5nm較7nm晶體數(shù)量將增加1.8倍,性能提升15%。不過在今年,2019款iPhone還是繼續(xù)采用7nm工藝制程的芯片,性能較上代的A12有所提升。而高通下一代旗艦芯片驍龍865將由三星代工,也是7nm EUV工藝制造。

2019-06-17 10:36:28 1119

1119 7nm工藝計劃2021年推出,相比10nm工藝晶體管密度翻倍,每瓦性能提升20%,設計復雜度降低了4倍。

2019-07-19 10:49:36 2832

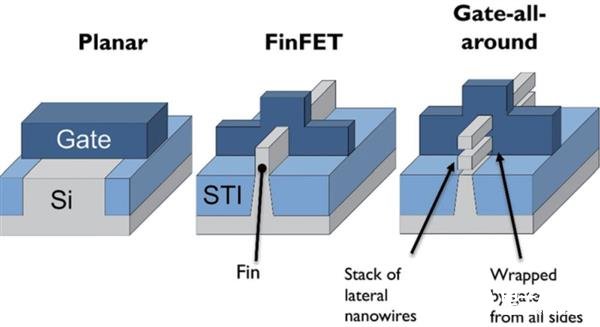

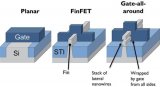

2832 目前全球最先進的半導體工藝已經(jīng)進入 7nm,下一步還要進入 5nm、3nm 節(jié)點,制造難度越來越大,其中晶體管結(jié)構(gòu)的限制至關重要,未來的工藝需要新型晶體管。

2019-12-10 15:40:49 7156

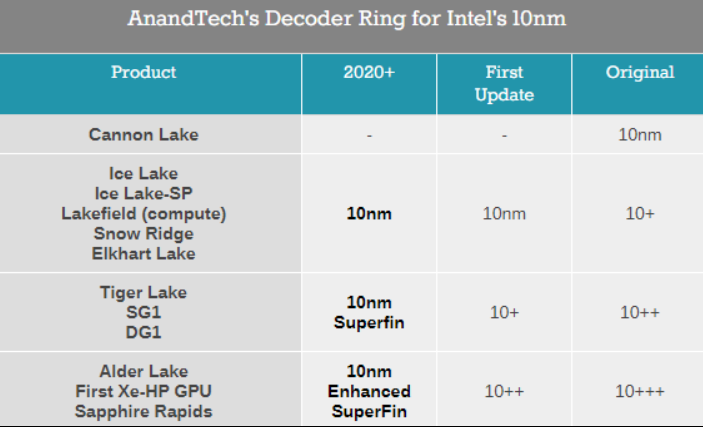

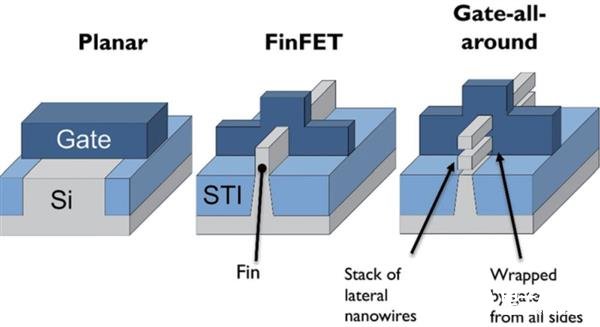

7156 在工藝制程方面,臺積電的進度明顯要快于英特爾。其實在2017年的時候,英特爾就指出臺積電7nm并非真實的7nm。而且英特爾呼吁行業(yè)應該統(tǒng)一命名標準,防止命名混亂。英特爾更希望以晶體管密度作為衡量標準。

2020-03-01 08:13:00 3016

3016 我們要不要過分夸大中芯國際呢,14nm能夠發(fā)揮7nm工藝的水平?如果說14nm高于12nm,筆者是相信的,畢竟當年的iphone 6s的兩個處理器是混用的。

2020-03-09 11:59:34 3314

3314 Intel之前已經(jīng)宣布在2021年推出7nm工藝,首發(fā)產(chǎn)品是數(shù)據(jù)中心使用的Ponte Vecchio加速卡。7nm之后的5nm工藝更加重要了,因為Intel在這個節(jié)點會放棄FinFET晶體管轉(zhuǎn)向GAA晶體管。

2020-03-11 08:56:47 2440

2440

Intel之前已經(jīng)宣布在2021年推出7nm工藝,首發(fā)產(chǎn)品是數(shù)據(jù)中心使用的Ponte Vecchio加速卡。7nm之后的5nm工藝更加重要了,因為Intel在這個節(jié)點會放棄FinFET晶體管轉(zhuǎn)向GAA晶體管。

2020-03-11 09:51:09 5687

5687

臺積電5nm制造工藝基于ULV,也就是紫外線光刻技術(shù)實現(xiàn),之前的7nm EUV工藝同樣也是基于這項技術(shù)。那么制程的縮小又意味著什么?相比于7nm工藝,5nm工藝可以進一步提升芯片的晶體管密度,提升性能并降低功耗,可廣泛用于PC、智能手機等設備的元器件中。

2020-03-12 14:10:44 2569

2569 近日,臺積電再拿下華為大單,據(jù)了解,華為麒麟820將采用臺積電7nm制程工藝。

2020-04-01 15:38:29 3592

3592 據(jù)國外媒體報道,圖形處理器廠商英偉達周四推出了他們首款基于安培架構(gòu)的GPU英偉達A100,采用7nm工藝制造,集成超過540億個晶體管。

2020-05-15 10:33:42 1698

1698 在近日的GTC上,Nvidia發(fā)布了最新的安培架構(gòu),以及基于安培架構(gòu)的A100 GPU。A100 GPU使用臺積電7nm工藝實現(xiàn),包含了542億個晶體管,據(jù)官方消息可以實現(xiàn)比起上一代V100高7倍的性能。

2020-05-20 10:17:50 2315

2315 在今年上半年,臺積電5nm工藝所生產(chǎn)的芯片,尚未出貨,營收排在首位的,也還是7nm工藝,在一季度和二季度,7nm分別貢獻了35%和36%的營收,超過三分之一。

2020-09-02 16:52:15 2373

2373 去年AMD推出了7nm Zen2架構(gòu)的銳龍、霄龍?zhí)幚砥鳎@是首款7nm工藝的x86處理器。不過嚴格來說它是7nm+14nm混合,現(xiàn)在AMD要加速甩掉14nm工藝了,IO核心也有望使用臺積電7nm工藝。

2020-09-24 10:12:58 1765

1765 關于芯片工藝,Intel前幾天還回應稱友商的7nm工藝是數(shù)字游戲,Intel被大家誤會了。不過今年Intel推出了新一代的10nm工藝,命名為10nm SuperFin工藝,簡稱10nm SF,號稱是有史以來節(jié)點內(nèi)工藝性能提升最大的一次,沒換代就提升15%性能,比其他家的7nm還要強。

2020-09-27 10:35:06 3537

3537

據(jù)英文媒體報道,臺積電近幾年在芯片制程工藝方面走在行業(yè)前列,他們的7nm和5nm工藝都是率先量產(chǎn),獲得了蘋果等公司的大量訂單,為他們帶來了可觀的營收。

2020-11-05 09:08:02 548

548 半年大規(guī)模投產(chǎn)。 在 2nm 工藝方面,外媒稱臺積電在去年就已組建了研發(fā)團隊,確定了 2nm 工藝的研發(fā)路線。 供應鏈的消息人士此前透露,臺積電的 2nm 工藝將采用多橋通道場效晶體管 (MBCFET)架構(gòu),這一架構(gòu)有助于克服鰭式場效晶體管 (FinFET)架構(gòu)因制程微縮產(chǎn)生電流控制漏電的物理

2020-11-17 17:34:02 1415

1415 臺積電、三星在2022年就有可能將制程工藝推到2nm,AMD、蘋果、高通、NVIDIA等公司也會跟著受益,現(xiàn)在自己生產(chǎn)芯片的就剩下Intel了,然而它們的7nm工藝已經(jīng)延期到至少2021年了。

2020-11-18 09:52:51 1857

1857 如今5nm才剛剛起步,臺積電的技術(shù)儲備就已經(jīng)緊張到了2nm,并朝著1nm邁進。根據(jù)最新報道,臺積電已經(jīng)在2nm工藝上取得一項重大的內(nèi)部突破,雖未披露細節(jié),但是據(jù)此樂觀預計,2nm工藝有望在2023

2020-11-26 10:48:09 2546

2546

1 月 15 日消息,據(jù)國外媒體報道,在蘋果轉(zhuǎn)向 5nm,華為無法繼續(xù)采用臺積電的先進工藝代工芯片之后,臺積電 7nm 的產(chǎn)能,也就有了給予其他廠商更多的可能,去年下半年 AMD 獲得的產(chǎn)能

2021-01-15 11:27:28 2631

2631 則是早早的用上了臺積電7nm工藝,晶體管集成度提高,性能和能耗比也有大幅提升。 近期,據(jù)驅(qū)動之家報道,半導體業(yè)內(nèi)人士稱,Intel將其南橋芯片組的生產(chǎn)外包給了三星,GPU芯片則委托給臺積電代工生產(chǎn),將使用臺積電的4nm工藝。 ? 這幾年Intel銷量占比持續(xù)下降,為了提高市場占

2021-01-25 17:58:53 1715

1715 得益于從平面型晶體管到鰭式場效應管(FinFET)的過渡,過去 10 年的芯片性能提升還算勉強。然而隨著制程工藝不斷抵近物理極限,芯片行業(yè)早已不再高聲談論摩爾定律。盡管業(yè)界對環(huán)繞柵極晶體管(GAAFET)在 3nm 及更先進制程上的應用前景很是看好,但這種轉(zhuǎn)變的代價也必然十分高昂。

2021-01-27 14:56:43 1941

1941 ,3nm工藝是今年下半年試產(chǎn),2022年正式量產(chǎn)。 與三星在3nm節(jié)點激進選擇GAA環(huán)繞柵極晶體管工藝不同,臺積電的第一代3nm工藝比較保守,依然使用FinFET晶體管。 與5nm工藝相比,臺積電3nm工藝的晶體管密度提升70%,速度提升11%,或者功耗降低27%。 不論是5nm還是3nm工

2021-02-19 15:13:40 2028

2028 。 原文如下: 說點題外話,大家就當看個熱鬧吧,既然說舊工藝的“疊加”,那咱就聊聊疊加嘛。 首先還是強調(diào)一點,現(xiàn)在所謂的幾 nm 工藝,這個幾 nm 的數(shù)字并不是指晶體管的 gate length(或溝道長度)——很多人對此是存在誤解的。比如臺積電的 7nm 工藝,晶體管并不存在

2021-07-02 16:39:34 5583

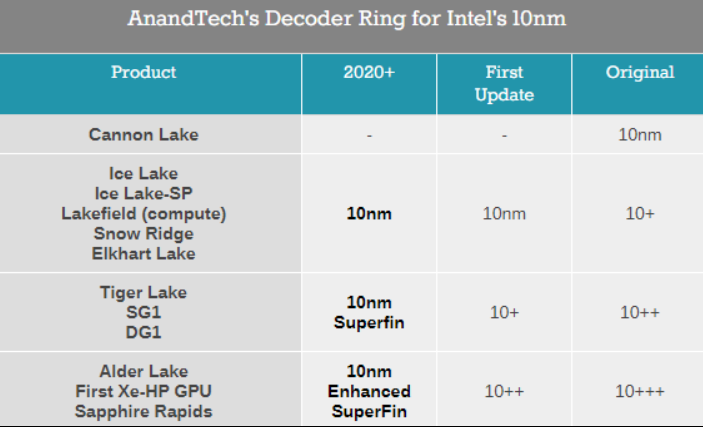

5583 半導體制程已經(jīng)進展到了3nm,今年開始試產(chǎn),明年就將實現(xiàn)量產(chǎn),之后就將向2nm和1nm進發(fā)。相對于2nm,目前的1nm工藝技術(shù)完全處于研發(fā)探索階段,還沒有落地的技術(shù)和產(chǎn)能規(guī)劃,也正是因為如此,使得1nm技術(shù)具有更多的想象和拓展空間,全球的產(chǎn)學研各界都在進行著相關工藝和材料的研究。

2021-12-17 15:18:06 10991

10991 1nm芯片是什么意思?目前芯片的代工工藝制程工藝已經(jīng)進入3nm節(jié)點,在1nm芯片制造技術(shù)節(jié)點迎來技術(shù)突破。芯片的發(fā)展一直都很快,有消息稱IBM與三星聯(lián)手將實現(xiàn)1nm及以下芯片制程工藝。

2021-12-17 14:34:43 30435

30435 制程3,首次將5G Modem集成到SoC上,方寸之地集成了約103億晶體管4,如發(fā)絲作畫,非奇跡而不為。承襲并進化麒麟優(yōu)秀基因,融合巴龍卓越5G能力,以硬核技術(shù)與超前智慧,決勝千里。麒麟990處理器的硬件參數(shù)。麒麟990處理器是采用了7nm制程工藝打造的八核處理器,CPU部分采用三叢集的設計,

2021-12-22 19:11:40 14

14 全球首顆2nm芯片已經(jīng)被IBM研制出來了,在這一顆指甲蓋大小面積的芯片上可以容納500億顆晶體管,芯片制程工藝的進步必將讓半導體行業(yè)的發(fā)展越來越快。接下來我們詳細了解下這款2nm芯片的特性、功耗等,跟7nm芯片做個對比,看下2nm芯片與7nm芯片之間有何差距。

2022-06-22 09:52:43 4352

4352 會問了:2nm芯片是極限嗎? 之前臺積電公布了先進制程發(fā)展規(guī)劃圖,從圖中我們可得知,在步入3nm制程后,臺積電將繼續(xù)在3nm上研發(fā)多代制程,直到2025年才能研發(fā)出2nm制程,而去年IBM就已經(jīng)研制出2nm芯片了,從去年到2025年如此長的時間里人類都在2nm及2nm之前的

2022-06-23 10:12:37 4233

4233 7nm和12nm指的是晶體管間的距離。在同等cpu面積下,距離越小,能夠擺放的晶體管數(shù)量也就越多。那么,對于運算速度而言,晶體管越多,運算速度提高的可能性也就越大。

2022-06-23 15:58:37 6458

6458 的重要性,我國目前最先進的制程7nm還正在研發(fā)當中,那么2nm芯片與7nm芯片的差距有多大呢? 拿臺積電的7nm舉例子,臺積電最初用DUV光刻機來完成7nm工藝,當時臺積電7nm工藝要比上一代16nm工藝密度高3.3倍,性能提升達到了35%以上,同樣性能下功耗減少了65%,在當時

2022-06-24 10:31:30 3662

3662 目前手機處理器的工藝制程是7nm,臺積電也即將量產(chǎn)5nm芯片,未來還有2nm甚至1nm芯片的出現(xiàn)。臺積電的研發(fā)負責人曾在談論半導體工藝極限的問題時,認為到2050年,晶體管可達0.1nm的氫原子尺度。

2022-06-24 16:10:03 22959

22959 已經(jīng)進入了試產(chǎn)階段,并且也從華為那邊收取到了麒麟710A的訂單,中芯國際表示過其12nm制程能夠?qū)崿F(xiàn)晶體管尺寸的縮減,相較于14nm制程,中芯國際的12nm制程將減少20%功耗和增加10%性能。 而相較于7nm芯片,12nm芯片在各方面就已經(jīng)就難以追趕了,以麒麟980和麒

2022-06-27 11:19:34 4561

4561 IBM的2nm制程芯片采用的是什么技術(shù)?IBM 2nm制程芯片采用GAA環(huán)繞柵極晶體管技術(shù),晶體管密度可達5nm兩倍,每平方毫米容納3.3億個晶體管,2nm芯片將計算速度要提高45%,能源效率更是提高75%,電池續(xù)航時間提升至之前的4倍。

2022-06-29 17:43:08 885

885 1 眾所周知,芯片制程工藝越小,芯片的性能就會越好,功耗也會更低,而隨著技術(shù)的發(fā)展,芯片制程工藝迎來了重要的7nm,而關于中芯國際12nm芯片的事又鬧得沸沸揚揚,那么12nm芯片和7nm芯片哪個費電

2022-07-01 09:43:27 2761

2761 有多大呢?是2nm嗎? 其實芯片前面的數(shù)字代表的是這款芯片所采用的制程工藝,2nm即為2nm制程工藝,而制程工藝又特指芯片內(nèi)部晶體管的柵極最小長度,柵極是晶體管內(nèi)用于控制電流的結(jié)構(gòu),因此2nm即代表著芯片內(nèi)部晶體管最小柵極長度為2nm,并不是代表整

2022-07-04 09:15:36 3936

3936 到2007年,當時Intel公司在舊金山舉辦了一場演講,在那場演講中,Intel CEO展示了一款32nm制程的芯片,他表示該芯片中集成了超過19億個晶體管,Intel將會在2009年正式量產(chǎn)32nm制程工藝的芯片。 2010年Intel推出了Corei7≤980X,這款芯片采用了32nm制程工藝

2022-07-04 09:47:46 3046

3046 臺積電首度推出采用GAAFET技術(shù)的2nm制程工藝,將于2025年量產(chǎn),其采用FinFlex技術(shù)的3nm制程工藝將于2022年內(nèi)量產(chǎn)。

2022-07-04 18:13:31 2636

2636 在芯片設計和制造中,納米表示的是芯片中晶體管與晶體管之間的距離,在體積相同大小的情況下,7nm工藝的芯片容納的晶體管的數(shù)量,幾乎是14nm工藝芯片的2倍。

2022-07-06 16:53:46 21551

21551 三星3nm采用的晶體管架構(gòu)是GAAFET,也被稱為Nanosheet,而1nm制程對晶體管架構(gòu)提出了更高的要求。

2022-09-05 15:03:57 4512

4512 IBM 剛剛官宣研發(fā)2nm芯片不久,臺積電再次發(fā)起了挑戰(zhàn)! 臺積電取得1nm以下制程重大突破,不斷地挑戰(zhàn)著物理極限。

2022-10-20 10:39:11 901

901 、臺積電及三星這三大芯片廠商也在沖刺,其中三星首個宣布2027年量產(chǎn)1.4nm工藝,臺積電沒說時間點,預計也是在2027年左右。 1.4nm之后就是1nm工藝了,這個節(jié)點曾經(jīng)被認為是摩爾定律的物理極限,是無法實現(xiàn)的,但是現(xiàn)在芯片廠商也已經(jīng)在攻關中。 臺積電已經(jīng)啟動了先導計劃,傳聞中的1nm晶圓

2022-10-31 11:06:30 1316

1316

在 VLSI 2021 上,imec 推出了 forksheet 器件架構(gòu),以將納米片晶體管系列的可擴展性擴展到 1nm 甚至更領先的邏輯節(jié)點。

2022-11-01 10:50:42 3482

3482

臺積電7nm產(chǎn)能利用率目前已跌至50%以下,預計2023年第一季度跌勢將加劇,臺積電高雄新廠7nm制程的擴產(chǎn)也被暫緩。

2022-11-10 11:12:08 416

416 然而,前不久麻省理工學院(MIT)華裔研究生朱家迪突破了常溫條件下由二維(2D)材料制造成功的原子晶體管,每個晶體管只有 3 個原子的厚度,堆疊起來制成的芯片工藝將輕松突破 1nm。

2023-05-30 14:24:48 1309

1309

然而,前不久麻省理工學院(MIT)華裔研究生朱家迪突破了常溫條件下由二維(2D)材料制造成功的原子晶體管,每個晶體管只有 3 個原子的厚度,堆疊起來制成的芯片工藝將輕松突破 1nm。

2023-05-31 15:45:29 1164

1164

據(jù)供應鏈消息透露,臺積電計劃真正降低其7nm制程的價格,降幅約為5%至10%。這一舉措的主要目的是緩解7nm制程產(chǎn)能利用率下滑的壓力。

2023-12-01 16:46:23 508

508 據(jù)消息人士透露,臺積電已經(jīng)決定將其1nm制程廠選址在嘉義科學園區(qū)。為了滿足這一先進制程技術(shù)的需求,臺積電已向相關管理局提出了100公頃的用地需求。

2024-01-23 15:15:27 894

894

電子發(fā)燒友App

電子發(fā)燒友App

評論