�����ھ��w�܈Dʾ�x��CPLD�������OӋ

�����w�܈Dʾ�x���·�OӋ�г��õ���Ӄx�������܉��@ʾ���w�ܵ�ݔ�����ԡ�ݔ�����Ժ��D�����Եȶ�N�����ͅ����������H���Ԝy�����w���O�ܺ����O�ܣ�߀���Ԝy����Ч���ܡ��������O�ܡ��νY���w�ܡ��ɿع����������������y�ľ��w�܈Dʾ�x�������·���s���w�e����ʾ���ܵ��@ʾ��С�����Ĵr���F��ȱ�c���S��Ӌ��CܛӲ�����g����Ƭ�C���g��EDA���g�IJ���lչ������늹���Ӝy�����g�đ��ã����w�܈Dʾ�x�ڽY��������ԭ�������ϰl���ܴ�׃�����ɞ锵�ֻ������ܻ���̓�M�x���������OӋ�ľ��w�܈Dʾ�x�����@��һ�N���̓x������������ԭ�Ѓx������֮�⣬߀�Uչ�˃x�����ܣ����ЈD�α��棬����̎���������@ʾ�`��ɲ����ԏ������܃r��ȸߵȃ��c��

����1 ϵ�y�Y����D

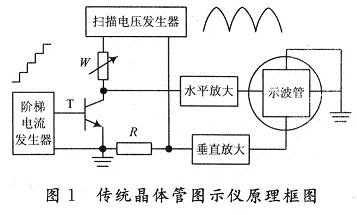

����1��1 ���y���w�܈Dʾ�x�Y��������ԭ��

�����ڂ��y�ľ��w�܈Dʾ�x�У���ģ�K��Ԫ��ȫ��ģ�M�·���}�_�����·�M�ɣ�����ȫӲ���Y������D1��ʾ������Ҫ�����A������l����������늉��l��������ֱ�Ŵ�ˮƽ�Ŵ��ʾ���ܵȡ��D��W��ؓ�d��裬R������ɘ���裬T�DZ��y���O�ܡ����^���O��ݔ�����������ǣ��ڻ��O�����׃�ėl���£���늘O늉������֮�g���Pϵ���ڜy�����O��ݔ�����������r���A������l������T�Ļ��Oʩ���A�������̖�����A�������ÿһ���_�A�r�g�ȣ�����늉��l������T�ļ�늘O��·ʩ�Ӓ���늉�������늉���50 Hz����늽������õ���T�ļ�늘O����ڲɘ����R�ϵĉ���(������늘O���)����ֱ�Ŵ��ӵ�ʾ���ܴ�ֱƫ�D���ϣ�T�ļ�늘O늉���ˮƽ�Ŵ��ӵ�ʾ���ܵ�ˮƽƫ�D���ϡ���ʩ�ӵ��A������͒���늉������Ե��؏ͳ��F�r�����O��ݔ�����������Ϳ����@ʾ��ʾ�����ϡ�

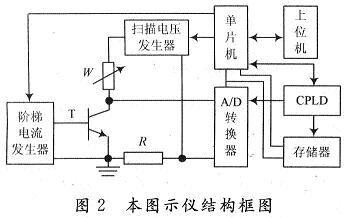

����1��2 ���Dʾ�x�Y����D

�������Dʾ�x�Ę���Ҋ�D2���c�D1��Ȳ�ͬ���ǣ�����ֱ�Ŵ���ˮƽ�Ŵ͡�ʾ���ܡ�ȡ���ˣ��书������λ�C�Г���ͬ�r�����ˆ�Ƭ�C��CPLD���惦����A��D�D�Q���Ȳ������M�ɔ����ɼ��·�������r��λ�C���Ƭ�C�l�������ɼ������Ƭ�Cͨ�^�A������l������T�Ļ��Oʩ���A�������̖��ͨ�^����늉��l������T�ļ�늘O��·ʩ�Ӓ���늉����c��ͬ�r��CPLD����������A��D�D�Q���ʹ惦�����ٲɼ��ʹ惦늉�������������惦��������M��CPLD���������Ƭ�C�l���ɼ��Y����̖����Ƭ�C�ٌ��惦���еĔ���ͨ�^���ڂ��͵���λ�C�M��̎�����@ʾ��һ�������ĈD����Ҫ����@�ӵ��^�̲��܌��F��

����ԓϵ�y����ʹ��CPLD�ʹ惦��������Ҳ�Ɍ��F�����ɼ��������چ�Ƭ�C�����ٶ������^���������ޕr�g(����늉��������Σ�5 ms)�Ȳɼ����c���^�٣���������ʴ_��ʹ����CPLD�ʹ惦��֮�ɵõ��c���ܼ������������挍����ϵ�y���P�I���OӋCPLD���������Խ�Q��Ƭ�C���惦����A��D�D�Q��֮�g�ĕr������Pϵ��

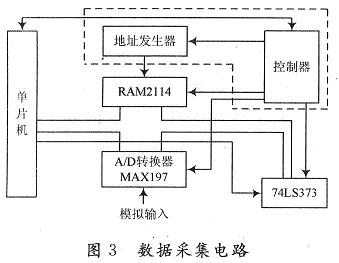

����2 �����ɼ��·����ģ�K�_��

���������ɼ��·�Ę�����D3��ʾ�����˰�����Ƭ�C�����������惦������A��D�D�Q���⣬߀�е�ַӋ�����͔����i������

����2��1 A��D�D�Q���͔����i����

����A��D�D�Q���ǔ����ɼ��·��Ҫ�IJ���֮һ����ϵ�y��A��D�D�Q������Maxim��˾��MAX197��

����MAX197��һ������̵�12λA��D�D�Q����8·ģ�M��̖ݔ�룬ݔ��������8�l���֞��4λ�͵�8λݔ������HBEN�˿��ơ����r��l�ʞ�2 MHz�r���D�Q�r�g��6��s��MAXl97�چ����D�Q�r����Ҫݔ��һ��8λ�����֣��@�����������Ɇ�Ƭ�C�ṩ��ʹ���ӕr�g���L���y����߲ɼ��ٶȣ������@���õ�һ�������i����74LS373����������֡�

����2��2 �惦���͵�ַ�l����

�����惦�����Ã�Ƭ2114,����һ��4 b��1K�o�B�S�C�惦����2114�ڴ�ȡ�����r��������Ҫ�ⲿ�ṩƬ�x��̖���x����̖�⣬߀��Ҫ�ṩ��ַ��̖����ַ��̖�ɵ�ַ�l�����a������ַ�l�������H����һ��Ӌ������

����2��3 ������

�����������ǔ����ɼ��·�ĺ��ģ���CPLD�Ȳ�ģ�K���F���@���CPLD�x��Altera��˾��EPM7064��EPM7064��64�����Ԫ��1 250�������T�36��I��O�_���Ŀ����Է�����f��RAM����ַ�l������74LS373�Ϳ�����������ͬ�r����CPLD�У���RAM��Ҫ100��������CPLD�팍�F��ռ�ô����YԴ���HһƬEPM7064�Ͳ����á����Ԟ��˹�ʡ�YԴ�����ͳɱ����@��������RAM2114��74LS373Ҳ������ӷ�ʽ����Ҫ�ǿ��]�˿ڲ����á������CPLD�Ȳ��H�����˿������͵�ַ�l����(�D3̓�����)��

��3 �������Y���OӋ

����3��1 �ɼ��c���Ĵ_�����������ӿ�Ҫ��

�������w�����������У�ݔ����������������s�ġ�ݔ����������һ����8��10�l���M�ɡ��ڱ�ϵ�y�У�ÿ�l����50���c�B�Ӷ��ɡ�ÿ���c��һ��늉�ֵ��_�����ֵ�_����ÿ��늉�(�����)����ռ���ֹ��惦��Ԫ(������12λ)���tÿ�l������늉�ֵ(�����ֵ)��ռ100���ֹ���늉�ֵ�����ֵ����ԓ��ͬһ�r�̲ɼ��������˹�ʡA��D�D�Q��������Ӳ�����@���늉�����������ڲ�ͬ�Ē������ڃȲɼ���ֻҪ�ɼ��r�g�c���ԵĒ���������ʼ�r�g�g��һһ�����Ϳ��Ա��C���ȣ��r�g�`����1��s֮�ȡ�

����ÿһ�M늉�����������IJɼ�������һ������늉��������r�g����ɡ�����늉��ǰ�50 Hz����늉��������a��������ÿ������늉���ռ�r�g��10 ms������늉��������Εr�g����5ms�����5 ms�r�g��Ҫ�ɼ�50���������tÿ������ռ�Õr�g��100��s��10�l������ռ��20���������ڡ�

������ÿ�������ɼ��r�g(100��s)�ȣ����������ȏ��i����74LS373���xȡ�������֡�����A��D�D�Q��������A��D�D�Q���������M���D�Q�ȴ���B�����D�Q�Y���r����������A��D�D�Q���քe�xȡ�����ĸ��ֹ��͵��ֹ�����RAM�У�Ȼ��ȴ���һ���ɼ����ڡ���50�������ɼ��Y�����������Ƭ�C�l���ɼ��Y����̖�����Կ�����Ҫ�a��74LS373���x��̖��A��D�D�Q����Ƭ�x���x����̖���惦��Ƭ�x���x����̖����ַ�l�����ĕr犺�������̖�ȣ�߀Ҫ���܆�Ƭ�C�IJɼ�ָ����̖��50 Hz�����ͬ����̖�����؆�Ƭ�C�ɼ��Y����̖�ȡ�

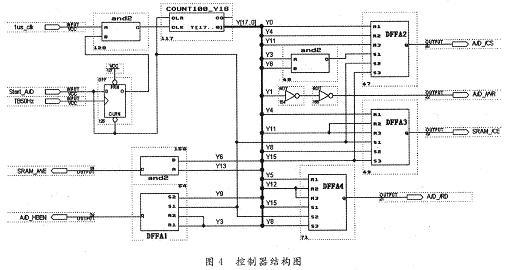

����3��2 �������Ȳ�����

�����������Ȳ�(Ҋ�D4)��Ҫģ�K��Ӌ�������}�_���������|�l����Ӌ������100�M�ƣ�ݔ��r����ڞ�1��s���@��Ӌ����Ӌ�Mһ��ѭ�h����100��s(��һ�������ɼ��ĕr�g)���}�_�������������nj�100 ��s�ȵĕr�g���M�м��֣�ʹÿ1��s�r�g������ݔ���}�_(������Ҫ)���|�l�����}�_�������|�l�a�����⌒�ȵ��}�_(Ҋ�D5)���D��COUNT100_Y18ģ�K���F��100�M��Ӌ�������}�_�������Ĺ��ܣ�DFFA1��DFFA4��������D�|�l��ģ�K��DFFA2��R1��R3����0�ˣ�S1��S3����1�ˣ�DFFA2��DFFA3��DFFA4�Y����ͬ��

�����B��RAM�Ŀ�����̖�Ѓɂ������x����̖SRAM_OE��Ƭ�x��̖SRAM_WE���B��A��D�D�Q���Ŀ�����̖��4������Ƭ�x��̖A��D_CE������̖A��D_WR���x��̖A��D_RD�ߵ��ֹ��x����̖A��D_HEEN����ַӋ������74LS373�i�����Ŀ�����̖ҲҪ�c�����r����ϡ�

����3��3 �����������^��

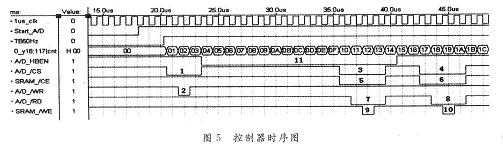

����������ݔ���˕r��D��D5��ʾ����Ƭ�C�����i��������һ�������֣��O��ݔ��ģ�Mͨ����ݔ��ͨ�����̡����ģʽ�̓���r��x�����Ϣ��Ȼ����������l���ɼ�ָ��(Start_A��D׃����ƽ)��������늉�����r(�D��TB50 Hz׃����ƽ)��COUNT100_Y18�_ʼӋ����ݔ���}�_��ͨ�^�|�l���ڲ�ͬ�r�g�a����ͬ���ȵ��}�_��COUNT100_Y18�ĵ�1��4���}�_�a��A��D�D�Q��Ƭ�x��̖A��D_CS��74LS373�x��̖(�D5����1)����2���}�_�a��A��D�D�Q������̖A��D_WR(�D5����2)����74LS373�Ĕ�������MAX197������A��D�_ʼ�D�Q�����D�Q�Y��(��8���}�_�Y���D�Q)��COUNT100_Y18�ĵ�10H��14H�}�_�a��A��D�D�Q��Ƭ�x��̖A��D_CS��RAM2Ƭ�x��̖SRAM_CE(�D5����3��5)����11H��14H�}�_�a��A��D�D�Q�����x��̖A��D_RD(�D5����7)����15H�}�_��A��D_HEEN�Þ���ƽ���xͨ�����ĸ��ֹ�������17H��1BH�}�_�ٴήa��A��D_CS��SRAM_CE��A��D_RD��SRAM_WE(�D5����4��6��8��10)���є����ĸ�4λ����惦���С��@��һ�������IJɼ�����Y����

�������r�g�_100��s�r���؏������^�̣��M����һ�������IJɼ�����RAM��M100���ֹ����������Ƭ�C���زɼ��Y����̖����Ƭ�Cͨ�^���ڌ�100���ֹ��Ĕ����������f�o��λ�C��

����4 �Y �Z

�������OӋ�^���У�������VHDL�Z�Ծ���COUNT100_Y18��DFFA1��DFFA4��ģ�K����Max+Plus���g�ͷ���ͨ�^�����B�Ӹ�ģ�K�γ�플ӈD���ļ�(�D5)����플ӈD���ļ����M�о��g�ͷ��棬ͨ�^�������d��оƬ�С���Ƭ�C��Ҫ�����@ʾ�����A������ӳ���ʹ���ͨ�ų����{ԇͨ�^����λ�C������VB�Z�Ԍ��F�������������^�����Ʒ��㡣�YՓ��������CPLD���g���ڸ�����y���w�܈Dʾ�x��Ч�������@�ģ��x�������кܴ���ߡ�