����FPGA�Ĕ����ɼ�����ģ�K�OӋ

��0 �� ��

���������ɼ��Ϳ���ϵ�y�nj����a�^�̻�ƌW����и��N�������M�Ќ��r�ɼ����yԇ�ͷ������Ƶ��]�h���ƣ����ڹ��I���ơ�܊������O�䡢�t�W�O�o���S���I��l�]����Ҫ���á����У������ɼ������Ȟ���Ҫ�������y�Ĕ����ɼ�ϵ�y��ͨ�����Æ�Ƭ�C��DSP��������������Կ���ADC���惦������������·�Ĺ�����ʹ�òɼ��ٶȺ�Ч�ʽ��͡����������Ӽ��g���磺��Ҏģ�����·�ͳ���Ҏģ�����·���g�İlչ���锵���ɼ�ϵ�y�İlչ�ṩ�����õ����|���A���Ķ�ʹ������ģ�K���͆�Ƭ���lչ��ʹ����ܛ�����r���Z�Ժ�ܛ��ģ�K���lչ���ӿ���˜ʻ��lչ������FPGA�r��l�ʸߣ��Ȳ��ӕrС��ȫ������߉����Ӳ����ɣ��ٶȿ죬Ч�ʸߣ�ͬ�r���зdz������Ӳ�������Z�Ժͷ��湤�ߣ�����z�Y�������_�ԡ��������Ͽ��]�����OӋ�в���FPGA�������̎��������VGA�ӿڵ��OӋ����ͻ����ԓģ�K�ļ����ԣ������ڲɼ�������ֱ�^���F��

����1 ϵ�y���w�OӋ����

���������Ĕ����ɼ��^��ͨ���ɔ�����ͨ���x�ɘӡ��惦���@ʾ���ɣ��ЕrҲҪ�������M���m����̎�������У�����ģ�K���˺������ã������������̖�a����̎�����ИЌ��@Щ����·�M�������r�ıO�غ������OӋ�^���в���FPGA�������������Ɍ�A��D�D�Q���Ŀ��ƣ������ɼ����Ĕ����惦��һ���Ĵ惦��Ԫ��ͨ�^VGA�ӿڅf�h��������@ʾ�����@ʾ�����w�漰������·�У������ɼ�������Ҫ����ADC0809���锵���ɼ�оƬ����ݔ���ģ�M���M��A��D�D�Q���������沿�֑���6116����惦оƬ���Á�����0809�ɼ��Ĕ��������I���Ʋ�������8�����I������0809���D�Qͨ���x�D���@ʾ����ݔ���˜ʵ�VGA��̖��ʹ��CRT�@ʾ�������@ʾ���r���Ρ��������OӋ�Ќ��ⲿ�����M�п��ƵĿ�����������FPGA��ɵģ�FP-GA�Ĺ������ܴ���������õ�FPGAоƬ��FLEXϵ����30�f�T��EPF10K30��

����2 ����FPGA������ģ�K�Č��F

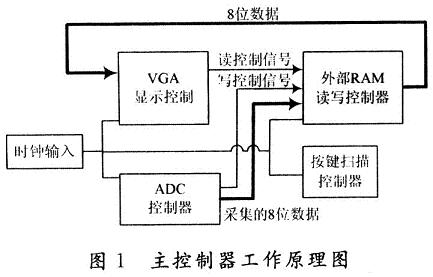

�������������Ĺ���ԭ����D1��ʾ��

����ͨ�^һ��A��D�D�Q�������a����ADC0809�Ŀ�����̖������ADC0809֮���S���͕�����һ���l���M��A��D�D�Q��ͬ�rͨ�^һ�������i����̖�������i�浽A��D�D�Q����ģ�K�С��@���i����̖������RAM��������ݔ�������̖����RAM�x���������Č�������̖��Ч֮���_��RAM�Č�ʹ����Ч��̖�����ɼ����Ĕ�������RAM�ĵ�600����ַ��Ԫ�У�Ȼ��RAM��������RAM�еĔ��������Ƅ�һλ���Ƅ���֮�a��һ�����������ꮅ��̖��֮���ͨ�^�Ȳ���һ��������̖�����S��RAM�x����������RAM���x����ʹ�ܣ�ÿ��VGA�@ʾ�������l��һ���x��������r��RAM�x�����������_��RAM���x��Ч��̖���x��RAM�еĔ���������ͨ�^VGA�������ĕr����ƺ�ݔ����̖�M���@ʾ���ⲿ�İ��I���ֹ���8�����@8�����I����ADC0809��8·ͨ�����x���I�P�������Ĺ��ܾ��ǒ��������°��I���к���ֵ�����Һϳ��Iֵ���D�Q�ɰ��I��ֵ0��7����K����8��ģ�Mݔ��ͨ�����x��

����2��1 VGA�@ʾ���������OӋ

������Ҋ�IJ�ɫ�@ʾ��һ����ꎘO�侀��(CRT)���ɣ���ɫ���ɼt���S���{(R��G��B)����ɫ�M�ɵģ������В���ķ�ʽ��Q�D���@ʾ��������������5����̖��R��G��B����ɫ��̖��HS����ͬ����̖��VS����ͬ����̖��

��������VGA�@ʾ�����@�傀��̖�ĕr����Ҫ������ѭ��VGA���I�˜ʡ�����640��480��60ģʽ����t���p��VGA�@ʾ�����ڴˣ�����������2��ݔ����̖��6��ݔ����̖��CLK�B�ӵ��ⲿ�ľ����ϣ��侧���l����50 MHz������VGA���I�˜���Ҫ��ľ����l����25 MHz����ˣ��ڴ˿�����������Ҫ���r��M�ж����l��RD��һ��8λ�Ĕ������������Տ�RAM�x���Ĕ�����ݔ����̖READ���ڿ���RAM����ģ�K�_��RAM���x��Ч��̖��ֻҪREAD��׃������ô���M���x������B����RD�����x�����Ĕ�����HS��VS�քe����ͬ����̖�͈�ͬ����̖��R��G��B�����lݔ������̖�����@ʾ������ͨ�^��׃R��G��B�@���lݔ����̖��ֵ�팍�F�ġ�

����ÿ�x��һ���������䌍�nj�����һ�������c�������@�����ɼ���늉�ֵ������0��5 V������ADC0809�D�Q�ɵĔ�������0x00��0xFF�����������OӋ�rֻҪ��RD���յľ��w��ֵ�c�@ʾ���е�ijһ�����������ɣ����w���F�ñ��^�Z��Ϳ��Ԍ��F�ж�λ��ͬ�r���o���Ĵ���LLV��1���ɣ��@�Ӽ��Ɍ��F�B�m���Ρ��@Щ�c�B����������һ�������IJ��Σ���������ͬ���͈�ͬ����̖�Įa���t�քe�ɃȲ���̖CC��LL������֪��ݔ��r犣�ͨ�^Ӌ����Ӌ���ķ�ʽ���_�����I�˜�Ҫ����l�ʡ�

����2��2 A��D�D�Q���������OӋ

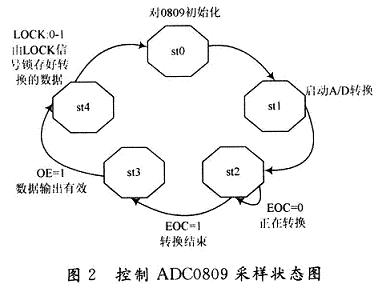

�����ڴ��OӋ�У������à�B�C��A��D�D�Q�M�п��Ƶġ�����ADC0809�ɘӠ�B�D����D2��ʾ��

�����ڠ�BST0�У���0809�M�г�ʼ����֮���M�뵽��BST1���ڠ�BST1�У�ALE��START��̖��Ч���@�rEOC��̖׃����ƽ���M���D�Q��BST2���˕r����Ҫ��0809������B��̖EOC�M�Мyԇ���������ƽ����ʾ�D�Q�]�Y��������Ҫͣ����ST2��B�еȴ���ֱ��׃�ɸ��ƽ����f���D�Q�Y��������һ�r��}�_����r�D���BST3���ڠ�BST3���ɠ�B�C��0809�l���D�Q�õ�8λ����ݔ�����S����@һ��B����ͬ�r�����锵��ݔ���������ڣ��Ա�������һ��B�����i�������i��ɿ��Ĕ������ڠ�BST4���ɠ�B�C��FPGA�е��i�����l���i����̖����0809ݔ���Ĕ����M���i�档

��2��3 RAM�x�����������OӋ

������ԓģ�K�OӋ�У�RAM�x������ģ�K�ַ֞��x����ģ�K��������ģ�K���x����B�D�Qģ�K��������ģ�K�Ѓɂ�ݔ����̖�քe�cA��D�D�Q����ģ�K�Ĕ����i����D�Qݔ�����B�����i����̖ʹ�ܣ����l������̖���������惦���ⲿRAM�ĵ�600����ַ���g֮���ٌ�֮ǰ�Ĕ����M��ǰ�ƣ����_�������ļ��r���¡��x����ģ�K�Ŀ�����̖�քe�c�������ꮅ��̖���x��̖���B�����������ꮅ��̖ʹ�ܕr��ֻҪ�ӵ��x��̖���t�����x���ⲿRAMǰ600����ַ���g(һ��)�Ĕ�����

����2��4 �I�P������������OӋ

�����I�P����ģ�K���Ă�ģ�K�M�ɣ��������r犷��lģ�K�����Iֵݔ��ģ�K���Iֵ�i��ģ�K���Iֵ�ϳ�ģ�K���Iֵ�i��ģ�K�����°��I���С�����Ϣ�i�棬�������Iֵ�ϳ�ģ�K��ԓģ�K������Iݔ��ģ�Kݔ���ĽY���M�в������K�_���Iֵ��

����3 ����Y��

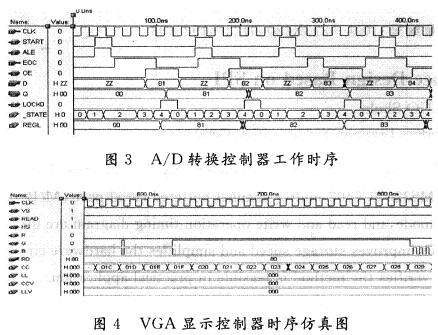

����Max+Plus�����ƽ�_�ĈD��ݔ�뷽ʽֱ�^�����ς��y����ϵ�y�OӋ�ˆT�����T�������M�нӿڵ��OӋ�������F���棬������̖���^�졣�������Ͽ��]�����ô�ƽ�_����Ӳ�������Z��VHDL�팍�F��������ģ�K��A��D�D�Q��������VGA�@ʾ������ģ�K�ĕr�����Y����D3���D4��ʾ��

����4 �Y �Z

�����@��Ĕ����ɼ�����ģ�K��Ҫ��FPGA����A������ܛ��Ӳ������˼·�������о�������ģ�K�Č��F�����ڲ���FPGA�������̎���������ٶȿ죬Ч�ʸߣ��Ҙ˜ʵ�VGA�ӿ�ʹ��ϵ�y��ʹ�ø��ӱ�ݣ��I�P���ƵĶ�ͨ���g�ГQ��Ҳ�錍�F��·�ɼ��춨�˻��A��

<-- 2010/2/6 10:17:12-->