dds技術是什么

dds簡介:

DDS是直接數字式頻率合成器(Direct Digital Synthesizer)的英文縮寫,是一項關鍵的數字化技術。與傳統的頻率合成器相比,DDS具有低成本、低功耗、高分辨率和快速轉換時間等優點,廣泛使用在電信與電子儀器領域,是實現設備全數字化的一個關鍵技術。

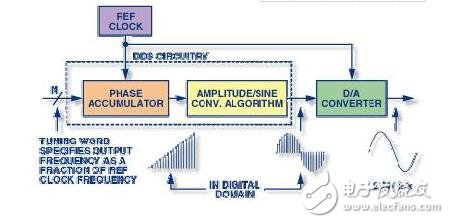

DDS芯片中主要包括頻率控制寄存器、高速相位累加器和正弦計算器三個部分(如Q2220)。頻率控制寄存器可以串行或并行的方式裝載并寄存用戶輸入的頻率控制碼;而相位累加器根據dds頻率控制碼在每個時鐘周期內進行相位累加,得到一個相位值;正弦計算器則對該相位值計算數字化正弦波幅度(芯片一般通過查表得到)。DDS芯片輸出的一般是數字化的正弦波,因此還需經過高速D/A轉換器和低通濾波器才能得到一個可用的模擬頻率信號。

另外,有些DDS芯片還具有調幅、調頻和調相等調制功能及片內D/A變換器(如AD7008)。

dds優點:

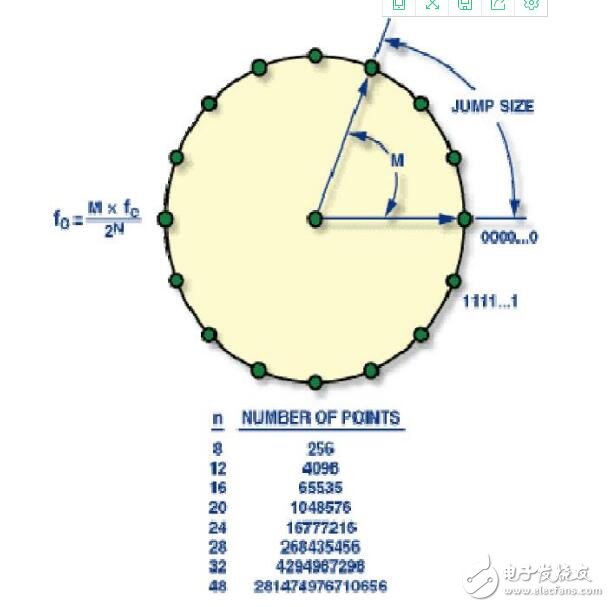

頻率分辨率高、輸出頻點多、可達2的N次方個頻點(N為相位累加器位數);

頻率切換速度快,DDS是一個開環系統,無任何反饋環節,因而頻率轉換時間極短,可達ns量級;

頻率切換時相位連續;

可以輸出寬帶正交信號;

輸出相位噪聲低,對參考頻率源的相位噪聲有改善作用;

可以產生任意波形;全數字化實現、便于集成、體積小、重量輕。

在各行各業的測試應用中,信號源扮演著極為重要的作用。但信號源具有許多不同的類型,不同類型的信號源在功能和特性上各不相同,分別適用于許多不同的應用。波形發生器,函數發生器,RF信號源,以及基本的模擬輸出模塊。信號源中采用DDS技術在當前的測試測量行業已經逐漸稱為一種主流的做法。

DDS工作原理

Error! Reference source not found. 是DDS 的內部結構圖,它主要分成3 部分:相位累加器,相位幅度轉換,數模轉換器(DAC)。

相位累加器

一個正弦波,雖然它的幅度不是線性的,但是它的相位卻是線性增加的。

DDS 正是利用了這一特點來產生正弦信號。如圖 2,根據DDS 的頻率控制字的位數N,把360° 平均分成了2的N次等份。

圖2,相位累加器原理

假設系統時鐘為Fc,輸出頻率為Fout。每次轉動一個角度360°/2N, 則可以產生一個頻率為Fc/2N 的正弦波的相位遞增量。那么只要選擇恰當的頻率控制字M,使得 Fout / Fc= M / 2N,就可以得到所需要的輸出頻率Fout,

Fout = Fc*M / 2N,相位幅度轉換通過相位累加器,我們已經得到了合成Fout 頻率所對應的相位信息,然后相位幅度轉換器把0°~360°的相位轉換成相應相位的幅度值。比如當DDS 選擇為2V p-p 的輸出時,45°對應的幅度值為0.707V,這個數值以二進制的形式被送入DAC。這個相位到幅度的轉換是通過查表完成的。

DAC 輸出代表幅度的二進制數字信號被送入DAC 中,并轉換成為模擬信號輸出。注意DAC 的位數并不影響輸出頻率的分辨率。輸出頻率的分辨率是由頻率控制字的位數決定的。

直接數字式頻率合成技術(DDS)是一種先進的全數字頻率合成技術,它具有多種數字式調制能力(如相位調制、頻率調制、幅度調制以及I/Q正交調制等),在通信、導航、雷達、電子戰等領域獲得了廣泛的應用。在項目中光柵傳感系統高頻并行解調算法的FPGA實現我們的光纖通信模塊用到DDS。我們通過FPGA 實現了DDS的功能。

1971年,美國學者J.Tierney等人撰寫的《A Digital Frequency

Synthesizer》一文首次提出了以全數字技術,從相位概念出發直接合成所需波形的一種新的頻率合成原理。限于當時的技術和器件水平,它的性能指標尚不能與已有的技術相比,故未受到重視。近10年間,隨著微電子技術的迅速發展,直接數字頻率合成器(Direct Digital Frequency Synthesis簡稱DDS或DDFS)得到了飛速的發展,它以有別于其它頻率合成方法的優越性能和特點成為現代頻率合成技術中的佼佼者。具體體現在相對帶寬寬、頻率轉換時間短、頻率分辨率高、輸出相位連續、可產生寬帶正交信號及其他多種調制信號、可編程和全數字化、控制靈活方便等方面,并具有極高的性價比。

DDS基本原理及性能特點

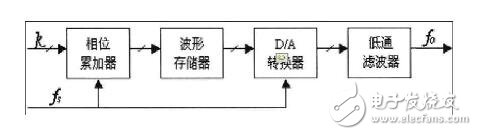

DDS的基本原理是利用采樣定理,通過查表法產生波形。DDS的結構有很多種,其基本的電路原理如圖所示。

相位累加器由N位加法器與N位累加寄存器級聯構成。每來一個時鐘脈沖fs,加法器將頻率控制字k與累加寄存器輸出的累加相位數據相加,把相加后的結果送至累加寄存器的數據輸入端。累加寄存器將加法器在上一個時鐘脈沖作用后所產生的新相位數據反饋到加法器的輸入端,以使加法器在下一個時鐘脈沖的作用下繼續與頻率控制字k相加。這樣,相位累加器在時鐘作用下,不斷對頻率控制字進行線性相位累加。由此可以看出,相位累加器在每一個時鐘脈沖輸入時,把頻率控制字累加一次,相位累加器輸出的數據就是合成信號的相位,相位累加器的溢出頻率就是DDS輸出的信號頻率。

用相位累加器輸出的數據作為波形存儲器(ROM)的相位取樣地址,這樣就可把存儲在波形存儲器內的波形抽樣值(二進制編碼)經查找表查出,完成相位到幅值轉換。波形存儲器的輸出送到D/A轉換器,D/A轉換器將數字量形式的波形幅值轉換成所要求合成頻率的模擬量形式信號。低通濾波器用于濾除不需要的取樣分量,以便輸出頻譜純凈的正弦波信號。

DDS在相對帶寬、頻率轉換時間、高分辨力、相位連續性、正交輸出以及集成化等一系列性能指標方面遠遠超過了傳統頻

非常好我支持^.^

(317) 99.1%

不好我反對

(3) 0.90000000000001%

相關閱讀:

- [電子說] 為什么DDR3/4不需要設置input delay呢? 2023-09-11

- [電子說] XILINX FPGA IP之DDS Compiler_ip例化仿真 2023-09-07

- [電子說] 如何判定雜散來源? 2023-09-04

- [電子說] 直接數字合成技術(DDS)是什么?DDS又是如何工作的? 2023-08-24

- [電子說] DDS-IP核的理論知識和應用案例 2023-08-22

- [電子說] FPGA和DDS在信號源中的應用 2023-07-24

- [電子說] Xilinx Vivado DDS IP使用方法 2023-07-24

- [汽車電子] 基于ADAS自動泊車功能的DDS協議的系統設計 2023-07-14

( 發表人:姚遠香-老賬號 )