TTL和非門的基本結構及工作原理是什么?

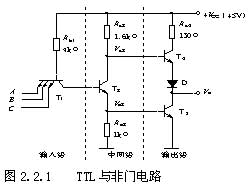

1.TTL與非門的基本結構

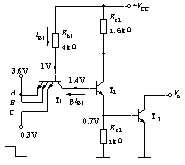

我們以DTL與非門電路為基礎,根據提高電路功能的需要,從以下幾個方面加以改進,從而引出TTL與非門的電路結構。

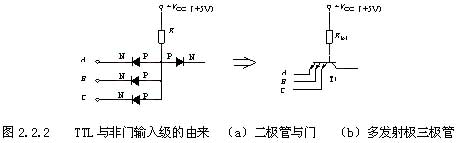

首先考慮輸入級,DTL是用二極管與門做輸入級,速度較低。仔細分析我們發現電路中的Dl、D2、D3、D4的P區是相連的。我們可用集成工藝將它們做成—個多發射極三極管。這樣它既是四個PN結,不改變原來的邏輯關系,又具有三極管的特性。一旦滿足了放大的外部條件,它就具有放大作用,為迅速消散T2飽和時的超量存儲電荷提供足夠大的反向基極電流,從而大大提高了關閉速度。詳細情況后面再講。

第二,為提高輸出管的開通速度,可將二極管D5改換成三極管T2,邏輯關系不變。同時在電路的開通過程中利用T2的放大作用,為輸出管T3提供較大的基極電流,加速了輸出管的導通。另外T2和電阻RC2、RE2組成的放大器有兩個反相的輸出端VC2和VE2,以產生兩個互補的信號去驅動T3、T4組成的推拉式輸出級。

第三,再分析輸出級。輸出級應有較強的負載能力,為此將三極管的集電極負載電阻RC換成由三極管T4、二極管D和RC4組成的有源負載。由于T3和T4受兩個互補信號Ve2和Vc2的驅動,所以在穩態時,它們總是一個導通,另一個截止。這種結構,稱為推拉式輸出級。

2.TTL與非門的邏輯關系

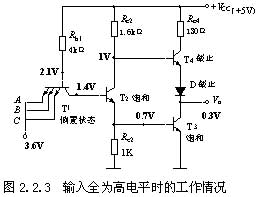

因為該電路的輸出高低電平分別為3.6V和0.3V ,所以在下面的分析中假設輸入高低電平也分別為3.6V和0.3V。

(1)輸入全為高電平3.6V時。T2 、T3導通,VB1=0.7×3=2.1(V),從而使T1的發射結因反偏而截止。此時T1的發射結反偏,而集電結正偏,稱為倒置放大工作狀態。

由于T3飽和導通,輸出電壓為:VO=VCES3≈0.3V

這時VE2=VB3=0.7V,而VCE2=0.3V,故有VC2=VE2+ VCE2=1V。1V的電壓作用于T4的基極,使T4和二極管D都截止。

可見實現了與非門的邏輯功能之一:輸入全為高電平時,輸出為低電平。

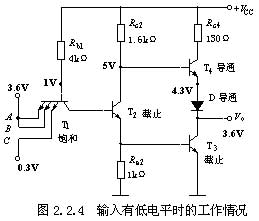

(2)輸入有低電平0.3V時。

該發射結導通,T1的基極電位被鉗位到VB1=1V。T2、T3都截止。由于T2截止,流過RC2的電流僅為T4的基極電流,這個電流較小,在RC2上產生的壓降也較小,可以忽略,所以VB4≈VCC=5V ,使T4和D導通,則有:

VO≈VCC-VBE4-VD=5-0.7-0.7=3.6(V)

可見實現了與非門的邏輯功能的另一方面:輸入有低電平時,輸出為高電平。

綜合上述兩種情況,該電路滿足與非的邏輯功能,是一個與非門。

TTL與非門的開關速度:

1.TTL與非門提高工作速度的原理

(1)采用多發射極三極管加快了存儲電荷的消散過程。設電路原來輸出低電平,當電路的某一輸入端突然由高電平變為低電平,T1的一個發射結導通,VB1變為1V。由于T2、T3原來是飽和的,基區中的超量存貯電荷還來不及消散,VB2仍維持1.4V。在這個瞬間,T1為發射結正偏,集電結反偏,工作于放大狀態,其基極電流iB1=(VCC-VB1)/Rb1

圖2.2.5 多發射極三極管消散T2存儲電荷的過程

集電極電流iC1=β1iB1。這個iC1正好是T2的反向基極電流iB2,可將T2的存貯電荷迅速地拉走,促使T2管迅速截止。T2管迅速截止又使T4管迅速導通,而使T3管的集電極電流加大,使T3的超量存貯電荷從集電極消散而達到截止。

(2)采用了推拉式輸出級,輸出阻抗比較小,可迅速給負載電容充放電。

2.TTL與非門傳輸延遲時間tpd

當與非門輸入一個脈沖波形時,其輸出波形有一定的延遲,如圖所示。定義了以下兩個延遲時間:

導通延遲時間tPHL——從輸入波形上升沿的中點到輸出波形下降沿的中點所經歷的時間。

截止延遲時間tPLH——從輸入波形下降沿的中點到輸出波形上升沿的中點所經歷的時間。

與非門的傳輸延遲時間tpd是tPHL和tPLH的平均值。即

![]()

一般TTL與非門傳輸延遲時間tpd的值為幾納秒~十幾個納秒。

非常好我支持^.^

(98) 90.7%

不好我反對

(10) 9.3%

相關閱讀:

- [電子說] TTL與BJT的基礎知識 2023-10-21

- [電子說] 雙通道低邊門極驅動芯片BTL2752系列簡介 2023-10-20

- [電子說] 什么叫做LVDS信號?請問TTL信號與LVDS信號有什么區別? 2023-10-18

- [電子說] 邏輯電平測試筆設計方案 2023-10-18

- [電子說] TTL集成邏輯門的邏輯功能與參數測試實驗 2023-10-11

- [電子說] 催化劑利用率提高237倍!首次電化學生長超低負載鉑納米片超薄電極 2023-10-11

- [電子說] TTL邏輯門電路參數測試 2023-10-10

- [電子說] 一文詳解分立器件及數字集成電路 2023-10-07

( 發表人:admin )