本的二進制加法/減法器,本的二進制加法/減法器原理

兩個二進制數字Ai,Bi和一個進位輸入Ci相加,產生一個和輸出Si,以及一個進位輸出Ci+1。

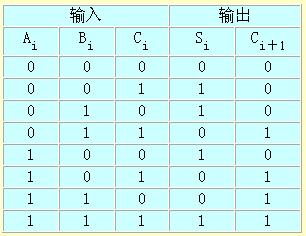

表2.2中列出一位全加器進行加法運算的輸入輸出真值表。

表2.2 一位全加器真值表圖

根據表2.2所示的真值表,三個輸入端和兩個輸入端可按如下邏輯方程進行聯系:

Si=Ai⊕Bi⊕Ci

??? Ci+1=AiBi+BiCi+CiAi??????? (2.23)

按此表達式組成的一位全加器示圖2.2,求和部分Si由兩個異或門組成,進位部分Ci+1由與非門組成。

圖2.2 一位全加器(FA)單元

補碼運算的二進制加法/減法器的邏輯結構圖

由圖看到,n個1位的全加器(FA)可級聯成一個n位的行波進位加減器。M為方式控制輸入線,當M=0時,作加法(A+B)運算;當M=1時,作減法(A-B)運算,在后一種情況下,A-B運算轉化成[A]補+[-B]補運算,求補過程由B+1來實現。因此,圖中最右邊的全加器的起始進位輸入端被連接到功能方式線M上,作減法時M=1,相當于在加法器的最低位上加1。另外,圖中左邊還表示出單符號位法的溢出檢測邏輯;當Cn=Cn-1時,運算無溢出;而當Cn≠Cn-1時,運算有溢出,經異或門產生溢出信號。

對一位全加器(FA)來說,Si的時間延遲為6T(每級異或門延遲3T),Ci+1的時間延遲為5T,其中T被定義為相應于單級邏輯電路的單位門延遲。T通常采用一個“與非”門或一個“或非”門的時間延遲來作為度量單位。

現在我們計算一個n位的行波進位加法器的時間延遲。假如采用圖2.2(a)所示的一位全加器并考慮溢出檢測,那么n位行波進位加法器的延遲時間ta為

ta=n·2T+9T=(2n+9)T??????? (2.22)

9T為最低位上的兩極“異或”門再加上溢出“異或”門的總時間,2T為每級進位鏈的延遲時間。

當不考慮溢出檢測時,有

ta=(n-1)·2T+9T (2.23)

ta意味著加法器的輸入端輸入加數和被加數后,在最壞情況下加法器輸出端得到穩定的求和輸出所需的最長時間。顯然這個時間越小越好。注意,加數、被加數、進位與和數都是用電平來表示的,因此,所謂穩定的求和輸出,就是指穩定的電平輸出。

非常好我支持^.^

(34) 64.2%

不好我反對

(19) 35.8%

相關閱讀:

- [電子說] 什么是奇校驗和偶校驗?常見的奇偶校驗方式有哪些? 2023-10-17

- [電子說] IPv6地址如何劃分?這篇文章看完必懂! 2023-10-17

- [電子說] 開放二進制翻譯聯盟,推動RISC-V實現跨架構應用運行 2023-10-17

- [電子說] 用D觸發器構成異步二進制加/減計數器 2023-10-11

- [電子說] Redis數據類型介紹 2023-10-09

- [電子說] 如何使用位操作符實現低級別的位掩碼 2023-10-07

- [電子說] ADC碼值的轉換過程講解 2023-09-25

- [電子說] 為什么rs觸發器可以消除機械抖動 2023-09-21

( 發表人:admin )