跳頻通信中的抗干擾同步算法研究

0 引言

復雜電磁環境下的現代戰場上,存在著很多人為干擾,這些有針對性的干擾信號會嚴重地影響我方在戰場上的信息傳輸。現今對抗干擾的方法有擴頻通信、信道糾錯編碼等技術。其中作為擴頻通信中的跳頻通信,以其抗干擾、抗衰落、抗截獲等優良性能,在軍事通信中有著及其重要的地位。

跳頻通信中,跳頻同步策略對于系統的性能指標有著極大的影響,是系統可靠性的關鍵所在。由于跳頻同步策略中用到的頻點數量相對隨機跳的頻點數量少得多,而且由于其重復性很高,極易受到敵方的偵測和干擾,給系統的可靠性帶來極大的隱患。通常的同步頭法和自同步法的跳頻同步策略,很難抵抗敵方的單音和多音干擾,而精確時鐘法易受時鐘漂移的影響,同步的精度不夠,不利于在可靠性要求極高的軍用通信中使用。

在敵方偵測到我同步跳頻點并開始加以干擾的過程中,我方有少許時間是可以有效通信的,故我方認為對于最先接收到的信息給予較高的信任度,在后續的信號處理中起到很重要的作用;同時我方需要能夠僅用幾位有效的頻點信息就能夠完成同步跳轉隨機跳的工作(跳頻同步),其余信息可以作為剔出干擾的校驗信息,故設計策略要求在獲得較少的有效頻點峰值信息的情況下,可以有效地完成跳頻同步工作的要求,所以需要在同步頭序列中加入定位信息。

1 跳頻同步頭的設計

為了完成提出的在獲得較少有效頻點峰值信息的情況下,可以有效地完成跳頻同步工作,需要設計發送端同步跳的跳頻序列。

若使用跳頻同步搜索方法,接收端在獲得有效頻點峰值信息的時候,可以從中獲得的信息有:

頻點信息,即F1,F2,F3,F4;頻點的前后順序關系,即F1頻點接的是F2頻點,而不是其他頻點;頻點之間的間隔信息,即F1與F3之間的間隔為一跳。

將發送端頻點序列設計成F1,F1,F2,F3,F4,F3,F2,F1,F3,即按照上面的3條信息分析,由此序列中任意的兩個頻點的信息,都完全可以確定它們在此序列的位置。由于發端序列中任意兩個頻點所確定的位置信息是惟一的,故可以推斷出當前收到的頻點信息與同步跳轉隨機跳位置之間的距離,亦可以給出同步跳轉隨機跳的時間信息,這是所需要的,而且以同樣頻點組成的這樣的序列有很多組,可以保證發端同步序列在頻點確定的情況下可以有較大的選擇空間。

2 系統框架

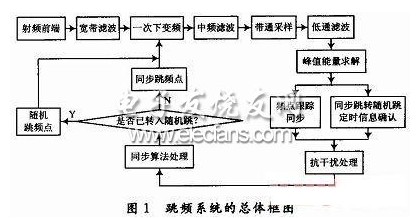

跳頻系統的總體框圖如圖1所示。

其中頻點跟蹤同步、同步跳轉隨機跳定時信息的確定及抗干擾處理是此處提出算法策略的重點。由于本文算法是從接收到能量峰值、頻點值和峰值之間的距離來提取所需要的信息,而不是頻點傳送的調制信息,故本文的算法策略對于調制方式沒有限定,可以很好地和現行的各種調制解調方式相結合。

非常好我支持^.^

(1) 50%

不好我反對

(1) 50%

相關閱讀:

- [PCB設計] PCB設計原則和抗干擾措施 2023-10-18

- [電子說] PLC控制器的主要抗干擾措施 2023-10-18

- [PCB設計] ?電源PCB設計抗干擾、EMC部分指南 2023-10-17

- [電子說] 如何解決PLC控制系統抗干擾問題 2023-10-17

- [電子說] 智能門鎖產品中應用的抗干擾低功耗觸摸感應芯片 2023-10-17

- [電子說] ESD抗干擾測試是什么?防止ESD的常見方法有哪些 2023-10-08

- [電子說] 紅外光學系統抗干擾的主要方法 2023-09-26

- [電子說] X2安規電容在電源中的三大作用,除了抗干擾它還能做什么? 2023-09-22

( 發表人:彭菁 )