8086CPU有哪些寄存器_各有什么用途

8086概述

8086微處理器是Intel公司推出的第三代CPU芯片,它們的內部結構基本相同,都采用16位結構進行操作及存儲器尋址,但外部性能有所差異,兩種處理器都封裝在相同的40腳雙列直插組件(DIP)中。

8086CPU的編程結構

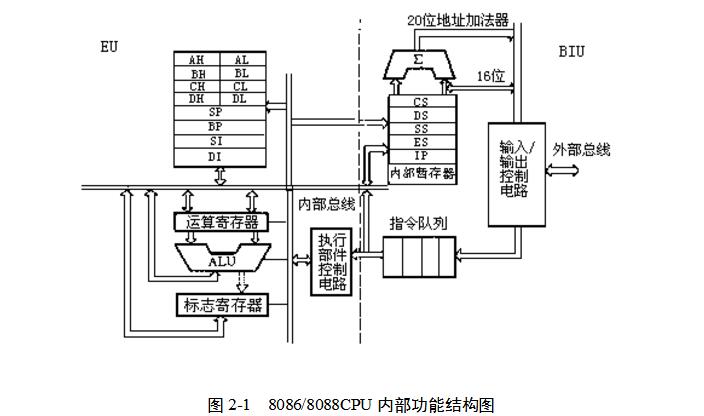

編程結構:是指從程序員和使用者的角度看到的結構,亦可稱為功能結構。如圖2-1所示是8086CPU的內部功能結構。

從功能上來看,8086CPU可分為兩部分,即總線接口部件BIU(BusInterfaceUnit)和執行部件EU(ExecutionUnit)。

(1)執行部件(EU)

功能:負責指令的執行。

組成:包括①ALU(算術邏輯單元)、②通用寄存器組和③標志寄存器等,主要進行8位及16位的各種運算。

(2)總線接口部件(BIU)

功能:負責與存儲器及I/O接口之間的數據傳送操作。具體來看,完成取指令送指令隊列,配合執行部件的動作,從內存單元或I/O端口取操作數,或者將操作結果送內存單元或者I/O端口。

組成:它由①段寄存器(DS、CS、ES、SS)、②16位指令指針寄存器IP(指向下一條要取出的指令代碼)、③20位地址加法器(用來產生20位地址)和④6字節(8088為4字節)指令隊列緩沖器組成。

(3)8086BIU的特點

①8086的指令隊列分別為6/4個字節,在執行指令的同時,可從內存中取出后續的指令代碼,放在指令隊列中,可以提高CPU的工作效率。

②地址加法器用來產生20位物理地址。8086可用20位地址尋址1M字節的內存空間,而CPU內部的寄存器都是16位,因此需要由一個附加的機構來計算出20位的物理地址,這個機構就是20位的地址加法器。

例如:CS=0FE00H,IP=0400H,則表示要取指令代碼的物理地址為0FE400H。

(4)BIU與EU的動作協調原則

總線接口部件(BIU)和執行部件(EU)按以下流水線技術原則協調工作,共同完成所要求的信息處理任務:

①每當8086的指令隊列中有兩個空字節,或BIU就會自動把指令取到指令隊列中。其取指的順序是按指令在程序中出現的前后順序。

②每當EU準備執行一條指令時,它會從BIU部件的指令隊列前部取出指令的代碼,然后用幾個時鐘周期去執行指令。在執行指令的過程中,如果必須訪問存儲器或者I/O端口,那么EU就會請求BIU,進入總線周期,完成訪問內存或者I/O端口的操作;如果此時BIU正好處于空閑狀態,會立即響應EU的總線請求。如BIU正將某個指令字節取到指令隊列中,則BIU將首先完成這個取指令的總線周期,然后再去響應EU發出的訪問總線的請求。

③當指令隊列已滿,且EU又沒有總線訪問請求時,BIU便進入空閑狀態。④在執行轉移指令、調用指令和返回指令時,由于待執行指令的順序發生了變化,則指令隊列中已經裝入的字節被自動消除,BIU會接著往指令隊列裝入轉向的另一程序段中的指令代碼。

從上述BIU與EU的動作管理原則中,不難看出,它們兩者的工作是不同步的,正是這種既相互獨立又相互配合的關系,使得8086可以在執行指令的同時,進行取指令代碼的操作,也就是說BIU與EU是一種并行工作方式,改變了以往計算機取指令→譯碼→執行指令的串行工作方式,大大提高了工作效率,這正是8086獲得成功的原因之一。

(5)8086CPU內部寄存器

8086內部的寄存器可以分為通用寄存器和專用寄存器兩大類,專用寄存器包括指針寄存器、變址寄存器等。

①通用寄存器

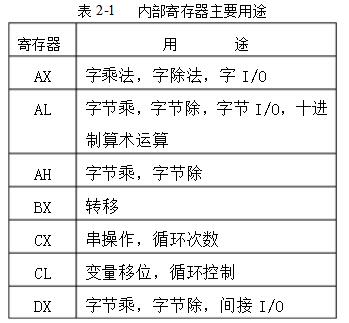

8086有4個16位的通用寄存器(AX、BX、CX、DX),可以存放16位的操作數,也可分為8個8位的寄存器(AL、AH;BL、BH;CL、CH;DL、DH)來使用。其中AX稱為累加器,BX稱為基址寄存器,CX稱為計數寄存器,DX稱為數據寄存器,這些寄存器在具體使用上有一定的差別,如表2-1所示。

②指針寄存器

系統中有兩個16位的指針寄存器SP和BP,其中SP是堆棧指針寄存器,由它和堆棧段寄存器SS一起來確定堆棧在內存中的位臵;BP是基數指針寄存器,通常用于存放基地址。

③變址寄存器

系統中有兩個16位的變址寄存器SI和DI,其中SI是源變址寄存器,DI是目的變址寄存器,都用于指令的變址尋址方式。

④控制寄存器

IP、標志寄存器是系統中的兩個16位控制寄存器,其中IP是指令指針寄存器,用來控制CPU的指令執行順序,它和代碼段寄存器CS一起可以確定當前所要取的指令的內存地址。順序執行程序時,CPU每取一個指令字節,IP自動加1,指向下一個要讀取的字節;當IP單獨改變時,會發生段內的程序轉移;當CS和IP同時改變時,會產生段間的程序轉移。

標志寄存器的內容被稱為處理器狀態字PSW,用來存放8086CPU在工作過程中的狀態。

⑤段寄存器

系統中共有4個16位段寄存器,即代碼段寄存器CS、數據段寄存器DS、堆棧段寄存器SS和附加段寄存器ES。這些段寄存器的內容與有效的地址偏移量一起,可確定內存的物理地址。通常CS劃定并控制程序區,DS和ES控制數據區,SS控制堆棧區。

(6)處理器狀態字PSW

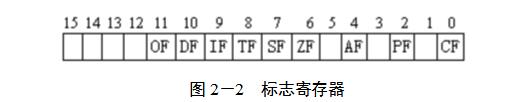

8086內部標志寄存器的內容,又稱為處理器狀態字PSW。其中共有9個標志位,可分成兩類:一類為狀態標志,一類為控制標志。其中狀態標志表示前一步操作(如加、減等)執行以后,ALU所處的狀態,后續操作可以根據這些狀態標志進行判斷,實現轉移;控制標志則可以通過指令人為設臵,用以對某一種特定的功能起控制作用(如中斷屏蔽等),反映了人們對微機系統工作方式的可控制性。

PSW中各標志位的安排如圖2-2所示,這些標志位的含義如下:①狀態標志:6個

CF—進位標志位,做加法時最高位出現進位或做減法時最高位出現借位,該位臵1,反之為0。

PF—奇偶標志位,當運算結果的低8位中l的個數為偶數時,則該位臵1,反之為0。?AF—半進位標志位,做字節加法時,當低四位有向高四位的進位,或在做減法時,低

四位有向高四位的借位時,該標志位就臵1。通常用于對BCD算術運算結果的調整。(例:11011000+10101110=110000110其中AF=1,CF=1)

ZF—零標志位,運算結果為0時,該標志位臵1,否則清0。

SF—符號標志位,當運算結果的最高位為1,該標志位臵1,否則清0。即與運算結果的最高位相同。

OF—溢出標志位,OF溢出的判斷方法如下:

加法運算:

若兩個加數的最高位為0,而和的最高位為1,則產生上溢出;若兩個加數的最高位為1,而和的最高位為0,則產生下溢出;兩個加數的最高位不相同時,不可能產生溢出。

減法運算:

若被減數的最高位為0,減數的最高位為1,而差的最高位為1,則產生上溢出;若被減數的最高位為1,減數的最高位為0,而差的最高位為0,則產生下溢出;被減數及減數的最高位相同時,不可能產生溢出。

如果所進行的運算是帶符號數的運算,則溢出標志恰好能夠反映運算結果是否超出了8位或16位帶符號數所能表達的范圍,即字節運算大于十127或小于-128時,字運算大于十32767或小于-32768時,該位臵1,反之為0。

- 第 1 頁:8086CPU有哪些寄存器_各有什么用途

- 第 2 頁:8086CPU的兩種工作模式

本文導航

非常好我支持^.^

(8) 100%

不好我反對

(0) 0%

相關閱讀:

- [電子說] 學習STM32F103的ADC功能 2023-10-24

- [電子說] 學習STM32F103的DAC功能 2023-10-24

- [電子說] 學習STM32F103的定時器功能 2023-10-24

- [電子說] STM32基礎知識:定時器的PWM輸出功能 2023-10-24

- [電子說] 既然ODR能控制管腳高低電平,為什么還需要BSRR寄存器呢? 2023-10-24

- [電子說] ARM系列-P Channel簡析 2023-10-24

- [控制/MCU] 基于STM32F429芯片的單片機芯片內存映射圖 2023-10-23

- [電子說] 軟硬件交互的角度將中斷的知識梳理 2023-10-22

( 發表人:姚遠香 )