相位累加器原理及累加器代碼

在中央處理器中,累加器(accumulator) 是一種寄存器,用來儲存計算產生的中間結果。如果沒有像累加器這樣的寄存器,那么在每次計算 (加法,乘法,移位等等) 后就必須要把結果寫回到內存,也許馬上就得讀回來。然而存取主存的速度是比從算術邏輯單元到有直接路徑的累加器存取更慢。

標準的例子就是把一列的數字加起來。一開始累加器設定為零,每個數字依序地被加到累加器中,當所有的數字都被加入后,結果才寫回到主存中。

現今的 CPU 通常有很多寄存器,所有或多數都可以被用來當作累加器。因為這個原因,“累加器” 這名詞就顯得有些老舊。這個名詞已經幾乎不在微處理器寄存器中使用,例如,運算寄存器的名稱中的符號以 “A” 開頭的表示是從 “accumulator” 這個歷史因素得來的 (有時候認為并非 “arithmetic”)。也可能混淆的是寄存器的名字前置 “A” 也表示 “address”,比如說像是Motorola 68000家族。

早期的 4 位、8 位微處理器,典型具有單個累加器。8051微控制器有兩個累加器:主累加器與從累加器,其中的從累加器只用于乘法(MUL AB)與除法(DIV AB)。乘法的 16 位結果放入兩個 8 位累加器中。除法時,商放入主累加器,余數放入從累加器。8008的直接后繼產品——8080與8086,開創了x86指令集體系結構,仍然使用兩個累加器:主累加器 EAX 與從累加器 EDX 用于乘法與除法的大數運算。例如,MUL ECX 將把兩個 32 位寄存器 ECX 與 EAX 相乘,64 位結果放入 EAX 與 EDX。但是 MUL 與 DIV 之外的其他算術——邏輯指令(ADD、SUB、CMP、AND、OR、XOR、TEST)可以使用 8 個寄存器:EAX、ECX、EDX、EBX、ESP、EBP、ESI、EDI 作為目的操作數(即存儲結果的位置)。

相位累加器原理

一個正弦波,雖然它的幅度不是線性的,但是它的相位卻是線性增加的。

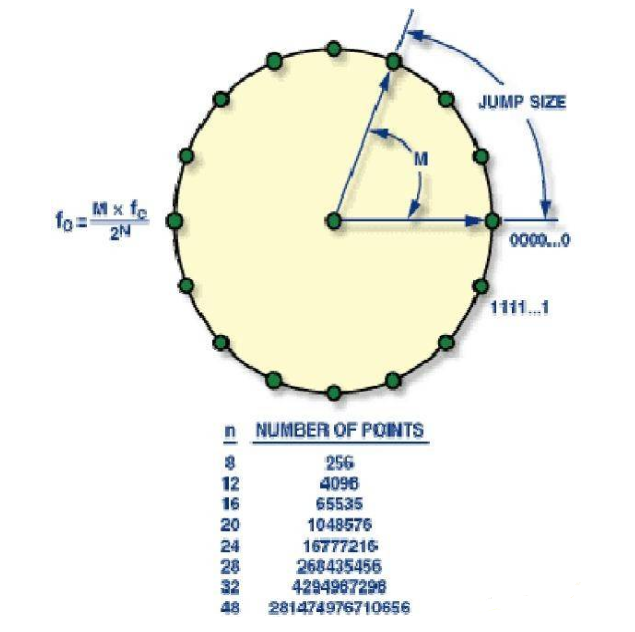

DDS 正是利用了這一特點來產生正弦信號。如圖 2,根據DDS 的頻率控制字的位數N,把360° 平均分成了2的N次等份。

圖2,相位累加器原理

假設系統時鐘為Fc,輸出頻率為Fout。每次轉動一個角度360°/2N, 則可以產生一個頻率為Fc/2N 的正弦波的相位遞增量。那么只要選擇恰當的頻率控制字M,使得 Fout / Fc= M / 2N,就可以得到所需要的輸出頻率Fout,

Fout = Fc*M / 2N,相位幅度轉換通過相位累加器,我們已經得到了合成Fout 頻率所對應的相位信息,然后相位幅度轉換器把0°~360°的相位轉換成相應相位的幅度值。比如當DDS 選擇為2V p-p 的輸出時,45°對應的幅度值為0.707V,這個數值以二進制的形式被送入DAC。這個相位到幅度的轉換是通過查表完成的。

DAC 輸出代表幅度的二進制數字信號被送入DAC 中,并轉換成為模擬信號輸出。注意DAC 的位數并不影響輸出頻率的分辨率。輸出頻率的分辨率是由頻率控制字的位數決定的。

累加器代碼

module counter (co, reset, data, ci, clk);

parameter N=4;

output co;

input reset, ci, clk;

input[N-1:0]data;

reg [N-1:0] q ;

// ???-1|?ü?èê?

always @(posedge clk)

begin

if (reset) q《=0;//

else

if(ci) q《=q + 1;

end

assign co=(q==data-1) && ci; //

endmodule

非常好我支持^.^

(28) 80%

不好我反對

(7) 20%

相關閱讀:

- [電子說] 學習STM32F103的ADC功能 2023-10-24

- [電子說] 學習STM32F103的DAC功能 2023-10-24

- [電子說] 學習STM32F103的定時器功能 2023-10-24

- [電子說] STM32基礎知識:定時器的PWM輸出功能 2023-10-24

- [電子說] 既然ODR能控制管腳高低電平,為什么還需要BSRR寄存器呢? 2023-10-24

- [電子說] ARM系列-P Channel簡析 2023-10-24

- [控制/MCU] 基于STM32F429芯片的單片機芯片內存映射圖 2023-10-23

- [電子說] 軟硬件交互的角度將中斷的知識梳理 2023-10-22

( 發表人:李倩 )