1. BGA和CSP封裝技術(shù)詳解 2.?干貨分享丨BGA開路金相切片分析 (BGA Open Cross-Section) ? ? ? 審核編輯:彭靜

2022-07-26 14:43:18 5181

5181 您是否認(rèn)為在150mm晶圓上制作芯片已經(jīng)過時(shí)了?再想一想呢!當(dāng)今市場(chǎng)的大趨勢(shì)——自動(dòng)駕駛汽車、電動(dòng)汽車、5G無線通信、增強(qiáng)現(xiàn)實(shí)和虛擬現(xiàn)實(shí)(AR/VR)、醫(yī)療保健,這些應(yīng)用都是在150mm晶圓上進(jìn)

2019-05-12 23:04:07

請(qǐng)問大家,0.4pitch的CSP封裝是怎么布線的,間距太小了

2016-06-29 21:36:01

。該方法與晶圓微調(diào)法相似,通過調(diào)整輸入級(jí)上的電阻器來校正失調(diào)電壓。但是在這種應(yīng)用實(shí)例中,調(diào)整工作是在器件最終封裝后完成。調(diào)整方法通常是在最后封裝級(jí)制造測(cè)試過程中將數(shù)字信號(hào)應(yīng)用于輸出。微調(diào)完成后,微調(diào)

2018-09-18 07:56:15

顆粒(如三星,現(xiàn)代,美光,力晶,爾必達(dá)等)有長(zhǎng)期供貨能力(這方面渠道的)請(qǐng)與我公司聯(lián)系采購各類半導(dǎo)體報(bào)廢晶圓片,IC晶圓、IC硅片、IC裸片、IC級(jí)單晶硅片、單晶硅IC小顆粒、IC級(jí)白/藍(lán)膜片、蕓膜片

2020-12-29 08:27:02

有人又將其稱為圓片級(jí)-芯片尺寸封裝(WLP-CSP),以晶圓圓片為加工對(duì)象,在晶圓上封裝芯片。晶圓封裝中最關(guān)鍵的工藝為晶圓鍵合,即是通過化學(xué)或物理的方法將兩片晶圓結(jié)合在一起,以達(dá)到密封效果。如下

2021-02-23 16:35:18

焊盤整理完成之后就可以重新貼裝元件了。這時(shí)我們又面臨了新的問題:如果選擇錫膏裝配的話,如何印刷錫膏呢?對(duì)于密間距的晶圓級(jí)CSP來說,這的確是一個(gè)難題。有采用小鋼網(wǎng),采用手工的方式來局部印刷錫膏

2018-09-06 16:32:16

晶圓級(jí)CSP的返修工藝包括哪幾個(gè)步驟?晶圓級(jí)CSP對(duì)返修設(shè)備的要求是什么?

2021-04-25 08:33:16

晶圓級(jí)CSP的元件如何重新貼裝?怎么進(jìn)行底部填充?

2021-04-25 06:31:58

細(xì)間距的晶圓級(jí)CSP時(shí),將其當(dāng)做倒裝晶片并采用助焊劑浸蘸的方法進(jìn)行組裝,以取代傳統(tǒng)的焊膏印刷組裝,如圖2所示,首先將晶圓級(jí)CSP浸蘸在設(shè)定厚度的助焊劑薄膜中,然后貼裝,再回流焊接,最后底部填充(如果有要求)。關(guān)于錫膏裝配和助焊劑裝配的優(yōu)缺點(diǎn)。圖1 工藝流程1——錫膏裝配圖2 工藝流程2——助焊劑裝配

2018-09-06 16:24:04

晶圓級(jí)CSP裝配回流焊接工藝控制,看完你就懂了

2021-04-25 06:28:40

; ·尺寸和位置精度受阻焊膜窗口的影響,不適合密間距元件的裝配。 NSMD焊盤的尺寸和位置不受阻焊膜窗口的影響,在焊盤和阻焊膜之間有一定空隙,如圖2和圖3所示。對(duì)于 密間距晶圓級(jí)CSP,印刷電路板上的焊盤

2018-09-06 16:32:27

低,這樣焊錫膏可以很容易地沉積。 對(duì)于0.5 mm和0.4 mm晶圓級(jí)CSP的裝配,錫膏印刷面臨挑戰(zhàn),選擇合適的錫膏是關(guān)鍵之一。0.5 mmCSP的印 刷可以選用免洗型type3。0.4 mmCSP

2018-11-22 16:27:28

的是CSP裝配的熱循環(huán)可靠性,利用晶圓級(jí)CSP,采用不同的裝配方式來比較其在熱循環(huán)測(cè)試中的 可靠性。依據(jù)IPC-9701失效標(biāo)準(zhǔn),熱循環(huán)測(cè)試測(cè)試條件: ·0/100°C氣——?dú)鉄嵫h(huán)測(cè)試

2018-09-06 16:40:03

晶圓級(jí)CSP的裝配對(duì)貼裝壓力控制、貼裝精度及穩(wěn)定性、照相機(jī)和影像處理技術(shù)、吸嘴的選擇、助焊劑應(yīng) 用單元和供料器,以及板支撐及定位系統(tǒng)的要求類似倒裝晶片對(duì)設(shè)備的要求。WLCSP貼裝工藝的控制可以參

2018-09-06 16:32:18

經(jīng)底部填充的CSP裝配,其穩(wěn)健的機(jī)械連接強(qiáng)度得到很大的提升。在二級(jí)裝配中,由于底部填充,其抵御 由于扭轉(zhuǎn)、振動(dòng)和熱疲勞應(yīng)力的能力得以加強(qiáng)。但經(jīng)過底部填充的CSP如何進(jìn)行返修成了我們面臨

2018-09-06 16:32:17

晶圓級(jí)封裝技術(shù)Wafer Level Package Technology Board Mounting Application Note for 0.800mm pitch

2009-06-12 23:57:22

晶圓級(jí)封裝技術(shù)源自于倒裝芯片。晶圓級(jí)封裝的開發(fā)主要是由集成器件制造廠家(IBM)率先啟動(dòng)。1964年,美國IBM公司在其M360計(jì)算器中最先采用了FCOB焊料凸點(diǎn)倒裝芯片器件。

2020-03-06 09:02:23

晶圓級(jí)封裝類型及涉及的產(chǎn)品

2015-07-11 18:21:31

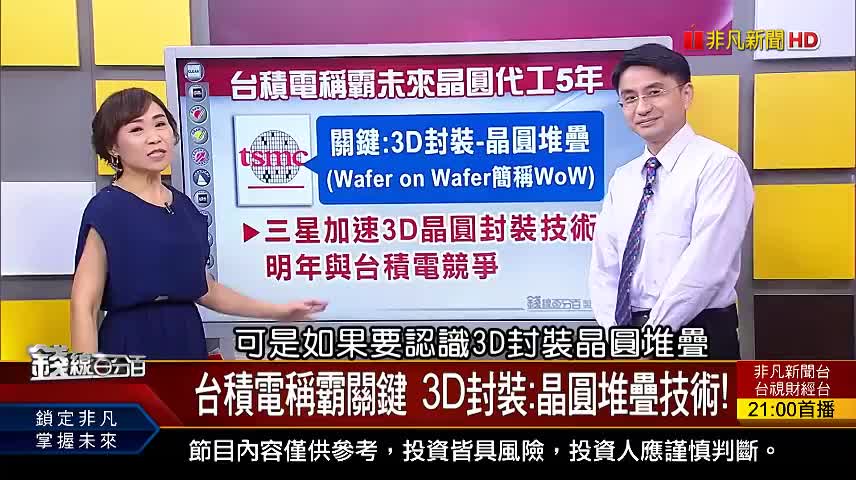

先進(jìn)封裝發(fā)展背景晶圓級(jí)三維封裝技術(shù)發(fā)展

2020-12-28 07:15:50

晶圓級(jí)芯片封裝技術(shù)是對(duì)整片晶圓進(jìn)行封裝測(cè)試后再切割得到單個(gè)成品芯片的技術(shù),封裝后的芯片尺寸與裸片一致。

2019-09-18 09:02:14

%,但受疫情影響,日前法說會(huì)上下修對(duì)全年半導(dǎo)體與晶圓代工產(chǎn)值預(yù)估;而由于居家工作需求成長(zhǎng),高效運(yùn)算平臺(tái)動(dòng)能優(yōu)于預(yù)期,仍樂觀看臺(tái)積電今年展望,估營(yíng)收成長(zhǎng)14-19%,高標(biāo)逼近20%,雖下修展望,但守住

2020-06-30 09:56:29

晶圓凸點(diǎn)模板技術(shù)和應(yīng)用效果評(píng)價(jià)詳細(xì)介紹了晶圓凸點(diǎn)目前的技術(shù)現(xiàn)狀,應(yīng)用效果,通過這篇文章可以快速全面了解晶圓凸點(diǎn)模板技術(shù)晶圓凸點(diǎn)模板技術(shù)和應(yīng)用效果評(píng)價(jià)[hide][/hide]

2011-12-02 12:44:29

` 晶圓級(jí)封裝是一項(xiàng)公認(rèn)成熟的工藝,元器件供應(yīng)商正尋求在更多應(yīng)用中使用WLP,而支持WLP的技術(shù)也正快速走向成熟。隨著元件供應(yīng)商正積極轉(zhuǎn)向WLP應(yīng)用,其使用范圍也在不斷擴(kuò)大。 目前有5種成熟

2011-12-01 14:33:02

`晶圓切割目的是什么?晶圓切割機(jī)原理是什么?一.晶圓切割目的晶圓切割的目的,主要是要將晶圓上的每一顆晶粒(Die)加以切割分離。首先要將晶圓(Wafer)的背面貼上一層膠帶(Wafer Mount

2011-12-02 14:23:11

圓比人造鉆石便宜多了,感覺還是很劃算的。硅的純化I——通過化學(xué)反應(yīng)將冶金級(jí)硅提純以生成三氯硅烷硅的純化II——利用西門子方法,通過三氯硅烷和氫氣反應(yīng)來生產(chǎn)電子級(jí)硅 二、制造晶棒晶體硅經(jīng)過高溫成型,采用

2019-09-17 09:05:06

`微晶片制造的四大基本階段:晶圓制造(材料準(zhǔn)備、長(zhǎng)晶與制備晶圓)、積體電路制作,以及封裝。晶圓制造過程簡(jiǎn)要分析[hide][/hide]`

2011-12-01 13:40:36

所用的硅晶圓。) 通過使用化學(xué)、電路光刻制版技術(shù),將晶體管蝕刻到硅晶圓之上,一旦蝕刻是完成,單個(gè)的芯片被一塊塊地從晶圓上切割下來。 在硅晶圓圖示中,用黃點(diǎn)標(biāo)出的地方是表示這個(gè)地方存在一定缺陷,或是

2011-12-01 16:16:40

。您能否告訴我們您對(duì)晶圓探針去嵌入技術(shù)的可行性的看法? 以上來自于谷歌翻譯 以下為原文We would like to characterize our co-planar wafer probes

2019-01-23 15:24:48

` 誰來闡述一下晶圓有什么用?`

2020-04-10 16:49:13

,然后切割成一片一片薄薄的晶圓。會(huì)聽到幾寸的晶圓廠,如果硅晶圓的直徑越大,代表著這座晶圓廠有較好的技術(shù)。另外還有scaling技術(shù)可以將電晶體與導(dǎo)線的尺寸縮小,這兩種方式都可以在一片晶圓上,制作出更多

2011-09-07 10:42:07

`晶圓的結(jié)構(gòu)是什么樣的?1 晶格:晶圓制程結(jié)束后,晶圓的表面會(huì)形成許多格狀物,成為晶格。經(jīng)過切割器切割后成所謂的晶片 2 分割線:晶圓表面的晶格與晶格之間預(yù)留給切割器所需的空白部分即為分割線 3

2011-12-01 15:30:07

晶圓針測(cè)制程介紹 晶圓針測(cè)(Chip Probing;CP)之目的在于針對(duì)芯片作電性功能上的 測(cè)試(Test),使 IC 在進(jìn)入構(gòu)裝前先行過濾出電性功能不良的芯片,以避免對(duì)不良品增加制造成

2020-05-11 14:35:33

`159-5090-3918回收6寸晶圓,8寸晶圓,12寸晶圓,回收6寸晶圓,8寸晶圓,12寸晶圓,花籃,Film Fram Cassette,晶元載具Wafer shipper,二手晶元盒

2020-07-10 19:52:04

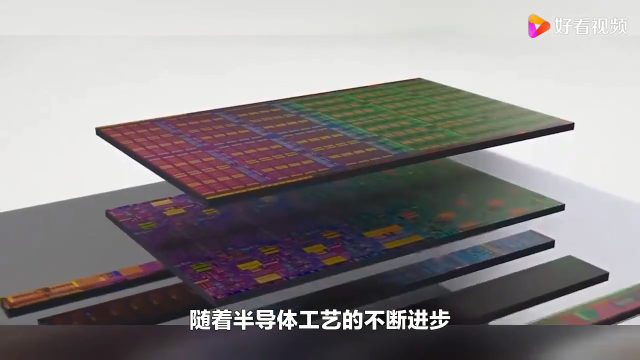

多芯片封裝解決方案方向發(fā)展。芯片堆疊可以通過一次一片的方式生產(chǎn),也可以通過晶圓級(jí)封裝方式進(jìn)行。未來發(fā)展趨勢(shì)封裝技術(shù)中的一個(gè)重要新方向是使用柔性襯底把多個(gè)剛性器件封裝在一起。多個(gè)傳感器可以和電子單元

2010-12-29 15:44:12

晶圓級(jí)芯片級(jí)封裝; 49 bumps; 3.29×3.29×0.54mm(包括背面涂層)

2022-12-06 06:06:48

(SMT)用PCB產(chǎn)品->芯片級(jí)封裝(CSP)用PCB產(chǎn)品3) 導(dǎo)線尺寸精細(xì)化,導(dǎo)通孔尺寸微小化,盲埋孔高密度互連的出現(xiàn),板面平整度要 求高,焊盤平面性重要性高,孔/線/層/面

2012-11-24 14:52:10

SMT組件中時(shí),技術(shù)遇到的困難最大。在一級(jí)封裝組件應(yīng)用中,倒裝片廣泛用于BGA和CSP,盡管BGA和CSP已經(jīng)采用了引線-框架技術(shù)。在板級(jí)組裝中,采用倒裝片可以帶來許多優(yōu)點(diǎn),包括組件尺寸減小、性能提高

2013-10-22 11:43:49

標(biāo)準(zhǔn)SMT組件中時(shí),技術(shù)遇到的困難最大。在一級(jí)封裝組件應(yīng)用中,倒裝片廣泛用于BGA和CSP,盡管BGA和CSP已經(jīng)采用了引線-框架技術(shù)。在板級(jí)組裝中,采用倒裝片可以帶來許多優(yōu)點(diǎn),包括組件尺寸減小、性能

2018-09-10 15:46:13

SiC SBD 晶圓級(jí)測(cè)試 求助:需要測(cè)試的參數(shù)和測(cè)試方法謝謝

2020-08-24 13:03:34

美國Amkor公司 ChriStopher M.Scanlan和Nozad Karim一、SiP技術(shù)的產(chǎn)生背景系統(tǒng)級(jí)封裝SiP(System-In-Package)是將一個(gè)電子功能系統(tǒng),或其子系統(tǒng)中

2018-08-23 09:26:06

的安全。下面給大家重點(diǎn)介紹回掃型ESD的新型封裝技術(shù)CSP: TVS新型封裝CSPCSP封裝的概念:Chip Scale Package 芯片級(jí)封裝 (晶圓級(jí)封裝)WLP (WLP,Wafer

2020-07-30 14:40:36

效應(yīng)和功耗。因此,三維系統(tǒng)集成技術(shù)在性能、功能和形狀因素等方面都具有較大的優(yōu)勢(shì)。用于三維集成的先進(jìn)晶圓級(jí)技術(shù)晶圓級(jí)封裝技術(shù)已在許多產(chǎn)品制造中得到廣泛應(yīng)用。目前正在開發(fā)晶圓級(jí)封裝的不同工藝技術(shù),以滿足在提高

2011-12-02 11:55:33

納米到底有多細(xì)微?什么晶圓?如何制造單晶的晶圓?

2021-06-08 07:06:42

`什么? 你對(duì)CSP的了解還不夠?趕快來圍觀吧! 首先,得知道什么叫CSPCSP(Chip Scale Package),又稱為芯片級(jí)封裝器件, 其技術(shù)性主要體現(xiàn)為讓芯片面積與封裝面積之比超過1

2017-02-24 16:36:32

` 晶圓是指硅半導(dǎo)體集成電路制作所用的硅晶片,由于其形狀為圓形,故稱為晶圓;在硅晶片上可加工制作成各種電路元件結(jié)構(gòu),而成為有特定電性功能之IC產(chǎn)品。晶圓的原始材料是硅,而地殼表面有用之不竭的二氧化硅

2011-12-01 11:40:04

`晶圓級(jí)封裝(WLP)就是在其上已經(jīng)有某些電路微結(jié)構(gòu)(好比古董)的晶片(好比座墊)與另一塊經(jīng)腐蝕帶有空腔的晶片(好比玻璃罩)用化學(xué)鍵結(jié)合在一起。在這些電路微結(jié)構(gòu)體的上面就形成了一個(gè)帶有密閉空腔的保護(hù)

2011-12-01 13:58:36

的輔助。 測(cè)試是為了以下三個(gè)目標(biāo)。第一,在晶圓送到封裝工廠之前,鑒別出合格的芯片。第二,器件/電路的電性參數(shù)進(jìn)行特性評(píng)估。工程師們需要監(jiān)測(cè)參數(shù)的分布狀態(tài)來保持工藝的質(zhì)量水平。第三,芯片的合格品與不良品

2011-12-01 13:54:00

發(fā)展趨勢(shì)的推動(dòng)下,制造商開發(fā)出更小的封裝類型。最小的封裝當(dāng)然是芯片本身,圖1描述了IC從晶片到單個(gè)芯片的實(shí)現(xiàn)過程,圖2為一個(gè)實(shí)際的晶片級(jí)封裝(CSP)。 晶片級(jí)封裝的概念起源于1990年,在1998年

2018-08-27 15:45:31

請(qǐng)問像AD8233一樣的晶圓封裝在PCB中如何布線,芯片太小,過孔和線路都無法布入,或者有沒有其他封裝的AD8233

2023-11-14 07:01:48

摘 要:先進(jìn)封裝技術(shù)不斷發(fā)展變化以適應(yīng)各種半導(dǎo)體新工藝和材料的要求和挑戰(zhàn)。在半導(dǎo)體封裝外部形式變遷的基礎(chǔ)上,著重闡述了半導(dǎo)體后端工序的關(guān)鍵一封裝內(nèi)部連接方式的發(fā)展趨勢(shì)。分析了半導(dǎo)體前端制造工藝的發(fā)展

2018-11-23 17:03:35

1、為什么晶圓要做成圓的?如果做成矩形,不是更加不易產(chǎn)生浪費(fèi)原料?2、為什么晶圓要多出一道研磨的工藝?為什么不能直接做成需求的厚度?

2014-01-20 15:58:42

單晶的晶圓制造步驟是什么?

2021-06-08 06:58:26

無線手持設(shè)備、掌上電腦以及其他移動(dòng)電子設(shè)備的增加導(dǎo)致了消費(fèi)者對(duì)各種小外形、特征豐富產(chǎn)品的需要。為了滿足越來越小的器件同時(shí)具有更多功能的市場(chǎng)趨勢(shì)和移動(dòng)設(shè)計(jì)要求,業(yè)界開發(fā)了芯片級(jí)封裝(CSP)形式的特定

2018-11-23 16:58:54

晶圓劃片 (Wafer Dicing )將晶圓或組件進(jìn)行劃片或開槽,以利后續(xù)制程或功能性測(cè)試。提供晶圓劃片服務(wù),包括多項(xiàng)目晶圓(Multi Project Wafer, MPW)與不同材質(zhì)晶圓劃片

2018-08-31 14:16:45

嵌入式系統(tǒng)趨勢(shì)展望2013,可以了解下!

2013-04-14 00:46:56

怎么選擇晶圓級(jí)CSP裝配工藝的錫膏?

2021-04-25 08:48:29

固態(tài)圖像傳感器要求在環(huán)境大氣中得到有效防護(hù)。第一代圖像傳感器安裝在帶玻璃蓋的標(biāo)準(zhǔn)半導(dǎo)體封裝中。這種技術(shù)能使裸片得到很好的密封和異常堅(jiān)固的保護(hù),但體積比較龐大,制造成本也比較高。引入晶圓級(jí)封裝后

2018-12-03 10:19:27

以來迅速發(fā)展的新型微電子封裝技術(shù),包括焊球陣列封裝(BGA)、芯片尺寸封裝(CSP)、圓片級(jí)封裝(WLP)、三維封裝(3D)和系統(tǒng)封裝(SIP)等項(xiàng)技術(shù)。介紹它們的發(fā)展?fàn)顩r和技術(shù)特點(diǎn)。同時(shí),敘述了

2018-09-12 15:15:28

`各位大大:手頭上有顆晶圓的log如下:能判斷它的出處嗎?非常感謝!!`

2013-08-26 13:45:30

求晶圓劃片或晶圓分撿裝盒合作加工廠聯(lián)系方式:QQ:2691003439

2019-03-13 22:23:17

的補(bǔ)償電路比較復(fù)雜,成本也較高,只適用于基地站和廣播電臺(tái)等要求高精度化的情況。因此,通常我們使用的都是采用的模擬式間接溫度補(bǔ)償?shù)臏匮a(bǔ)晶振。 隨著科學(xué)技術(shù)的不斷發(fā)展,晶振向小型化趨勢(shì)的不斷發(fā)展,溫補(bǔ)晶

2014-02-13 15:54:37

激光用于晶圓劃片的技術(shù)與工藝 激光加工為無接觸加工,激光能量通過聚焦后獲得高能量密度,直接將硅片

2010-01-13 17:01:57

隨著集成電路設(shè)計(jì)師將更復(fù)雜的功能嵌入更狹小的空間,異構(gòu)集成包括器件的3D堆疊已成為混合與連接各種功能技術(shù)的一種更為實(shí)用且經(jīng)濟(jì)的方式。作為異構(gòu)集成平臺(tái)之一,高密度扇出型晶圓級(jí)封裝技術(shù)正獲得越來越多

2020-07-07 11:04:42

看到了晶圓切割的一個(gè)流程,但是用什么工具切割晶圓?求大蝦指教啊 ?

2011-12-01 15:47:14

朝著超小型的方向發(fā)展,出現(xiàn)了與芯片尺寸大小相同的超小型封裝形式--圓晶級(jí)封裝技術(shù)(WLP)。 ●電子封裝技術(shù)從二維向三維方向發(fā)展,不僅出現(xiàn)3D-MCM,也出現(xiàn)了3D-SIP等封裝形式。 ●電子封裝技術(shù)

2018-08-23 12:47:17

搶注電子采購供應(yīng)市場(chǎng)趨勢(shì)展望峰會(huì),立省500元 2011電子采購供應(yīng)市場(chǎng)趨勢(shì)展望峰會(huì)(簡(jiǎn)稱“峰會(huì)”)將于2011年3月4日在深圳舉辦。此次峰會(huì)重點(diǎn)分析三網(wǎng)融合和高新技術(shù)產(chǎn)業(yè)給電子制造業(yè)的商機(jī),電子

2011-02-11 21:07:00

越大,代表著這座晶圓廠有較好的技術(shù)。另外還有scaling技術(shù)可以將電晶體與導(dǎo)線的尺寸縮小,這兩種方式都可以在一片晶圓上,制作出更多的硅晶粒,提高品質(zhì)與降低成本。所以這代表6寸、8寸、12寸晶圓當(dāng)中

2011-12-02 14:30:44

自動(dòng)化測(cè)試技術(shù)發(fā)展趨勢(shì)展望分析,不看肯定后悔

2021-05-14 06:50:31

以來迅速發(fā)展的新型微電子封裝技術(shù),包括焊球陣列封裝(BGA)、芯片尺寸封裝(CSP)、圓片級(jí)封裝(WLP)、三維封裝(3D)和系統(tǒng)封裝(SIP)等項(xiàng)技術(shù)。介紹它們的發(fā)展?fàn)顩r和技術(shù)特點(diǎn)。同時(shí),敘述了微電子

2023-12-11 01:02:56

SRAM中晶圓級(jí)芯片級(jí)封裝的需求

2020-12-31 07:50:40

固態(tài)圖像傳感器要求在環(huán)境大氣中得到有效防護(hù)。第一代圖像傳感器安裝在帶玻璃蓋的標(biāo)準(zhǔn)半導(dǎo)體封裝中。這種技術(shù)能使裸片得到很好的密封和異常堅(jiān)固的保護(hù),但體積比較龐大,制造成本也比較高。引入晶圓級(jí)封裝后

2018-10-30 17:14:24

晶圓測(cè)溫系統(tǒng),晶圓測(cè)溫?zé)犭娕迹?b class="flag-6" style="color: red">晶圓測(cè)溫裝置一、引言隨著半導(dǎo)體技術(shù)的不斷發(fā)展,晶圓制造工藝對(duì)溫度控制的要求越來越高。熱電偶作為一種常用的溫度測(cè)量設(shè)備,在晶圓制造中具有重要的應(yīng)用價(jià)值。本文

2023-06-30 14:57:40

CSP封裝內(nèi)存

CSP(Chip Scale Package),是芯片級(jí)封裝的意思。CSP封裝最新一代的內(nèi)存芯片封裝技術(shù),其技術(shù)性能又有了新的提升。CSP封裝可以讓芯片面積與封裝面積之比超

2009-12-25 14:24:49 636

636 什么是CSP封裝

近幾年的硬件發(fā)展是日新月異,處理器已經(jīng)進(jìn)入G赫茲時(shí)代,封裝形式也是經(jīng)歷了數(shù)種變化。不過,光有一顆速急力猛的芯還遠(yuǎn)遠(yuǎn)不夠

2010-03-04 11:43:25 14777

14777 CSP封裝芯片的量產(chǎn)測(cè)試采用類似晶圓測(cè)試的方法進(jìn)行,但是兩者的區(qū)別在于:晶圓的測(cè)試,探針是扎在管芯的PAD(通常情況下為鋁金屬)上,而CSP封裝的測(cè)試座,探針是扎到CSP封裝的錫

2012-05-02 10:00:40 1546

1546 CSP(chip scale package)封裝是指一種封裝自身的體積大小不超過芯片自身大小的20%的封裝技(下一代技術(shù)為襯底級(jí)別封裝,其封裝大小與芯片相同)。

2018-09-05 08:36:00 13375

13375 CSP封裝是最新一代的內(nèi)存芯片封裝技術(shù),其技術(shù)性能又有了新的提升。CSP封裝可以讓芯片面積與封裝面積之比超過1:1.14,已經(jīng)相當(dāng)接近1:1的理想情況,絕對(duì)尺寸也僅有32平方毫米,約為普通的BGA的1/3,僅僅相當(dāng)于TSOP內(nèi)存芯片面積的1/6。與BGA封裝相比,同等空間下CSP封裝可以將存儲(chǔ)容量提高三倍。

2019-06-24 14:12:36 19779

19779 倒裝芯片 CSP 封裝

2022-11-14 21:07:58 19

19 BGA和CSP封裝技術(shù)詳解

2023-09-20 09:20:14 951

951

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論