在高速實時或者非實時信號處理系統當中,使用大容量存儲器實現數據緩存是一個必不可少的環節,也是系統實現中的重點和難點之一。SDRAM(同步動態隨機訪問存儲器)具有價格低廉、密度高、數據讀寫速度快的優點

2018-01-18 07:21:00 7964

7964

更快、更大,每比特的功耗也更低,但是如何實現FPGA和DDR3 SDRAM DIMM條的接口設計呢? 關鍵字:均衡(leveling)如果FPGA I/O結構中沒有包含均衡功能,那么它與DDR3

2019-04-22 07:00:08

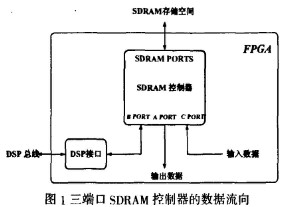

現場電路設計中。本文用 FPGA 作為接口芯片,提供控制信號和定時信號,來實現 DSP 到 SDRAM 的數據存取。1 、SDRAM 介紹本文采用的 SDRAM 為 TMS626812A,圖 1 為其

2020-04-23 08:00:00

FPGA怎么實現控制CF從SDRAM中讀取數據以及實現CF卡向SDRAM中上傳數據????本人初學者,希望大家幫幫忙!!!!謝謝!!

2013-02-25 21:58:59

處理方法。本系統的主要工作是通過基于FPGA的嵌入式系統,實現數據采集、數據存儲、LCD顯示、USB數據傳輸和數據處理,完成光 纖微擾動傳感的擾動識別和定位功能。1 系統結構和硬件設計1.1 系統結構

2020-09-04 09:56:23

存儲器)也是FPGA設計中經常采用的內存器件,掉電后不能保存數據,功耗也比較大。因此Flash用于保存FPGA系統啟動所需的配置文件,SDRAM則用于系統的數據的緩存,所有程序的運行都在內存中進

2018-08-02 09:37:08

實戰應用,這種快樂試試你就會懂的。話不多說,上貨。SDR SDRAM驅動設計實用進階 本篇實現基于叁芯智能科技的SANXIN -B01 FPGA開發板,以下為配套的教程,如有入手開發板,可以登錄官方

2023-03-27 17:09:14

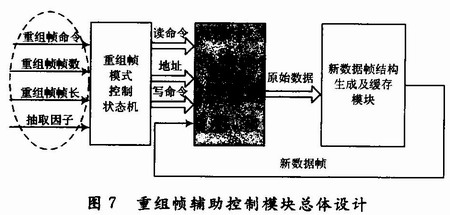

SDRAM文件結構存儲控制的FPGA實現面對不同的應用場景,原始采樣數據可能包含多種不同樣式的信號,這給傳統基于連續存儲方式的數據緩存系統帶來了挑戰。除此之外,由于對不同信號的處理往往需要不同的數據

2012-08-13 10:40:40

和后仿真。以上介紹了一種應用于通用微處理器系統中的SDRAM與雙口RAM之間的數據轉移接口控制電路,由VHDL語言設計,用Xilinx公司4000系列FPGA實現,目前該電路硬件實現和微處理器系統已經通過驗證,證明可將SDRAM作為高速、大容量存儲器應用在簡單電子系統中。

2019-06-10 05:00:08

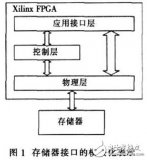

對SDRAM的控制,并通過利用FPGA控制數據存取的順序來實現對數字視頻圖像的旋轉,截取、平移等實時處理。SDRAM的控制原理,如圖1所示。 [/hide]

2009-11-13 11:37:08

請問各位大蝦 SDRAM是如何進行讀寫的,如何將文件數據存儲到SDRAM中 網上沒找到這方面的資料 求各位大蝦幫忙

2013-04-14 10:09:13

用DAQmax采集助手做的一個數據采集系統,用TDMS文件格式存儲數據,怎樣實現系統把一天的數據存儲到以當日日期命名的數據文件中?

2014-10-25 09:01:55

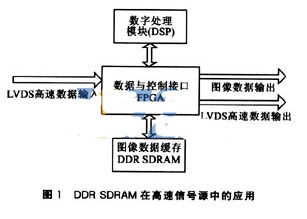

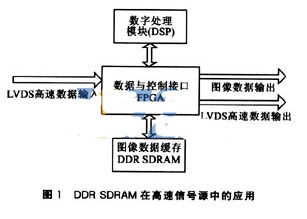

。 在該系統中,由FPGA的完成各模塊之間的接口控制。FPGA接收從前端傳送過來的高速數字信號,并將其存儲在DDR SDRAM中;DSP通過FPGA讀取DDR中的數據,處理后再送回到DDRSDRAM,最后

2018-12-18 10:17:15

的文件系統,實現了文件系統基本的數據緩存、掉電恢復、磨損均衡等功能,在資源相對富裕的環境中,開發者們可以對其運行機制甚至存儲結構進行“使用空間換時間”的優化策略,提升讀寫的IO性能。學會有效地利用文件系統往往能起到事半功倍的作用,希望開發者能夠將所學知識有效應用到未來的開發工作中,從而提高開發工作的效率。

2022-07-18 12:18:40

緩存控制器( Buffer Controller)緩存控制器負責暫時存儲接收或發送的數據,這些數據來自設備端的外部SDRAM或者主機。考慮到USB 2. 0 高速數據的傳輸要求,減小存儲或讀取數據

2019-04-12 07:00:12

設計的思想。項目實現了PC機上的上位機通過以太網UDP協議將圖片數據傳輸給AC620 FPGA開發板,AC620接收圖片數據后將圖片緩存在片外的SDRAM中,最后將緩存的圖片數據顯示在4.3寸TFT屏上

2017-09-17 16:43:43

`一、硬件平臺二、實驗簡介本實驗基于ARM+FPGA超mini款iCore4T雙核心板,核心板ARM掛有一片32MB SDRAM,可用于數據采集緩存,液晶顯示緩存,代碼執行等。該實驗將帶你一步一步

2020-04-06 22:08:43

管理模型,它能夠根據應用優先級區分回收緩存資源以實現對各應用緩存分區容量的在線動態調節進而達成應用級緩存管理語義.實驗數據表明PARP策略能夠在實際系統中有效的支持區分應用優先級,這不僅可以用于實現存儲系統

2010-04-24 09:43:47

使用Verilog實現基于FPGA的SDRAM控制器

2012-08-20 19:35:27

介紹了一種基于現場可編程門陣列(FPGA)和第二代雙倍數據率同步動態隨機存取記憶體(DDR2)的高速模數轉換(ADC)采樣數據緩沖器設計方法,論述了在Xilinx V5 FPGA中如何實現高速同步

2010-04-26 16:12:39

基于FPGA的SDRAM設計與實現

2013-03-14 18:34:25

設計高溫環境下(最高120°)基于FPGA的數據采集存儲系統,就是通過傳感器采集數據,通過FPGA來控制,把數據存儲到存儲芯片上,回頭可以通過接口讀取數據顯示在計算機上,求大師給我指導,我急需整個系統的protel原理圖,請各位幫忙,我將感激不盡。最好有附件畫出整個原理圖,謝謝!

2012-10-29 21:37:12

進行了DDR3 SDRAM控制器的編寫,分析并提出了提高帶寬利用率的方法。最終將其進行類FIFO接口的封裝,屏蔽掉了DDR3 IP核復雜的用戶接口,為DDR3數據流緩存的實現提供便利。系統測試表明,該

2018-08-02 09:34:58

作者:吳連慧,周建江,夏偉杰摘要:為了解決視頻圖形顯示系統中多個端口訪問DDR3的數據存儲沖突,設計并實現了基于FPGA的DDR3存儲管理系統。DDR3存儲器控制模塊使用MIG生成DDR3控制器

2018-08-02 11:23:24

顯示。FPGA的片內存儲資源較少,對于緩存如此大量的數據,只能使用SDRAM或DDR3緩存數據。2、圖片的預處理首先選取要顯示的圖片兩張,使用 Window 系統自帶的畫圖工具對圖片進行處理,將圖片

2023-01-06 17:06:04

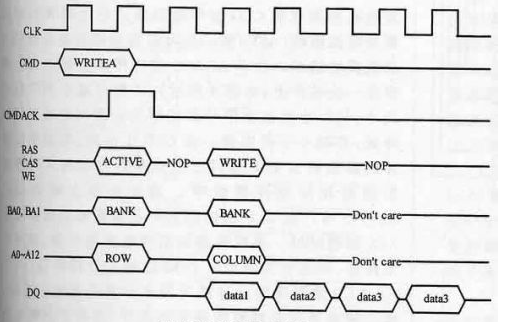

SDRAM同步動態隨機存儲器,同步是指內存工作需要同步時鐘,內部的命令的發送與數據的傳輸都以它為基準;動態是指存儲陣列需要不斷的刷新來保證數據不丟失;隨機是指數據不是線性依次存儲,而是自由指定地址

2016-10-07 09:43:43

吞吐量大、功耗低的需求,因此選擇DDR3 SDRAM作為機載視頻圖形顯示系統的外部存儲器。本文以Kintex-7系列XC7K410T FPGA芯片和兩片MT41J128M16 DDR3 SDRAM芯片為硬件平臺,設計并實現了基于FPGA的視頻圖形顯示系統的DDR3多端口存儲管理。

2019-06-24 06:07:53

要求:該系統將圖像采集、顯示和存儲功能集成到FPGA平臺上,本設計采用NIOS II 設計軟核系統,通過FPGA初始化圖像傳感器OV7670,OV7670再等待場同步,行同步,將采集的數據在TFT

2012-05-22 09:22:09

了解它,運用它,你會發現它將非常有趣。恭喜我們兩名同學在快樂中制作出了新的作品,在老師的幫助下,兩位同學合力完成了基于SDRAM的圖像存儲顯示系統,跟大家分享一下學習過程吧!首先是設計思路,我們的想法

2019-08-19 10:57:37

的網絡數據傳輸。3、 系統結構高速同步數據采集系統主要包括以下幾個部分:ARM控制器、存儲電路、FPGA邏輯控制電路、A/D轉換電路、FIFO緩存、電源電路、接口電路等。系統具備多通道數據采集接口

2010-08-31 09:14:55

基于Xilinx FPGA的DDR2 SDRAM存儲器接口

2012-08-20 18:55:15

FPGA怎么把數據寫入SDRAM緩存啊?

2016-08-17 11:37:17

本文提出了一種基于FPGA的SDRAM控制器的設計方法,并用Verilog給于實現,仿真結果表明通過該方法設計實現的控制器可以在FPGA芯片內組成如圖1所示的SDRAM接口,從而使得系統用戶對SDRAM的操作非常方便。

2021-04-15 06:46:56

FPGA芯片上實現對時序與數據緩存系統的控制。最后針對Xiling公司的FPGA器件XQ2V3000對設計進行了配置及仿真,從而驗證了該設計方案的可行性。

2021-06-08 06:35:41

由于系統帶寬不斷的增加,因此針對更高的速度和性能,設計人員對存儲技術進行了優化。下一代雙數據速率(DDR)SDRAM芯片是DDR3 SDRAM。 DDR3 SDRAM具有比DDR2更多的優勢。這些

2019-08-09 07:42:01

表。4 結 語介紹了在嵌入式Windows CE系統平臺上,使用大容量SDRAM作為動態存儲設備的方案。詳細介紹了sDRAM硬件連接方案以及軟件接口的實現。該方案已經在工程設計中投入使用,其可以在同類的嵌入式高端產品中推廣使用。

2020-08-12 00:00:00

` 幀差法FPGA實現原理作者:FPGA自習室微信公眾號:FPGA自習室時間:2020/4/12郵箱:1964740514@qq.com根據幀差法的實現流程,設計的雙端口SDRAM控制器,一側讀寫

2020-04-12 23:29:14

,影響系統可靠性,要進一步提高系統實時性,必須研究開發高速嵌入式雷達信號采集系統。這里結合高速嵌入式數據采集系統,提出一種基于CvcloneⅢFPGA實現的異步FIFO和鎖相環(PLL)結構來實現

2019-08-21 06:56:32

請問怎么利用FPGA實現模式可變的衛星數據存儲器糾錯系統?

2021-04-13 06:10:54

結合高速嵌入式數據采集系統,提出一種基于CvcloneⅢ FPGA實現的異步FIFO和鎖相環(PLL)結構來實現高速緩存,該結構可成倍提高數據流通速率,增加數據采集系統的實時性。采用FPGA設計高速緩存,能針對外部硬件系統的改變,通過修改片內程序以應用于不同的硬件環境。

2021-04-30 06:19:52

型號 UD408G5S1AF的一款8Gb 32位 DDR4 SDRAM,是一款支持使用在英特爾Arria 10 SoC FPGA以及Kintex Ultrascale FPGA中的存儲器。32位 DDR4

2020-09-23 10:59:56

本帖最后由 upmcu 于 2012-7-28 15:07 編輯

截圖:LED顯示控制系統中SDRAM控制器的設計.pdf基于FPGA的DDR2+SDRAM數據存儲研究.pdf基于FPGA

2012-07-28 14:40:53

XC2S200型FPGA器件實現。采用Spansion公司的NOR Flash存儲器來存放配置文件,其型號為S29GL512N,容量為512 Mb。系統總體框圖如圖3所示。上位機軟件包括Flash燒寫

2019-05-30 05:00:05

。 3、海量緩存的設計實現 本系統使用了兩片256k16bit容量的SRAM作為高速緩存,系統中的4個通道可同時存儲每通道128k點采樣數據。在25MHz的采樣頻率下,一次可采集存儲5ms多的波形數據

2020-12-04 15:59:14

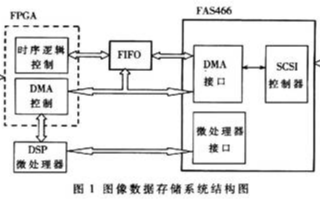

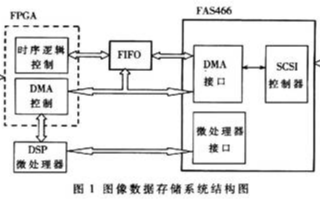

為了實現SCSI協議和硬盤存儲,一般需要有微處理器、DMA控制器、SCSI協議控制器、數據緩存器等硬件支持和相應的軟件控制模塊。·微處理器用來控制設備中各部件的工作,實現設備本身的特定功能。該專用

2011-06-02 09:33:21

一種I2C總線型EEPROM 存儲器,在數據記錄系統中,用來保存當前時刻以前一段時間內的多組數據使用時設計成首尾地址相接的環型存儲結構,實現數據文件的循環存儲文章介紹循環

2009-04-15 10:36:20 33

33 探討了高速數據采集系統中高速采樣緩存的重要性和實現途徑,闡述了基于ADSP-21065L的并行多通道數據采集板上高速采樣緩存的設計與電路結構,給出了采用FPGA實現通道復用和采樣數據

2009-04-23 17:08:09 23

23 介紹基于現場可編程門陣列(FPGA),利用VHDL 語言設計實現MMC2107 與SDRAM 接口電路。文中包括MMC2107 組成結構、SDRAM 存儲接口結構和SDRAM 控制狀態機的設計。

2009-05-15 14:47:29 24

24 提出了一種在HDTV SOC 系統中實現多模塊共享存儲單元的高效SDRAM 控制器。通過利用合理的請求仲裁、Full Page 讀寫、指令與數據分離、指令緩存和前后相關處理等機制,實現了高吞吐

2009-08-14 16:09:14 13

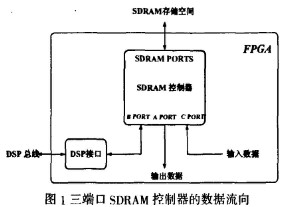

13 設計實現了一種基于FPGA 的,可用于多數據緩存的、能夠高效利用帶寬的多端口SDRAM 控制器。本文使用狀態機的設計思想,采用Verilog 硬件描述語言設計了時序控制程序。得到的SDR

2009-08-27 09:43:33 22

22 本文設計了一種以 FPGA 為數據壓縮和數據緩存單元的高速數據采集系統,其主要特點是對高速采集的數據進行實時壓縮,再將壓縮后的數據進行緩沖存儲。該設計利用數據比較模

2009-11-30 15:32:36 20

20 摘要:一種I2C總線型EEPROM存儲器,在數據記錄系統中,用來保存當前時刻以前一段時間內的多組數據。使用時設計成首尾地址相接的環型存儲結構,實現數據文件的

2006-03-24 13:01:38 1123

1123

摘要: 介紹了SDRAM的存儲體結構、主要控制時序和基本操作命令,并且結合實際系統,給出了一種用FPGA實現的通用SDRAM控制器的方案。

關鍵詞:

2009-06-20 12:51:58 834

834

摘 要:介紹了SDRAM的特點和工作原理,提出了一種基于FPGA的SDRAM控制器的設計方法,使用該方法實現的控制器可非常方便地對SDRAM進行控制。

關鍵

2009-06-20 13:04:51 2075

2075 基于FPGA的高速SDRAM控制器的視頻應用

0 引言 SDRAM(同步動態存儲器)是一種應用廣泛的存儲器,具有容量大、數據讀寫速度快、價格低廉等優點,特別適

2009-11-04 09:56:20 847

847 FPGA芯片在高速數據采集緩存系統中的應用

概 述在高速數據采集方面,FPGA有單片機和DSP無法比擬的優勢。FPGA的時鐘頻率高,內部時延小,全部控制邏輯都可由硬

2010-03-30 10:51:15 881

881

O 引言

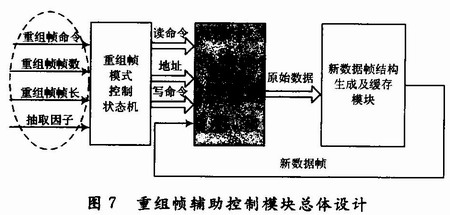

面對不同的應用場景,原始采樣數據可能包含多種不同樣式的信號,這給傳統基于連續存儲方式的數據緩存系統帶來了挑戰。除此之外,由于對不同信

2010-10-08 11:11:20 1179

1179

本內容提出了適于測控系統的文件存儲結構研究,希望對大家學習上有所幫助

2011-05-26 16:20:03 9

9 本文利用“FPGA+單片機”作為存儲控制器,采用基于LZW算法的數據壓縮技術,以SDRAM作為周期存儲和緩存,SD卡作為最終存儲載體,實現車載CAN總線記錄儀實現大容量存儲系統。

2011-09-08 16:24:59 2172

2172

在高速實時或者非實時信號處理系統當中,使用大容量存儲器實現數據緩存是一個必不可少的環節,也是系統實現中的重點和難點之一。詳細闡讀SDRAM數據文檔的前提下,參考ALTERA公司的

2012-10-30 17:04:58 1770

1770

使用功能強大的FPGA來實現一種DDR2 SDRAM存儲器的用戶接口。該用戶接口是基于XILINX公司出產的DDR2 SDRAM的存儲控制器,由于該公司出產的這種存儲控制器具有很高的效率,使用也很廣泛,

2013-01-08 18:15:50 237

237 高速圖像存儲系統中SDRAM控制器的實現

2016-08-29 15:02:03 10

10 華清遠見FPGA代碼-SDRAM讀寫控制的實現與Modelsim仿真

2016-10-27 18:07:54 26

26 中,并采用DMA傳輸技術將存儲后的圖像數據上傳至計算機硬盤中作進一步處理;同時,利用SDRAM顯存實時刷新數據,FPGA構造相應的VGA信號,最終實現100 MB/s圖像數據的實時顯示。 隨著數據存儲設備被廣泛應用于航空航天系統、醫療衛生、工業自動化等各行各業,對于圖像設備采集的控制及實

2017-10-11 18:33:17 6

6 在數字圖像處理、航空航天等高速信號處理應用場合,需要有高速大容量存儲空間的強力支持,來滿足系統對海量數據吞吐的要求。通過使用大容量同步動態RAM(SDRAM)來擴展嵌入式DSP系統存儲空間的方法

2017-10-23 10:48:11 1

1 的像素大小。在存儲模塊中,SDRAM的工作時鐘和視頻采集系統的時鐘不同,為解決讀寫時鐘不同步的問題,采用異步FIFO實現跨時鐘域的同步化,同時采用了兩片SDRAM實現乒乓緩存設計,對SDRAM控制器各個模塊分別進行Modelsim仿真驗證,得出正確結果,可以滿足系統的整體要求。

2017-11-17 01:28:55 3704

3704

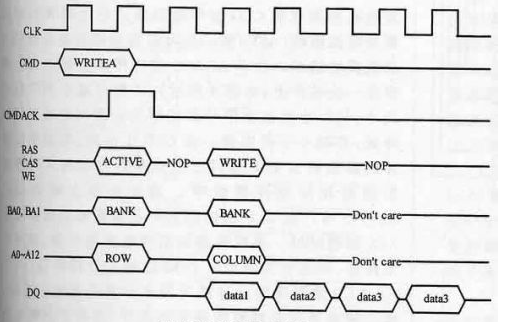

控制器,在介紹控制器的邏輯結構的基礎上,對FPGA與SDRAM間數據通信進行了時序分析,實現SDRAM 帶有自動預充電突發讀寫和非自動預充電整頁讀寫。

2017-11-18 12:42:03 2054

2054

在高速信號處理系統中, 需要緩存高速、大量的數據, 存儲器的選擇與應用已成為系統實現的關鍵所在。DDR SDRAM是一種高速CMOS、動態隨機訪問存儲器, 它采用雙倍數據速率結構來完成高速操作

2018-07-20 18:38:00 12744

12744

為提高云存儲的訪問速率并降低費用,提出了一種面向費用優化的云存儲緩存策略。利用幾乎免費的局域網環境下的多臺桌面計算機,在本地建立一個分布式文件系統,并將其作為遠端云存儲的緩存。進行文件讀取時,首先

2018-01-24 14:45:35 0

0 針對Ceph文件系統元數據寫操作響應時間較長的問題,提出一種對元數據緩存進行備份的方案。該方案采用多個元數據服務器之間互相備份寫緩存數據的方法,保證元數據的可靠性,并設計基于元數據熱度的多隊列緩存

2018-02-08 15:38:24 0

0 SDRAM 具有存儲容量大、速度快、成本低的特點,因此廣泛應用于雷達信號處理等需 要海量高速存儲的場合,但是SDRAM 的操作相對復雜,需要有專門的控制器配合處理器 工作完成數據的存取操作。隨著FPGA 技術的快速發展及其應用的普及,用FPGA 實現 SDRAM 控制器是目前最流行的技術手段。

2019-04-26 08:06:00 2129

2129

,因此能夠很好地滿足上述場合對大量數據緩存的需求。但DDR SDRAM的接口不能直接與現今的微處理器和DSP的存儲器接口相連,需要在其間插入控制器實現微處理器或DSP對存儲器的控制。

2019-07-02 08:03:00 4051

4051

了SDRAM作為緩存器件。來自多個輸入通道的數據在采集后需要暫時存儲在SDRAM中,處理后的數據也需要存儲在SDRAM中,再輸出到輸出通道中。在SDRAM與多個輸入輸出通道之間,采用多個雙口RAM作為

2020-06-01 07:08:00 2577

2577

實現數據的高速大容量存儲是數據采集系統中的一項關鍵技術。本設計采用Altera 公司Cyclone系列的FPGA 完成了對DDR SDRAM 的控制,以狀態機來描述對DDR SDRAM 的各種時序

2019-08-14 08:00:00 3401

3401

,SDRAM的原理和時序,SDRAM控制器,動態隨即存儲器SDRAM模塊功能簡介,基于FPGA的SDRAM控制器的設計和實現,一種簡易SDRAM控制器的設計方法

2018-12-25 08:00:00 56

56 在DSP應用系統中,需要大量外擴存儲器的情況經常遇到。例如,在數碼相機和攝像機中,為了將現場拍攝的諸多圖片或圖像暫存下來,需要將DSP處理后的數據轉移到外存中以備后用。從目前的存儲器市場看,SDRAM由于其性能價格比的優勢,而被DSP開發者所青睞。DSP與SDRAM直接接口是不可能的。

2020-04-08 09:26:00 1268

1268

,SDRAM是非常流行的存儲器。它們不像靜態存儲器那樣容易控制,因此經常使用SDRAM控制器。 FPGA器件屬于專用集成電路中的一種半定制電路,是可編程的邏輯列陣,能夠有效的解決原有的器件門電路數較少的問題。FPGA的基本結構包括可編程輸入輸出單元,可配

2020-05-19 17:35:14 1833

1833

隨著目前數字技術的發展,多通道數據的高速采集處理獲得了廣泛的應用,面對大的數據吞吐量,往往需要共享一塊大的緩存空間(外掛的大容量存儲SDRAM或是DDR)。而大多時候多通道之間的實時數據流量并不一定

2020-11-20 15:54:54 635

635 在 DSP 應用系統中,需要大量外擴存儲器的情況經常遇到。例如,在數碼相機和攝像機中,為了將現場拍攝的諸多圖片或圖像暫存下來,需要將 DSP 處理后的數據轉移到外存中以備后用。從目前的存儲器市場

2020-12-22 13:16:00 5

5 針對SDRAM 操作繁瑣的問題,在對SDRAM 存儲器和全頁突發式操作進行研究的基礎上,提出一種簡易SDRAM 控制器的設計方法。該設計方法充分利用全頁式高效率存取的優點,對SDRAM 進行配置、全頁突發式讀寫時,操作方便。在實現sDRAM 的快速批量存儲方面,具有良好的應用價值。

2020-12-18 16:13:18 6

6 SDRAM與 Flash不同,它不具有掉電保持數據的特性,但其存取速度大大高于 Flash存儲器,且具有讀/寫的屬性,因此 SDRAM在系統中主要用作程序的運行空間,數據及堆棧區。當系統

2020-12-18 16:13:16 12

12 本文檔的主要內容詳細介紹的是使用FPGA讀寫SDRAM存儲器的實例工程文件和程序免費下載。

2020-12-18 16:13:13 10

10 的設計方法。結合實際系統,設計給出了使用FPGA實現 SDRAM控制器的硬件接口,在 Altera公司的主流FPGA芯片EPlC6Q240C8上,通過增加流水級數和將輸出觸發器布置在IO單元中,該控制器可達到185MHz的頻率。

2021-01-26 15:30:52 13

13 1.SDRAM使用越來越廣泛。

2.SDRAM具有存儲容量大,速率快的特點。

3.SDRAM對時序要求嚴格,需要不斷刷新保持數據。

.FPGA在電子設計中的廣泛應用,使用十分靈活利用FPGA來設計自己的 SDRAM控制器。

2021-03-05 14:49:00 10

10 實現SCSI協議和硬盤存儲,通常需要有微處理器、DMA控制器、SCSI協議控制器、數據緩存器等硬件支持和相應的軟件控制模塊。而本系統。DMA控制通過對FPGA編程來實現。圖像數據存儲系統結構圖如圖l所示。

2021-03-16 14:52:10 2076

2076

基于FPGA的DDR3SDRAM控制器設計及實現簡介(arm嵌入式開發平臺PB)-該文檔為基于FPGA的DDR3SDRAM控制器設計及實現簡介資料,講解的還不錯,感興趣的可以下載看看…………………………

2021-07-30 09:05:51 7

7 基于FPGA的SDRAM控制器的設計與實現簡介(嵌入式開發工程師和基層公務員)-該文檔為基于FPGA的SDRAM控制器的設計與實現簡介文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-07-30 09:34:59 11

11 基于FPGA的DDR3SDRAM控制器設計及實現(嵌入式開發式入門)-該文檔為基于FPGA的DDR3SDRAM控制器設計及實現總結文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-07-30 13:07:09 35

35 在FPGA中對圖像的一行數據進行緩存時,可以采用FIFO這一結構,如上圖所示,新一行圖像數據流入到FIFO1中,FIFO1中會對圖像數據進行緩存,當FIFO1中緩存有一行圖像數據時,在下一行圖像數據來臨的時候,將FIFO1中緩存的圖像數據讀出,并傳遞給下一個FIFO

2022-05-10 09:59:29 3056

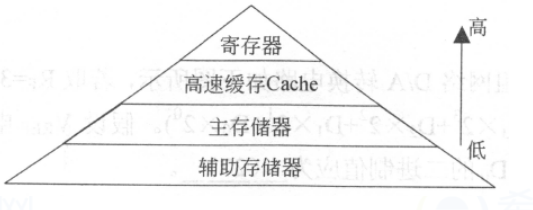

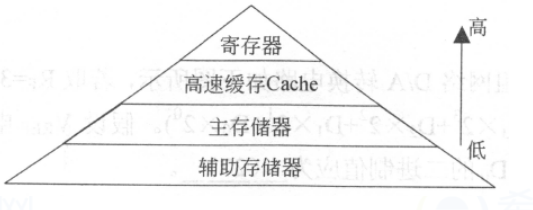

3056 ? ? ? 存儲系統的層次化結構可以分為5級:寄存器組、高速緩存Cache、主存、虛擬存儲器和外部存儲器。其中,寄存器組總是在CPU內部,程序員可通過寄存器名訪問,無總線操作,訪問速度最快;其余

2022-06-18 20:47:10 4738

4738

實時視頻SDRAM控制器的FPGA設計與實現

2022-12-30 09:21:26 3

3

電子發燒友App

電子發燒友App

評論