摘要:采用Lattice公司的在系統可編程器件pLSI/ispLSI1016,設計出一個具有可變格式、可變長度和可變速率的通信數字信號源,從而可以產生出符合設計者要求的數字碼流。

可編程邏輯器件(PLD)在工業、自動控制、信號處理和日常生活等方面都發揮著愈來愈大的作用。isp(在系統可編程)器件就是PLD中的一朵奇葩,它以其良好的系統性能、較強的設計靈活性、較高的邏輯利用率和優越的E2CMOS工藝而得到了電路設計者們的青睞。本設計就是采用Lattice公司的高密度在系統可編程芯片pLSI/ispLSI1016設計的一個通信數字信號源。設計中采用兩套地址總線(微機總線與isp總線)分時對兩片RAM進行讀寫操作,并采用不斷查詢端口的方式進行協調控制,從而產生出滿足設計要求的數字碼流。

1 isp系統介紹

1.1 概述

在系統可編程器件是近幾年來興起的一種PLD器件。所謂在系統可編程,是指在用戶自己設計的目標系統中或線路板上為重構邏輯器件進行編程或反復編程的能力。常規PLD通常是先編程后裝配,而采用isp技術的PLD則是先裝配后編程,成為產品之后還可反復編程。在系統可編程器件的出現使得當今數字電子系統設計的面貌煥然一新。采用isp技術之后硬件設計可以變得象軟件那樣靈活而易于修改,硬件的功能可以實時地加以修改或按預定程序改變組態,這不僅擴展了器件的用途,縮短了系統調試周期,而且還省卻了對器件單獨編程的環節和器件編程設備,簡化了目標設備的現場升級和維護工作。isp是美國Lattice半導體公司生產的可編程邏輯器件的專用商標,該公司生產的PLD在工藝上吸收了E2PROM的浮柵技術,并與CMOS靜態RAM相結合,開拓了能長期保持數據的E2CMOS技術。目前所有的GALpLSI/ispLSI都應用了Lattice公司的高速UltraMOS E2CMOS技術。Lattice公司已將其獨特的isp技術應用到它的高密度可編程邏輯器件(HDPLD)中,形成ispLSI系列高密度在系統可編程邏輯器件,使得isp成為新產品研制和開發的理想工具。

1.2 isp器件的特點

可編程邏輯器件的在系統編程能力必將更新人們設計、制造和維護電子系統的方法,具有如下特點:

·在系統編程允許用戶“在系統之中”編程或修改邏輯設計,而無需將器件從線路板上拆上拆下。這就加速了系統和線路板的調試過程,便于用戶在設計過程中更早地確定線路板的布局。

·當對傳統的PLD器件進行編程時,其測試、制造過程總是免不了人工處置。采用ispLSI器件之后,可以將芯片直接焊接在印刷電路板上,然后再進行編程或改寫。這就保證了調試制造過程中絕不會損傷器件的引腳。

·ispLSI器件在焊接到印刷電路板上之后,仍可毫不困難地修改其邏輯功能,于是用戶可在同一塊電路板上實現各種硬件結構。

·通過軟件重構系統,ispLSI器件的現場改寫只需從磁盤裝入或通過調制解調器送入結構文件,實現起來非常容易,而且還可實現遠距離遙控編程。

·所有ispLSI器件都為用戶提供了一個保密位來防止對片內編程模式的非法復制。保密位僅能在芯片改寫時被擦除,因而一旦被編程后就無法讀出芯片內原有的內部結構。

此外ispLSI器件也可以用市售的通用邏輯編程器來進行編程。

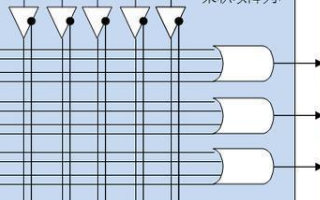

1.3 pLSI/ispLSI1000系列的結構及特點

pLSI/ispLSI邏輯塊的基本單位是萬能邏輯塊(GLB),這種萬能邏輯塊由四個輸出邏輯宏單元(OLMC)組成。每個GLB中有18個輸入、一個可編程的與/或/異或陣列和4個輸出。GLB的輸入來自于集總布線區(GRP Global Routing Pool)和直通輸入。所有GLB的輸出都送至集總布線區,因此可使它們與器件中其它GLB的輸入相連,如圖1所示。

由8個GLB、16個I/O單元和兩個直通輸入互相連接而構成一個大塊(Megablock)。這8個GLB的輸出通過輸出布線區(ORP The Output Routing Pool)被連至16個通用I/O單元。每一個大塊共享一個輸出使能控制信號。

pLSI/ispLSI器件由于邏輯輸入端多,邏輯塊劃分較細膩而優越于一般的可編程邏輯器件。它之所以設計靈活,邏輯利用率高,是由于它具有靈活的布線資源和可供選擇的宏單元時鐘,還有輸入寄存器和豐富的使能信號。pLSI/ispLSI器件編程速度快,出廠前100%經過測試,因此在系統編程能力、質量、可靠性和生產率方面都領先于一般的PLD。對于pLSI/ispLSI1016而言,它包括96個寄存器、4個直通輸入、3個直通輸入時鐘和一個集總布線區。isp1016具有5V在系統編程和在系統監測能力。isp1016共包括2個大塊,內含16個GLB。該器件同時具有32個I/O單元和4個直通輸入,它們都直接連至I/O引腳。每一個I/O單元都可以單獨編程為組合輸入、寄存器輸入、鎖存器輸入、輸出或是具有三態控制的雙向I/O引腳。

2 系統設計原理及框圖

2.1 設計原理

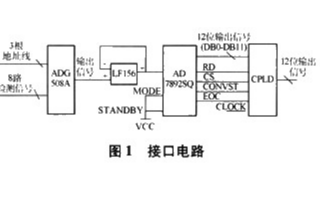

本設計的任務是設計一個數字信號源。要求碼長可變;數據格式是可以符合任何一種建議的數據格式;碼速率可調且在1~10Mbps之間。為此,在設計之初采用了以下方案,框圖如圖2所示, 其中八分頻電路,可置數的地址計數器電路及并/串轉換電路由isp器件編程實現。為了實現碼速在1~10Mbps之間可調,特采用DDS器件產生出1~10MHz的正弦波信號,經過整形及濾波電路而形成方波,即主控時鐘CLK信號。主控時鐘經過8分頻電路而形成CLK0信號,它成為可置數的地址計數器的計數脈沖。同時CLK0信號經過反相成為并/串轉換電路的置入(采樣)脈沖信號fsa,而CLK 信號經過反相成為并/串轉換電路的時鐘信號fcp,這樣CLK信號的速率就決定了所產生的數據碼流的速率。在EPROM存儲器中存放著符合一定數據格式的數據。這樣由可置數的地址計數器循環地長度可變地讀出EPROM中的數據(以byte為單位),經過并/串轉換電路便產生了碼長可變、碼速可變的數字碼流。

其中八分頻電路,可置數的地址計數器電路及并/串轉換電路由isp器件編程實現。為了實現碼速在1~10Mbps之間可調,特采用DDS器件產生出1~10MHz的正弦波信號,經過整形及濾波電路而形成方波,即主控時鐘CLK信號。主控時鐘經過8分頻電路而形成CLK0信號,它成為可置數的地址計數器的計數脈沖。同時CLK0信號經過反相成為并/串轉換電路的置入(采樣)脈沖信號fsa,而CLK 信號經過反相成為并/串轉換電路的時鐘信號fcp,這樣CLK信號的速率就決定了所產生的數據碼流的速率。在EPROM存儲器中存放著符合一定數據格式的數據。這樣由可置數的地址計數器循環地長度可變地讀出EPROM中的數據(以byte為單位),經過并/串轉換電路便產生了碼長可變、碼速可變的數字碼流。

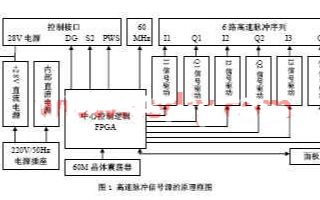

但是,考慮到EPROM編程及擦寫的過程比較繁瑣,數據不易改寫,靈活性及通用性較差,因此,經過比較決定采用第二種方案。其框圖如圖3所示。

在第二種方案中,isp器件仍由編程實現八分頻電路、地址譯碼器電路及并/串轉換電路的功能。圖3中, 端口電路的作用主要是通過不斷查詢B15的狀態,從而控制兩片RAM的讀寫進程。控制電路主要包括地址線選擇控制,存儲器片選控制,讀寫及輸出使能端控制以及總線驅動控制等。設計中采用兩片RAM進行分時讀寫操作,這樣做的目的是使數據信號的設計具有更大的靈活性。當微機對RAM1進行寫操作的同時,由isp器件中的地址計數譯碼對RAM2進行讀操作,讀出的數據經isp內并/串轉換部分而輸出數據信號OUT;同樣地,當微機對RAM2進行寫操作的同時,由isp器件中的地址計數譯碼對RAM1進行讀操作,讀出的數據經isp內并/串轉換部分而輸出數字信號流OUT。如此往復循環,從而方便靈活地產生出符合設計要求的數字碼流。

端口電路的作用主要是通過不斷查詢B15的狀態,從而控制兩片RAM的讀寫進程。控制電路主要包括地址線選擇控制,存儲器片選控制,讀寫及輸出使能端控制以及總線驅動控制等。設計中采用兩片RAM進行分時讀寫操作,這樣做的目的是使數據信號的設計具有更大的靈活性。當微機對RAM1進行寫操作的同時,由isp器件中的地址計數譯碼對RAM2進行讀操作,讀出的數據經isp內并/串轉換部分而輸出數據信號OUT;同樣地,當微機對RAM2進行寫操作的同時,由isp器件中的地址計數譯碼對RAM1進行讀操作,讀出的數據經isp內并/串轉換部分而輸出數字信號流OUT。如此往復循環,從而方便靈活地產生出符合設計要求的數字碼流。

由于設計中采用兩套地址總線進行分時讀寫操作,而分時讀寫操作的切換主要是利用ispLSI1016中地址計數譯碼電路的最高位—B15。在整個工作期間,兩片RAM都應處于被選中的狀態,即片選信號均應為低電平。當微機對一片RAM進行寫操作時,要保證ispLSI1016對另一片RAM進行讀操作,每一片RAM都有2個雙向數據收發器74LS245與之相連接。其中一個固定為輸入→輸出,對應為ispLSI1016從RAM中讀出數據;另外一個固定為輸出→輸入,對應為微機向RAM寫數據。

由于寫操作是通過編程由微機控制的,速度較快,而讀操作是由ispLSI1016控制的,速度較慢,這就很有可能出現讀寫操作的混亂。為了防止這種情況的發生,在設計中增加了端口電路部分。我們可以在系統程序中增加一段不斷查詢端口的語句,而標志位就為B15(因為對一片RAM而言,B15信號電平的改變就意味著讀寫狀態的改變)。當查詢到標志位發生改變時,立即進行下一輪讀寫;當查詢到標志位不變時,繼續查詢,直至其發生改變為止,然后進行下一輪讀寫。

對于ispLSI1016的時鐘輸入,可以使用DDS?直接數字頻率合成?構造一個可變頻率的正弦波產生電路,然后再進行波形變換而形成一個方波脈沖信號。但是為了簡單起見,也可使用一個4MHz的晶體和基本門電路搭成一個具有一定頻率穩定度的方波產生電路。

前面已經提到過ispLSI1016由編程實現八分頻電路、地址計數譯碼電路、并/串轉換電路的功能。其中八分頻電路可以看作是一個3位的計數器,它的進位信號就是外部輸入時鐘的八分頻信號;地址計數譯碼電路也可以看作是一個16位的地址計數器,它的低15位就是作為輸出的地址信號,它的最高位B15是做為控制信號來使用的;并/串轉換電路可以看作是一個八位的移位寄存器,它的移出信號就是所要產生的數據碼流信號。

2.2 系統程序設計

系統程序主要完成以下功能:由微機將符合一定建議數據格式的數據寫入RAM中,查詢端口的狀態并完成相應的操作,結束系統的工作等。系統程序流程圖如圖4所示。

3 isp編程設計

3.1 在系統編程原理

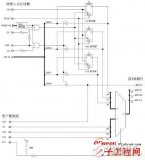

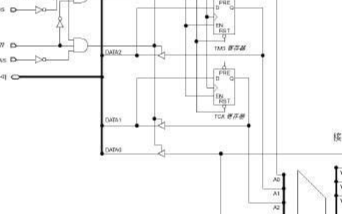

ispLSI器件的編程是由片內狀態機控制的,狀態的輸入即為進入片內的五個編程接口信號。圖5給出了在系統編程電路的典型結構。

圖中編程信號來自專門的在系統編程控制電路。編程過程即為把JEDEC形式的熔絲圖傳送到器件中的過程。ispLSI器件有兩種模式:正常工作模式與編程模式。器件的工作模式是由在系統編程使能信號ispEN控制的。ispLSI器件一旦進入編程模式,器件的編程操作就完全受片內isp狀態機控制。在五個編程控制信號中,ispEN信號用來使能或取消其他四個編程控制信號。它們是:數據串入信號SDI、模式控制信號MODE、數據串出信號SDO和串行時鐘信號SCLK。在SCLK的作用下,來自JEDEC文件的編程信息通過SDI端口串行地移入器件,同時通過SDO端口移出。SCLK同時也驅動片內狀態機工作。當器件處于正常工作模式時,4個編程控制信號端口可以用作普通的直通輸入端。對ispLSI器件編程有多種方法。其中最簡單的是直接把isp編程引腳當作專用的編程端口。用如圖5那樣的并行編程結構來進行編程。

3.2 設計軟件簡介

如前所述,isp由編程實現八分頻電路、地址計數器電路以及并/串轉換電路的功能。在這里對isp編程采用原理圖設計法,即先設計出滿足上述功能的原理圖,然后生成JEDEC形式的熔絲圖,再寫入isp器件中。

我們使用的繪制原理圖的軟件為OrCAD System公司的OrCAD/SDT IV。需要注意的是,因為要使用OrCAD Systems公司的WDOWNLD軟件包進行對ispLSI1016的編程寫入,所以在繪圖時要采用庫LSC.LIB(Lattice Semiconductor Corporation Library)中的元件。也就是說,要使用LSC庫中基本邏輯門和D觸發器來繪制出具有上述三種功能的isp編程原理圖。 在原理圖繪制完畢之后,就可以用OrCAD/SDT IV中的網絡表制作功能生成網絡表.EDN文件,此時還可使用OrCAD/VST進行數字電路的邏輯模擬。在電路連接網表文件生成以后,就可以使用pDS+ OrCAD Software軟件包生成JEDEC形式的熔絲圖文件了。有關pDS+ OrCAD Software的資料請參考文獻[4]。當具有標準JEDEC格式的熔絲圖文件生成以后,就可以使用WDOWNLD軟件包(即DOWNLOAD for Windows)對isp器件進行編程寫入了。下載電纜線是專用的ispDOWNLOAD CABLE,它的一端是25針的并行接口,另一端是一個8腳的插座。對WDOWNLOAD軟件感興趣的讀者請參考相關的資料。

在原理圖繪制完畢之后,就可以用OrCAD/SDT IV中的網絡表制作功能生成網絡表.EDN文件,此時還可使用OrCAD/VST進行數字電路的邏輯模擬。在電路連接網表文件生成以后,就可以使用pDS+ OrCAD Software軟件包生成JEDEC形式的熔絲圖文件了。有關pDS+ OrCAD Software的資料請參考文獻[4]。當具有標準JEDEC格式的熔絲圖文件生成以后,就可以使用WDOWNLD軟件包(即DOWNLOAD for Windows)對isp器件進行編程寫入了。下載電纜線是專用的ispDOWNLOAD CABLE,它的一端是25針的并行接口,另一端是一個8腳的插座。對WDOWNLOAD軟件感興趣的讀者請參考相關的資料。

經過上述步驟,pLSI/ispLSI1016就成為一個具有一定功能的邏輯器件了,我們也就可以在系統電路板上使用它了。

總之,美國Lattice 公司將“在系統可編程(isp)”技術應用到高密度可編程器件中,形成既有可編程邏輯器件(PLD)的性能與特點,又有現場可編程邏輯陣列(FPGA)高密度和靈活性的在系統可編程邏輯器件。本設計就是對這種器件進行了一定的開發及應用,設計出一種通用數字信號源。有關isp器件的開發及應用還值得我們作進一步的探索。

- 采用可編(5093)

- 字信號源(4862)

相關推薦

基于可編程邏輯器件和VHDL語言實現算術邏輯單元的設計

2066

2066

16個信號源設計總結

可編程邏輯器件

可編程邏輯器件發展歷史

可編程邏輯器件和ASIC,兩者有什么不同區別?

DDS工作原理是?用DDS芯片AD9858寬帶雷達信號源要設計最佳?

FPGA零基礎學習:半導體存儲器和可編程邏輯器件簡介

PLD可編程邏輯器件

Xilinx可編程邏輯器件的高級應用與設計技巧絕版教程

專家都是如何使用超低功耗的復雜可編程邏輯器件(CPLD)的?

什么是可編程邏輯

基于EDA技術的可編程邏輯器件在數字信號處理系統中的應用

如何采用可編程邏輯器件和A/D轉換器組成高速數據采集卡?

怎么采用可編程邏輯器件設計可變通信數字信號源?

求一種可利用復雜可編程邏輯器件設計技術實現的專用鍵盤接口芯片方案

電子發燒友出品《可編程邏輯器件特刊》全球首發 免費下載

請教器件可編程的基本概念

可編程器件與MAX+plusII簡介

19

19采用可編程邏輯器件EPM7032實現自動

60

60可編程邏輯器件在積分式A/D轉換器中的應用

28

28可編程邏輯器件

0

0可編程邏輯器件應用設計技巧100問

41

41采用可編程邏輯器件器件設計可變格式和可變速率的通信數字信號源

18

18可編程邏輯器件資料

0

0基于復雜可編程邏輯器件(CPLD)的120MHZ高速AD采集

39

39可編程邏輯器件基礎及應用實驗指導書

29

29基于單片機的復雜可編程邏輯器件快速配置方法

749

749

第三十二講 可編程邏輯器件及應用

1333

1333

可編程邏輯器件在高準確度A/D轉換器中的應用

781

781

什么是PLD(可編程邏輯器件)

14281

14281

采用可編程邏輯器件器件設計可變格式和可變速率的通信數字信號源

547

547

基于可編程邏輯器件的數字電路設計

1473

1473

基于并口通訊的雙路高速可編程數字及模擬信號源設計

952

952

萊迪思發運MachXO可編程邏輯器件達7千5百萬片

663

663可編程邏輯器件的基本結構及電路表示方法

5178

5178

可編程邏輯器件技術_pld技術

基于LPC2132數字信號源的設計與實現

85

85Xilinx可編程邏輯器件的高級應用與設計技巧(孫航)

249

249可編程邏輯器件的詳細分析分類和輸出結構

3653

3653干貨!使用嵌入式處理器對可編程邏輯器件重編程

1458

1458

可編程邏輯器件與FPGA的發展(1)

5847

5847可編程邏輯器件PLD介紹

1471

1471FPGA視頻教程之可編程邏輯器件基礎的詳細資料說明

9

9FPGA視頻教程:可編程邏輯器件基礎

2075

2075

關于可編程邏輯器件的分析和應用

3097

3097簡析復雜可編程邏輯器件的工作原理

4769

4769

可編程邏輯器件向什么目標前進

533

533利用嵌入式處理器對可編程邏輯器件進行重編程

1294

1294

采用復雜可編程邏輯器件實現多路信號采集系統的設計

1259

1259

什么是可編程邏輯器件

7379

7379可編程邏輯器件的分類有哪些

26761

26761基于可編程邏輯器件和VHDL語言實現信號源的方案設計

1116

1116

可編程邏輯器件和ASIC對比介紹

2383

2383PLD可編程邏輯器件的原理詳細講解

33

33FPGA CPLD可編程邏輯器件的在系統配置方法

13

13一文詳細了解可編程邏輯器件(PLD)

5304

5304電可編程邏輯器件EPLD是如何設計的

935

935可編程邏輯器件測試方法

659

659

可編程邏輯器件測試

404

404

可編程邏輯器件有哪幾種 fpga和cpld的特點

1360

1360什么叫可編程邏輯器件 可編程邏輯器件有哪些特征和優勢?

1105

1105 電子發燒友App

電子發燒友App

評論