越來越多的設計正向混合信號發展,IBS公司預測顯示,到2006年所有集成電路設計中有73%將為混合信號設計。目前混合信號技術成為EDA業內最為熱門的話題。深亞微米及納米技術的發展促使芯片設計與制造由單個IC、ASIC向SoC轉變,現在SoC也由數字SoC全面轉向混合SoC,成為真正意義上的系統級芯片。混合信號設計可以減少成本,減小電路外形尺寸,并提供更好的功能。

芯片驗證占芯片設計50%到70%的工作量,大量的人力、硬件以及時間資源都消耗在驗證上。隨著芯片復雜度上升,驗證工作無論從復雜性或工作量上都在呈指數上升。因此,驗證技術是混合信號技術的關鍵所在。

人們很難明確區分具備少許數字功能的模擬芯片或能夠實現某些模擬功能的數字芯片與混合信號芯片的區別。即使在工藝上,模擬芯片也越來越多采用CMOS工藝取代傳統的BiCMOS工藝。混合信號集成電路的標準應該是它在數字和模擬方面都具備重要功能,而不簡單的是在數字芯片中嵌有一些模擬電路或者模擬芯片中嵌入一些數字電路。

對于中國的集成電路設計師來說,混合信號設計的概念雖然早已有之,但真正使用混合信號設計的技術并不多,大多只是采用傳統的方法,比如數字部分用HDL寫好,然后進行仿真、綜合、布局布線;模擬部分畫出電路圖,用Spice仿真在進行版圖設計;最后將兩部分拼接在一起。而真正的混合信號設計需要結合數字和模擬,作整體上的考慮以及驗證,需要更靈活的設計思路。

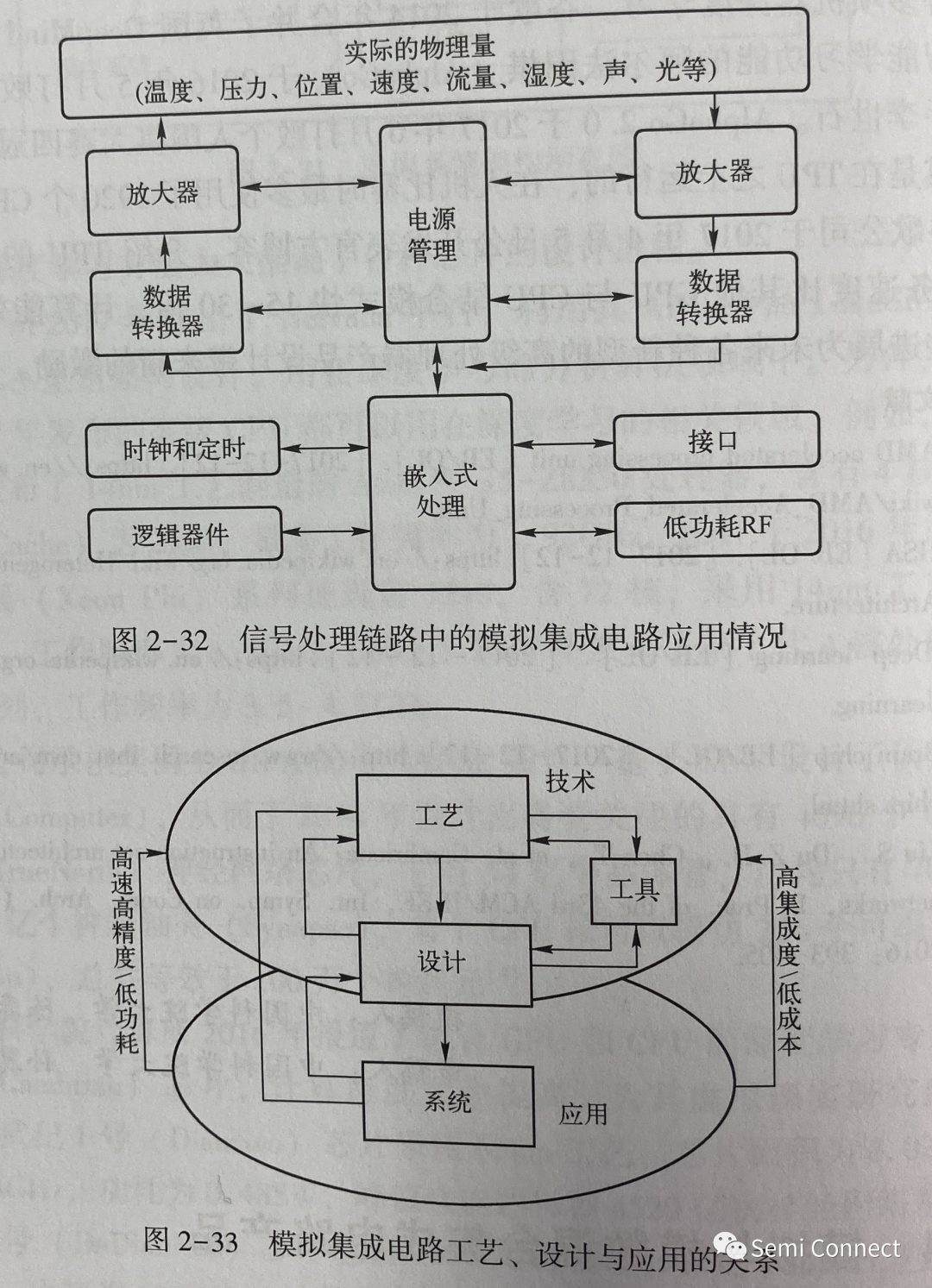

混合信號SoC設計面臨這樣的挑戰:行為級的數字與晶體管級的模擬的混合、HDL語言驅動的數字與原理圖驅動的模擬的混合、自上而下的數字與自下而上的模擬的混合。它不再是傳統的數字設計或者傳統的模擬設計,也不是數字設計與模擬設計的簡單疊加,混合信號設計提出了新的設計概念,必須使用全新的設計流程。

ADMS解決方案

EDA公司已充分意識到這一技術需求,領先的三大供應商——Mentor Graphics、Synopsys和Cadence在幾年前就開始整合或研發模擬和混合信號工具和技術。下面我們以Mentor Graphics的混合驗證平臺Advance MS(ADMS)為例說明它是如何解決混合信號設計難題的。

在了解ADMS之前,我們先來看看與ADMS相關的幾個EDA設計工具。

1. HDL仿真工具ModelSim

ModelSim是目前最流行的數字仿真器,早已被中國用戶所熟悉,其成熟技術眾所周知,這里不作具體介紹。

2. SPICE仿真工具Eldo

模擬電路設計最重要的部分即在電路仿真部分。SPICE的全稱為Simulation Program on IC Emphasis,由美國加州大學伯克萊分校創建于上世紀70年代,從此成為電路仿真的經典方法,現在的電路仿真基本上都采用SPICE方法。SPICE程序是公開源碼的,現在流行的各種版本SPICE都是由UCB SPICE衍生而來。HSPICE開發于1981年,是第一個成功的商用SPICE。Eldo則是最近幾年的SPICE新星,其研發組位于法國,在歐洲,基本上設計中使用的SPICE都是Eldo,最近Eldo也開始在北美及亞洲地區推廣。

評價一個仿真器可以從準確度、速度、容量、收斂性、控制界面、功能以及工藝廠商的支持等方面進行。

第一,準確度。Eldo通過基爾霍夫電流約束進行全局檢查,對收斂嚴格控制,保證了精度。Eldo在傳統SPICE使用的牛頓-拉普森(即NR)算法外,增加了OSR和IEM算法,新算法使得Eldo比傳統SPICE更為精確。

第二,速度。Eldo使用的新算法還增加了仿真速度,仿真速度達到一般SPICE的3到10倍。Eldo還可以對不同的電路子模塊采用不同的算法,比如對數字電路模塊采用速度快得多的OSR算法,大大提升了速度。尤其值得一提的是,Eldo本身還支持行為級的描述。從這個意義上看,Eldo不僅僅是一個SPICE,還是一個混合仿真器。

第三,容量。Eldo可以仿真大規模的電路,最大可以達到30萬個晶體管。

第四,收斂性。在收斂性上,Eldo采用了先進的技術如DC convergence引入的分割概念(在不收斂時對電路自動進行分割再組合,更改了Matrix),提升了收斂性。

第五,控制界面。Eldo的使用相當簡單。Eldo可以單獨使用(即命令行方式),也可以集成到電路圖編輯工具環境中,如Mentor Graphics的DA IC或者Cadence的Schematics Composer中。Eldo的輸入文件格式可以是標準的SPICE,也可以是HSPICE的格式。事實上,HSPICE的輸入文件,包括網表、控制語句、庫文件,不需要經過任何修改,即可由Eldo進行仿真。此外關于控制界面,Eldo還具有一個Shell,通過這個Shell,用戶可以中斷正在進行中的仿真,進行數據交換,調整仿真條件或參數設置,與Eldo進行互動。這樣解決了仿真一旦運行就不能進行任何控制的問題。

第六,功能。除了提供其它SPICE幾乎全部的功能外,Eldo本身擁有自己獨特的功能。Eldo擁有全面的分析功能,還可以進行各種參數的掃描。Eldo還可以進行RC Reduction、保存與續仿真等等功能。

第七,工藝廠商支持。電路仿真離不開具體工藝線的實際情況,SPICE程序必須得到工藝廠商的支持。目前世界上大多數代工廠商都開始支持Eldo,如臺積電、臺聯電、特許半導體、ST等。用戶還可以使用自己定義的Model。此外,由于Eldo對HSPICE完全兼容,甚至到Model,Eldo用戶完全可以采用代工廠商提供的HSPICE的模型。

3. Mach

SPICE仿真的特點是精度高、速度慢。做模擬電路設計時,用SPICE仿真一般可以滿足要求。但是當電路規模增加、尤其是增加了晶體管級描述的數字電路部分之后,SPICE顯得過慢。相同的仿真條件下,SPICE的仿真時間隨著晶體管的增加甚至不是線性上升,而是呈指數次方上升。這樣電路仿真成為設計的瓶頸,這一點在后仿真階段也經常遇到。

于是Mach作為Fast-SPICE應運而生。Mach在Eldo的基礎上,通過查表方式的晶體管模型迅速提高了仿真速度。相比Eldo,Mach可以將仿真速度提升10~1,000倍。速度提升犧牲的是精度,不過損失的精度能夠控制在3%之內。Mach的處理容量也是非常巨大的,最大可以達到2,000萬個器件。于是對于一些精度要求不是非常嚴格的設計,當需要快速驗證時,Mach成為必需,如存儲器設計。

ADMS是一個混合信號驗證平臺,集成了以上三種工具的技術。對模擬電路部分,采用Eldo的仿真算法,或者Mach的快速仿真算法;對數字部分,采用ModelSim的仿真算法。但是ADMS并不是這些工具簡單拼起來,它有單一的內核引擎。

采用ADMS進行設計,傳統的數字設計流程和模擬設計流程被打散并重新組合,設計師可以在任何階段對電路進行驗證,數字設計和模擬設計通過ADMS組成一個整體。

最新發布的ADMS4.0版增加了SystemVerilog語言和SystemC支持,這使得ADMS支持的語言達到了八種,即VHDL、Verilog、SPICE、VHDL-AMS、Verilog-AMS、SystemVerilog、SystemC 以及C,涵蓋了目前大部分的集成電路設計語言。這使得用ADMS進行設計時方法靈活多變,而工具卻只有一個。輸入ADMS的文件可以只有一個,不管其中的內容是HDL、SPICE,還是C語言,ADMS都可以讀入,并自動進行處理,給出仿真結果,例如在模擬電路中引入一個HDL描述的IP,或者是工具附帶單元庫里的一個VHDL-AMS行為級描述的運放單元,各種語言可以無縫地組合到一起。

ADMS提供了靈活的使用方式。它既可以集成到Mentor Graphics的電路圖編輯工具DA-IC中,也可以集成到Cadence的Schematics Composer中(圖3),另外還可以單獨使用。應用時ADMS的界面與經典的ModelSim相似,操作簡單,其樹狀結構顯示使得整個設計一目了然。使用時只需要讀入輸入的各種文本文件(可以以數字結構為最頂端層次,也可以以模擬結構為最頂端層次),即可由ADMS進行仿真和調試。

ADMS的輸出文件可以被其它工具的多種波形觀察工具查看和計算,不過ADMS附帶有兩個功能強大的波形處理工具Xelga和EZwave,可以同時處理數字和模擬信號,并進行各種操作與運算。

Eldo RF在Eldo的基礎上發展而來,針對射頻電路使用了新的技術,ADMS也可以擴展到ADMS RF,成為針對射頻混合信號SoC設計的工具。

ADMS附帶了很多行為級描述的單元庫,稱為CommLib,其中包括三百多種常見的基本單元,如ADC、DAC、PLL、Σ-Δ、OP等等。各種庫提供了大量的接口參數供修改,在設計中可以直接調用這些單元庫,增加仿真速度,以及方便調試電路。CommLib還有一個“行為級模型校正”(BMC,Behavior Model Calibration)的功能,通過BMC以及ADMS的驗證,可以將所設計的電路圖抽象到行為級。在仿真的時候,行為級的仿真速度比晶體管級快1,000倍,這樣可以將部分電路抽象到行為級,從而增加仿真速度,并方便調試。抽象化技術在大規模電路設計中越來越得到頻繁應用。

本文小結

ADMS是一種真正意義上的模擬/混合仿真工具,它可提供全面的語言與設計方法支持。目前,中國真正在做混合信號設計的設計師雖然不多,但毫無疑問,正在逐漸增加。那么,究竟在什么樣的情況下,需要轉到混合信號設計呢?也許可以簡單地作這樣一個描述:當使用HDL仿真器的數字電路設計工程師面臨增長的模擬部分和模擬電路行為,卻苦于不足的模型以及仿真精度時;當使用SPICE或者FastSPICE的模擬電路設計工程師,面臨增長的數字復雜度以及大規模,苦于仿真速度過慢時。這些時候,采用混合信號設計,就可以提升設計速度和效率以及設計水平,并降低產品成本。

電子發燒友App

電子發燒友App

評論