RFID芯片的攻擊技術(shù)分析及安全設(shè)計(jì)策略

本文以采用磁耦合和CMOS工藝的RFID產(chǎn)品為例,簡(jiǎn)要介紹了此類芯片的構(gòu)成,在列舉各種破壞性/非破壞性攻擊手段的基礎(chǔ)上,從軟/硬件角度分析現(xiàn)有的各種安全措施如何在設(shè)計(jì)階段應(yīng)對(duì)這些攻擊,或使攻擊變得難以實(shí)施,以及如何避免不良的設(shè)計(jì)。

以前,人們普遍認(rèn)為由于采用了各種復(fù)雜的認(rèn)證算法、密鑰等來保護(hù)數(shù)據(jù)免受未獲授權(quán)使用,IC卡具有磁卡無法比擬的安全性能。但在上個(gè)世紀(jì)90年代中期,大部分的IC卡處理器都被成功地實(shí)施了反向工程,因此這個(gè)看法有了很大的改變。除了采用更新的設(shè)計(jì)技術(shù)以外,更重要的是在IC卡芯片設(shè)計(jì)與實(shí)現(xiàn)過程中考慮抗攻擊措施,以保護(hù)重要的數(shù)據(jù)不被非法使用。

非接觸IC卡(RFID)的出現(xiàn)是智能卡發(fā)展中的重要里程碑:它通過磁耦合或微波的方式來實(shí)現(xiàn)能量與信號(hào)的非接觸傳輸,從而有效地解決了接觸式智能卡使用機(jī)械電氣觸點(diǎn)產(chǎn)生的靜電擊穿、機(jī)械磨損、易受污染和潮濕環(huán)境影響等問題,被認(rèn)為是身份識(shí)別、公交票據(jù)、物流等方面的重要替代技術(shù)。沒有了裸露的電氣接觸節(jié)點(diǎn),RFID和接觸式IC卡產(chǎn)品相比,在安全性方面也有一定的提升,但是它沒有改變智能卡使用認(rèn)證算法和密鑰等安全手段的模式,因此并沒有從本質(zhì)上解決安全問題。需要借鑒接觸式智能卡安全設(shè)計(jì)上的成熟經(jīng)驗(yàn),才能避免重大技術(shù)失誤。

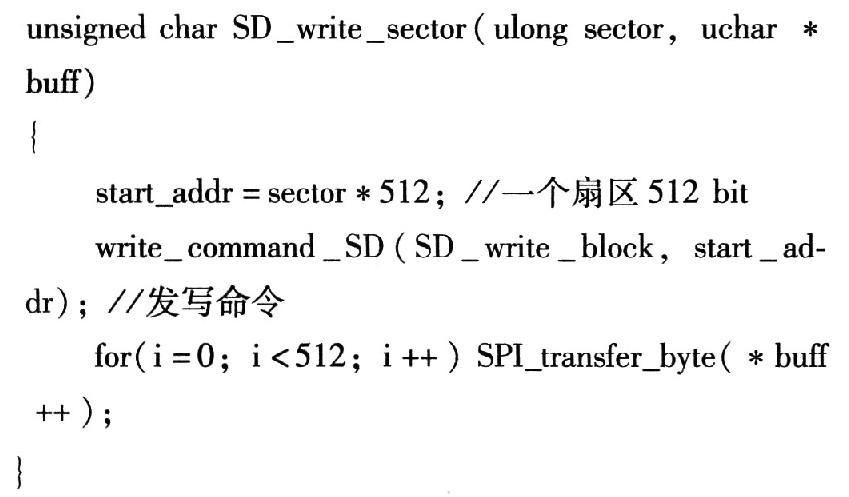

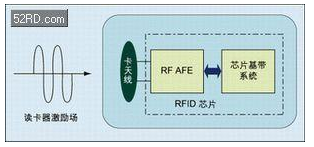

從結(jié)構(gòu)上講,RFID是一個(gè)包含射頻模擬前端(RF AFE)和基帶信號(hào)處理兩大部分的單片集成電路(見圖1)。基帶系統(tǒng)包括控制邏輯(甚至微處理器)和必要的存儲(chǔ)器,AFE部分是RFID的能量與信號(hào)接口,提供片上基帶系統(tǒng)工作所需的電源和時(shí)鐘等輔助信號(hào),完成數(shù)據(jù)的接收與發(fā)送功能。由于RF AFE屏蔽了智能卡片上的電源、時(shí)鐘、上電復(fù)位(POR)等信號(hào)與外界的聯(lián)系,在一定程度上減少了攻擊實(shí)施的點(diǎn),與接觸式智能卡相比在安全性方面有一定的提升。

智能卡芯片攻擊技術(shù)及應(yīng)對(duì)措施

根據(jù)是否破壞智能卡芯片的物理封裝可以將智能卡的攻擊技術(shù)分為兩大類:破壞性攻擊和非破壞性攻擊。

破壞性攻擊和芯片反向工程在最初的步驟上是一致的:使用發(fā)煙硝酸去除包裹裸片的環(huán)氧樹脂;用丙酮/去離子水/異丙醇完成清洗;氫氟酸超聲浴進(jìn)一步去除芯片的各層金屬。在去除芯片封裝之后,通過金絲鍵合恢復(fù)芯片功能焊盤與外界的電氣連接,最后可以使用手動(dòng)微探針獲取感興趣的信號(hào)。對(duì)于深亞微米以下的CMOS產(chǎn)品,通常具有3層以上的金屬連線,為了解芯片的內(nèi)部結(jié)構(gòu),可能要逐層去除以獲得重構(gòu)芯片版圖設(shè)計(jì)所需的信息。在了解內(nèi)部信號(hào)走線的基礎(chǔ)上,聚焦離子束(FIB)修補(bǔ)技術(shù)甚至可用于將感興趣的信號(hào)連到芯片的表面供進(jìn)一步觀察。

非破壞性攻擊主要針對(duì)具有微處理器的產(chǎn)品,其手段主要包括軟件攻擊、??技術(shù)和故障產(chǎn)生技術(shù)。軟件攻擊使用微處理器的通用通訊接口,尋求安全協(xié)議、加密算法以及他們物理實(shí)現(xiàn)的弱點(diǎn);??技術(shù)采用高時(shí)域精度的方法,分析電源接口在微處理器正常工作過程中產(chǎn)生的各種電磁輻射的模擬特征;故障產(chǎn)生技術(shù)通過產(chǎn)生異常的應(yīng)用環(huán)境條件,使處理器產(chǎn)生故障,從而獲得額外的訪問途徑。

智能卡的攻擊一般從破壞性的反向工程開始,其結(jié)論可以用于開發(fā)廉價(jià)和快速的非破壞性攻擊手段,這是最常見的最有效的智能卡攻擊模式之一。

1. 破壞性攻擊及其防范

a. 版圖重構(gòu)

破壞性攻擊的一個(gè)重要步驟是重構(gòu)目標(biāo)芯片的版圖。通過研究連接模式和跟蹤金屬連線穿越可見模塊(如ROM、RAM、EEPROM、ALU、指令譯碼器等)的邊界,可以迅速識(shí)別芯片上的一些基本結(jié)構(gòu),如數(shù)據(jù)線和地址線。

芯片表面的照片只能完整顯示頂層金屬的連線,而它是不透明的。借助于高性能的成像系統(tǒng),可以從頂部的高低不平中識(shí)別出較低層的信息,但是對(duì)于提供氧化層平坦化的CMOS工藝,則需要逐層去除金屬才能進(jìn)一步了解其下的各種結(jié)構(gòu)。因此,提供氧化層平坦化的CMOS工藝更適合于包括RFID在內(nèi)的智能卡加工。

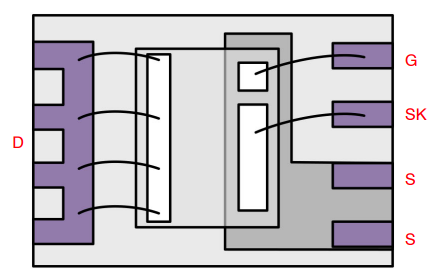

圖2是一個(gè)NAND門驅(qū)動(dòng)一個(gè)反向器的光學(xué)版圖照片,類似于該圖的不同層照片對(duì)于有經(jīng)驗(yàn)的人無異于電路圖。

對(duì)于RFID設(shè)計(jì)來說,射頻模擬前端需要采用全定制方式實(shí)現(xiàn),但是常采用HDL語言描述來實(shí)現(xiàn)包括認(rèn)證算法在內(nèi)的復(fù)雜控制邏輯,顯然這種采用標(biāo)準(zhǔn)單元庫綜合的實(shí)現(xiàn)方法會(huì)加速設(shè)計(jì)過程,但是也給反向工程為基礎(chǔ)的破壞性攻擊提供了極大的便利,這種以標(biāo)準(zhǔn)單元庫為基礎(chǔ)的設(shè)計(jì)可以使用計(jì)算機(jī)自動(dòng)實(shí)現(xiàn)版圖重構(gòu)。因此,采用全定制的方法實(shí)現(xiàn)RFID的芯片版圖會(huì)在一定程度上加大版圖重構(gòu)的難度。

版圖重構(gòu)的技術(shù)也可用于獲得只讀型ROM的內(nèi)容。ROM的位模式存儲(chǔ)在擴(kuò)散層,用氫氟酸(HF)去除芯片各覆蓋層后,根據(jù)擴(kuò)散層的邊緣就很容易辨認(rèn)出ROM的內(nèi)容(圖3)。

基于微處理器的RFID設(shè)計(jì)中,ROM中可能不包含任何加密的密鑰信息,但是它的確包含足夠的I/O、存取控制、加密程序等信息,這些在非破壞性攻擊中尤為重要。因此,對(duì)于使用微處理器的RFID設(shè)計(jì),推薦優(yōu)先使用FLASH或EEPROM等非易失性存儲(chǔ)器存放程序。

b. 存儲(chǔ)器讀出技術(shù)

對(duì)于存放密鑰、用戶數(shù)據(jù)等重要內(nèi)容的非易失性存儲(chǔ)器,它們不能通過簡(jiǎn)單的光學(xué)照片獲得其中的信息。在安全認(rèn)證過程中,至少訪問這些數(shù)據(jù)區(qū)一次,因此,可以使用微探針監(jiān)聽總線上的信號(hào)獲取重要數(shù)據(jù)。對(duì)于良好的設(shè)計(jì),簡(jiǎn)單重復(fù)認(rèn)證還不足以訪問存儲(chǔ)器所有的關(guān)鍵位置。例如,在同一個(gè)卡中使用不同的加密密鑰和加密算法,然后在它們之間每隔幾周就切換一次,芯片的算法和密鑰的存放區(qū)域在沒有被廣播呼叫激活以前不能被處理器控制等等,從而使早期的被動(dòng)監(jiān)測(cè)總線難以發(fā)現(xiàn)這些秘密。這些接觸智能卡IC的經(jīng)驗(yàn)可以應(yīng)用于RFID設(shè)計(jì)中。

一些文獻(xiàn)提到,為了保證存儲(chǔ)器數(shù)據(jù)的完整性,需要在每次芯片復(fù)位之后計(jì)算并檢驗(yàn)一下存儲(chǔ)器的校驗(yàn)結(jié)果,其實(shí)這種做法給攻擊提供了快速訪問全部存儲(chǔ)器的手段。

在使用帶微處理器的RFID中,還需要考慮軟件設(shè)計(jì)人員為提高代碼效率濫用CPU部件(如地址計(jì)數(shù)器)的行為所導(dǎo)致的安全問題。程序計(jì)數(shù)器在每個(gè)指令周期都自動(dòng)增量,如果被用于存儲(chǔ)器讀寫的地址發(fā)生器,攻擊中只需防止處理器執(zhí)行JUMP、CALL和RETURN等指令擾亂正常的讀順序即可。即稍微用激光切斷一些電路連接,改動(dòng)指令譯碼器、程序計(jì)數(shù)器電路即可實(shí)現(xiàn)完全訪問存儲(chǔ)器的目的。

頂層探測(cè)器網(wǎng)格是有效防止微探針獲取存儲(chǔ)器數(shù)據(jù)的重要手段之一,充分利用深亞微米CMOS技術(shù)提供的多層金屬,在重要的信號(hào)線頂層構(gòu)成探測(cè)器網(wǎng)格能夠連續(xù)監(jiān)測(cè)短路和斷路。當(dāng)有電時(shí),它能防止激光切割或選擇性的蝕刻去獲取總線的內(nèi)容。根據(jù)探測(cè)器輸出,芯片可立即觸發(fā)電路將非易失性存儲(chǔ)器中的內(nèi)容全部清零。這些網(wǎng)格對(duì)于其下的各層金屬連線重構(gòu)也有影響,因?yàn)槲g刻不是均勻的,上層金屬的模式在下層可見,會(huì)給版圖的自動(dòng)重構(gòu)帶來很多麻煩。手動(dòng)探針的目標(biāo)尺寸一般在1微米左右,尖端小于0.1微米的探針臺(tái)價(jià)格在幾十萬美元之上,且極難獲得。一個(gè)精心設(shè)計(jì)的網(wǎng)格將使手動(dòng)微探針攻擊難以實(shí)施,一般的FIB修補(bǔ)技術(shù)也難以逾越。

非破壞性攻擊及其防范

非破壞性攻擊主要針對(duì)具有微處理器的產(chǎn)品而言。微處理器本質(zhì)上是成百上千個(gè)觸發(fā)器、寄存器、鎖存器和SRAM單元的集合,這些器件定義了處理器的當(dāng)前狀態(tài),結(jié)合組合邏輯則可知道下一時(shí)鐘的狀態(tài)。許多類似系統(tǒng)的模擬效應(yīng)可用于非侵入式的攻擊,其中:

1. 每個(gè)晶體管和連線都具有電阻和電容特性,其溫度、電壓等特性決定了信號(hào)的傳輸延時(shí)。由于生產(chǎn)工藝參數(shù)的分散性,這些數(shù)值在單個(gè)芯片,或同種產(chǎn)品的不同芯片上差異很大。

2. 觸發(fā)器在很短的時(shí)間間隔內(nèi)采樣并和閾值電壓比較(與電源相關(guān))。采樣的時(shí)間間隔相對(duì)于時(shí)鐘邊沿是固定的,但不同的觸發(fā)器之間可能差異很大。

3. 觸發(fā)器僅在組合邏輯穩(wěn)定后的前一狀態(tài)上建立新的穩(wěn)態(tài)。

4. 在CMOS門的每次翻轉(zhuǎn)變化過程中,P和N管都會(huì)開啟一個(gè)短暫的時(shí)間,從而在電源上造成一次短路。沒有翻轉(zhuǎn)的時(shí)刻,則電源電流很小。

5. 當(dāng)輸出改變時(shí),電源電流會(huì)根據(jù)負(fù)載電容充放電變化。

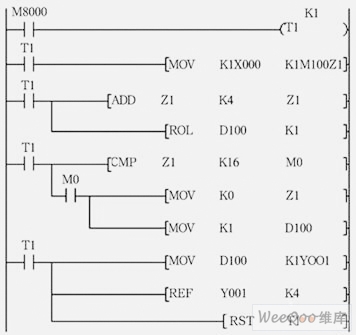

和接觸式IC卡不同的是,攻擊RFID的黑客不能完全控制其電源和時(shí)鐘線,理論上RFID針對(duì)非破壞性攻擊的安全性能有所改善,但是實(shí)際情形可能并非如此,仍會(huì)面臨一些危險(xiǎn)。常見的攻擊手段有電流分析攻擊和故障攻擊。

1. 電流分析攻擊

根據(jù)電流分析攻擊實(shí)施的特點(diǎn),可分為簡(jiǎn)單電源攻擊(SPA)和差分電源攻擊。

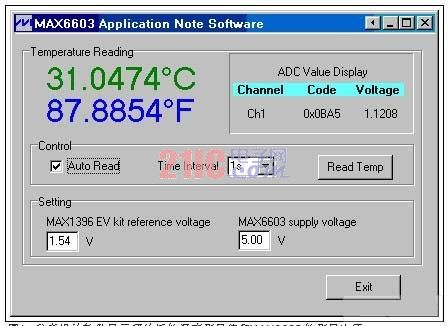

原則上,RFID的電源是集成在AFE的內(nèi)部,似乎遠(yuǎn)離了電流分析的危險(xiǎn),然而實(shí)際上并非如此。圖4顯示了RFID接觸法測(cè)試的原理圖:通過在RFID天線和串聯(lián)的分壓電阻兩端直接加載符合規(guī)格的交流信號(hào),RFID負(fù)載反饋信號(hào)可以百倍于無線模式下的信號(hào)強(qiáng)度直接疊加在加載的交流信號(hào)上。由于芯片的功耗變化與負(fù)載調(diào)制在本質(zhì)上是相同的,因此,如果AFE的電源設(shè)計(jì)不恰當(dāng),RFID微處理執(zhí)行不同內(nèi)部處理的狀態(tài)可能在串聯(lián)電阻的兩端交流信號(hào)上反映出來。

對(duì)于RFID而言,功耗是芯片設(shè)計(jì)過程中關(guān)心的重要問題,串聯(lián)方案的效率更高,更適合集成電路設(shè)計(jì)。但是就安全而言,并聯(lián)方案是更理想的選擇:通過并聯(lián)泄放電路將電源幅度和紋波的變化控制在盡可能小的范圍內(nèi),使電源電流消耗波動(dòng)抑制在整流電路之后。這樣天線兩端的交流信號(hào)不能反應(yīng)任何內(nèi)部基帶系統(tǒng)(主要是微處理器)狀態(tài)的差異。

2. 故障攻擊

通過故障攻擊可以導(dǎo)致一個(gè)或多個(gè)觸發(fā)器位于病態(tài),從而破壞傳輸?shù)郊拇嫫骱痛鎯?chǔ)器中的數(shù)據(jù)。在所知的CPU智能卡非破壞性攻擊中,故障攻擊是實(shí)際應(yīng)用中最有效的技術(shù)之一。當(dāng)前有三種技術(shù)可以可靠地導(dǎo)致觸發(fā)器病態(tài)且影響很少的機(jī)器周期:瞬態(tài)時(shí)鐘、瞬態(tài)電源以及瞬態(tài)外部電場(chǎng)。

通過簡(jiǎn)單地增加或降低時(shí)鐘頻率一個(gè)或多個(gè)半周期可以實(shí)施時(shí)鐘故障,這樣部分觸發(fā)器會(huì)在合法的新狀態(tài)到來之前采樣它們的輸入。時(shí)鐘故障有效的攻擊通常和電源故障結(jié)合在一起,在接觸式智能卡中通過組合時(shí)鐘和電源波動(dòng),已經(jīng)可以很可靠地增加程序計(jì)數(shù)器內(nèi)容而不影響處理器的其它狀態(tài)。這樣,智能卡內(nèi)的任意指令序列都可以被黑客執(zhí)行,而程序員在軟件編寫中并沒有什么很好的應(yīng)對(duì)措施。

大多數(shù)RFID的時(shí)鐘、電源都是使用天線的交流信號(hào)整形得到的,因此通過改變交流信號(hào)諧波的幅度、對(duì)稱性、頻率等參數(shù)可以實(shí)施時(shí)鐘-電源故障攻擊。借助于RFID接觸測(cè)試設(shè)備中的數(shù)字直接合成交流信號(hào)技術(shù),很容易產(chǎn)生時(shí)鐘-電源故障攻擊所需的波形。

RFID產(chǎn)品為了有效抵御時(shí)鐘故障攻擊,除了采用時(shí)鐘探測(cè)器以外,更重要的是嚴(yán)格限制RFID設(shè)計(jì)的工作頻率范圍、載頻的諧波品質(zhì)因素、對(duì)稱性等指標(biāo)。因此,從安全角度來說,并非RFID對(duì)機(jī)具適應(yīng)能力越強(qiáng)越好。

潛在的故障技術(shù)仍需進(jìn)一步探索,如通過將金屬探針置于處理器幾百個(gè)微米高度的時(shí)候,在幾個(gè)毫秒內(nèi)施加幾百伏的電壓,得到的電場(chǎng)強(qiáng)度足夠改變附近的晶體管閾值電壓。這些技術(shù)的應(yīng)用價(jià)值和應(yīng)對(duì)措施還有待進(jìn)一步的研究。

RFID的測(cè)試態(tài)及保護(hù)

對(duì)于一般意義的集成電路產(chǎn)業(yè)鏈條來說,需要將不良的芯片在晶圓測(cè)試階段剔除以減少后端加工工序中不必要的浪費(fèi),RFID芯片也不例外。根據(jù)RFID芯片的特點(diǎn),晶圓測(cè)試內(nèi)容包括:RF性能測(cè)試、邏輯功能測(cè)試和存儲(chǔ)器測(cè)試。和普通芯片一樣,如果借助于芯片應(yīng)用功能來進(jìn)行片上邏輯和存儲(chǔ)器測(cè)試,則測(cè)試成本將大幅增加。通常采取等效測(cè)試原理設(shè)計(jì)額外的測(cè)試態(tài)來快速完成。由于測(cè)試態(tài)提供了快速、全面訪問存儲(chǔ)器的機(jī)制,因此有必要在晶圓測(cè)試完成后,將測(cè)試態(tài)永久關(guān)閉。

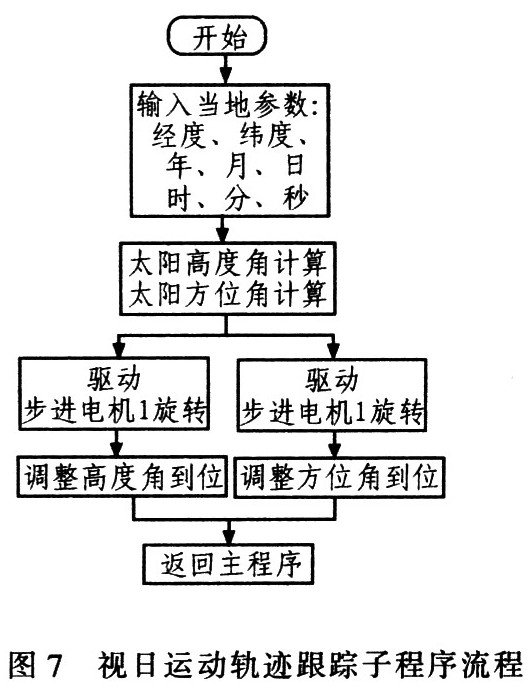

圖5a是在接觸式智能卡芯片的發(fā)展過程中曾大量采用的測(cè)試態(tài)控制方式:使用額外的I/O管腳和芯片內(nèi)部電路相連,該連線通過劃片槽,這樣芯片劃斷后就不能通過簡(jiǎn)單控制該管腳進(jìn)入測(cè)試態(tài)。由于FIB修補(bǔ)技術(shù)的出現(xiàn),這個(gè)手段已經(jīng)過時(shí)。圖5b是最有潛力的替代方案:在劃片槽和鄰近的芯片中設(shè)計(jì)部分控制電路,從而得到不可逆的測(cè)試態(tài)控制手段。

本文總結(jié)

本文對(duì)RFID芯片設(shè)計(jì)安全從破壞性、非破壞性攻擊以及測(cè)試態(tài)控制三個(gè)方面作了簡(jiǎn)單探討,通過與接觸式智能卡芯片安全設(shè)計(jì)比較,給出一些應(yīng)對(duì)的設(shè)計(jì)措施。然而仍然有很多安全設(shè)計(jì)措施不能一一列舉,如用于對(duì)付功率分析的電流調(diào)節(jié)器和噪聲負(fù)載。我國第二代居民身份證即將實(shí)施,這將是世界上最大的RFID項(xiàng)目,考慮其芯片設(shè)計(jì)安全問題具有重要的現(xiàn)實(shí)意義。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論