提升芯片投制設計的進度估算

芯片設計的進度經常估不準,連帶影響芯片的開發(fā)成本、芯片的上市時間、及上市后的銷售。許多芯片投制商(ASIC Supplier)會用總項目管理數據庫來估算芯片投制設計的進度。同時絕大多數的進度估算都認為,投制設計完成的時間取決于芯片設計的復雜度,而復雜度多以電路中的邏輯門數, 存儲器位數, 和時鐘頻率等來衡量。

然而,有家無晶圓廠的芯片投制在2008年完成一份芯片投制設計項目的內部研究,該研究顯示,芯片從交付netlist后開始進行投制設計,一直到產生GDSII數據庫后完成設計,此一投制過程時間的長短,其實與交付netlist的芯片設計商之成熟度密切關連。

舉例來說,一線芯片設計商與三線芯片設計商均交出最終定案的芯片netlist,且芯片的復雜程度相近,則三線芯片商必須比一線芯片商多等待一倍的時日才能取得投制完成后的GDSII成果。

以下本文將解說該芯片項目及其進度數據,了解為何一線與三線間為何有如此差異,并藉此啟發(fā)出更佳的規(guī)則、方法,以提升芯片設計進度的估算精確性。

本文所用的芯片投制項目進度數據,其項目的起訖認定,是從已完成最終定案的netlist開始,一直到GDSII數據庫產生為止,并以單一家芯片投制商于2008年間所承接、完成的項目為依據。該投制商于2008年共承接、完成28個項目,其中19個為一線(芯片設計)業(yè)者所委托,4個來自二線業(yè)者,另5個來自三線業(yè)者。

在此,一線業(yè)者指的是已良善確立其主要部門,或者是其芯片已形成一個或多個類群,且類群化已達高度成熟性。而三線業(yè)者指的是小規(guī)模的新創(chuàng)公司,并專注于發(fā)展及推行新技術、新(芯片)產品。至于二線業(yè)者則在各方面均介于一線與三線之間,包括規(guī)模性、(芯片)產品成熟性、產品線的廣度等等。請參考如下的表1,該表顯示出一線、二線、三線業(yè)者在芯片投制項目上的相關信息。

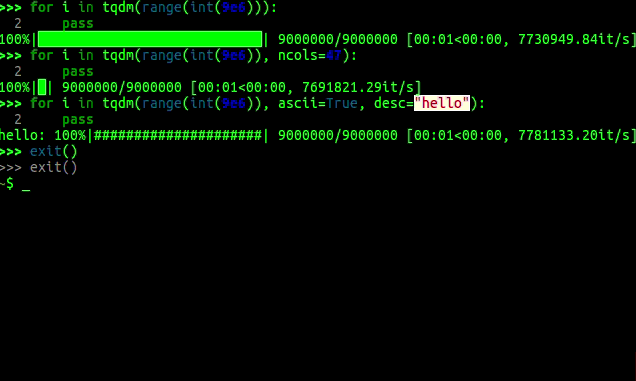

表1 從最終定案的netlist到產生GDSII的設計時間表

表1

從表中可知,一線、二線、三線業(yè)者從netlist到tapeout(指正式將芯片設計交由晶圓廠生產成芯片)的天數分別為31天、45天、61天。其中一線與三線間有較大的差異,此差異大于一線與二線間的差異,也大于三線與二線間的差異。而較大的差異性也意味著個中的分析將能有較大且確切的斬獲,因此以下本文將特別聚焦在一線與三線間的分析比較。

上表的數據也顯示,芯片投制設計項目的復雜度,極大程度取決于平均門數、平均存儲器位數、平均時鐘頻率等,關于此無論是一線、二線、三線業(yè)者均是相同的。

在平均門數方面,三線業(yè)者的用量較一線多出11%,若將此進行線性擴展對應,則會多增加3天的開制工程時間。平均存儲器位數方面也是一線與三線間有所差異,不過,存儲器個數(memory instance count)的差異所造成的影響,與內存在電路布局、芯片面積等方面的影響相比相對較小。即便如此,對三線業(yè)者的投制項目而言,所增加的電路布局上的工作及執(zhí)行投制設計的軟件工具運作時間等,也只會在整個項目中多增加幾天時間而已。

在頻率頻率方面,一線業(yè)者的平均頻率與三線業(yè)者的平均頻率相比,約僅高出8%,由于差異太小,難以看出是否此為影響投制進度時間的主要因素。另外,一線業(yè)者使用較先進的制程節(jié)點技術,如此會增加設計后的驗證心力,進而略增投制時間,不過使用舊制程的三線業(yè)者也會為了讓芯片有較佳的頻率表現(xiàn)而進行時序收斂(timing closure)的挑戰(zhàn)性設計,此亦同樣會略增投制時間。總體來說,一線與三線在投制設計上的差異太小,無法從中解釋為何一線與三線間有長達30天的項目進度落差。

表1的所有數據都來自同一家無晶圓廠的芯片投制商,所以表中的所有投制項目用的都是同一種設計方法、同一種設計流程,在邏輯閘用量上、電路配布的密度目標等也都是相近。進一步的,參與、投入投制設計的設計工作者的能力水平,以及由工作者構成的設計團隊等也都類似,而管理各設計團隊的則是同一組總項目管理團隊。

管理團隊追查所有芯片投制設計的主要設計復雜性部份,也追查一線與三線的芯片實現(xiàn)差異性等,均因差異過小而難以解釋為何項目進度時間有如此大的落差。唯一可解釋的是一線、三線業(yè)者所交付的定案版netlist有極大的不同,進而導致后續(xù)投制進度時間的大落差。因此接下來將探討一線與三線芯片設計商的設計工程團隊,試圖了解其是否為導致項目時程差異的主因。

由于一線與三線業(yè)者及其設計團隊業(yè)者有著太多的不同點,所以本文只專注在會影響netlist穩(wěn)定性、netlist質量方面的因素,此處的差異將對投制項目的進度造成極大影響、沖擊。許多一線業(yè)者的項目是以之前已完成的項目為基礎進行強化或升級,之前的項目能給新項目一個穩(wěn)定的基礎,同時在發(fā)展更高質量的netlist時能有更穩(wěn)當的發(fā)展路徑。

一線業(yè)者通常擁有內部自屬的實體電路設計團隊,如此他們可以決定投制工程的哪些部份要內部團隊自行完成,以及哪些部份要委外交由芯片投制商完成,一線業(yè)者自屬的內部實體電路設計團隊多用來支持公司內極先進的芯片設計項目,這類的項目需要緊密的工程回復與反應。若項目是以既有設計進行強化、升級,則很適合直接委外,這表示一線業(yè)者通常是將相對簡潔、穩(wěn)定的netlist委外設計(委給芯片投制商)。

另外,一線業(yè)者通常有詳整的項目定義,及開制設計完成后的接受性準則、依據,包括此次項目的訴求特點、規(guī)格、目標市場等,均經過仔細的檢視才批核。一旦一線業(yè)者批準并啟動一個設計項目,其主設計就極少再更動,如此設計目標的設計后的成效結果就相當穩(wěn)定,同時能進一步提升設計的穩(wěn)定性與質量。

相對的,多數的三線業(yè)者處于草創(chuàng)階段,正摸索發(fā)展與建立其(芯片)產品及(芯片)技術,在新產品、新技術的定義上沒有太多的過往設計可參考、倚賴。因此,與許多一線業(yè)者不同的,多數三線業(yè)者沒有太多的余裕來主掌現(xiàn)有的設計項目,多數三線業(yè)者也無法評斷是否該投資建立自屬的內部實體電路設計團隊,亦無法評斷是否該購買EDA(電子設計自動化)相關的電路布局、線路繞布等工具。

因此多數三線業(yè)者將實體電路的設計工作委外,有關實體電路的設計內容與技術成熟性等,均難有進一步的關注或涉入。為了投制出客戶交付的新的芯片設計和技術方案,三線業(yè)者就必須以更靈巧、彈性的手法來達成。

舉例而言,如果(但很有可能發(fā)生)有一個大客戶XYZ簽訂一紙合約,將大量采買新創(chuàng)公司ABC的芯片,可是ABC的芯片在封裝上卻不合乎大買家XYZ的需求,而ABC公司也找不到更有吸引力的買主或市場,這時ABC公司的設計團隊就必須停止現(xiàn)有的設計,并重新設計該芯片的I/O環(huán)(I/O Ring,指接近封裝接腳、接線的接口電路)來因應大買家所期望使用的封裝型態(tài)。如此原初設計的規(guī)格及netlist就必須更新,進而延誤netlist轉化成GDSII的時間。

另外,一線業(yè)者與三線業(yè)者在結構組成上也有所不同,一線業(yè)者通常有完整、近似的前案設計,也擁有既定的設計流程及具凝聚力的設計團隊,三線業(yè)者在設計流程上經常是設計團隊開發(fā)完電路后,也由同一組團隊進行設計除錯。進一步的,一線業(yè)者可以取用較多的工程資源與EDA工具,且隨著時間許多項目參與者可從中獲得學習,進而提升到不錯的水平。許多一線業(yè)者的工程師擁有比較專同時也比較深的經驗實務,不過多數項目多只用及少數關鍵工程師及具廣、深歷練的管理者,以此共同推動項目進行。

而三線業(yè)者,由于要保存現(xiàn)金流量及控管有限的創(chuàng)業(yè)資金,因此必須節(jié)省開銷,多數三線業(yè)者只擁有少數的關鍵工程師及具深廣經驗的管理者來投入項目。不過,三線業(yè)者通常缺乏傳統(tǒng)工程與EDA工具資源,以致沒有余力如一線業(yè)者般地執(zhí)行諸多具系統(tǒng)、條理、且詳整的設計確認,導致沖擊三線業(yè)者的netlist的質量、穩(wěn)定性。此外,三線業(yè)者的資源也只能進行有限的設計驗證、除錯、及問題排解,如此也延誤了netlist轉化成GDSII的時間進度。

以下我們將說明一種具啟發(fā)性的規(guī)則,該規(guī)則可協(xié)助我們強化進度推估。進度時程的推估向來詭譎多變,其中牽涉了項目時程的精準度或是現(xiàn)實性,此與企業(yè)文化息息相關,同時也與「業(yè)務、營銷團隊與研發(fā)團隊間的互動」息息相關。

有關進度推估,有的公司是實行一貫、固有的高度最佳化情境與假設來推算,又有的公司是致力于最大的進度精準度與可預測性來推算。如果有人很幸運的是在一家傾向于實行精準現(xiàn)實進度的芯片公司,則先取用一線業(yè)者的方式來進行進度估算,即是以邏輯閘用量、頻率、及內存容量等來推估,之后將此推估套用于二線、三線業(yè)者的設計時,則會往上追加時間。

舉例而言,二線業(yè)者且其營銷團隊、研發(fā)團隊均受過良好訓練,其進度估算就可逼近于一線業(yè)者的進度估算,而三線業(yè)者缺乏工程資源則必須延長設計時程,進而增加進度時間。

如果有個人所在的芯片公司,其進度是以一線到底式的瀑布流程為假設,即以高度最佳化的情境為設想,如此想強化進度估算的精準性就會出現(xiàn)極大的問題,有可能會在從高度最佳化進度到真實進度的突然轉變時, 遭遇公司內部強大的阻力。

為改善估算精準度,初始的工作應致力于將原本高度最佳化的進度調整成很積極但卻可行、合理的進度。

以上的討論傾向于反映出二線、三線業(yè)者中的不佳工程、營銷與業(yè)務團隊,多數公司里的多數設計、營銷及業(yè)務團隊都非常專注自有領域,并嘗試作出大的貢獻,但卻忽視了公司的處境。一線、二線、三線間的進度不同是由于公司情境的好壞因素,其影響性高過于控制設計、營銷、業(yè)務團隊。與其把心力用于強化、縮短芯片的設計時間,則更建議專注在規(guī)劃及問題排解,而不是對抗。

結論是,表中的28個委托投制案,其交托的客戶已歸為一線、二線、三線,同時也依不同線別來列出其委托案的平均設計復雜度。由表中可知,同樣的芯片投制商,同樣從交付netlist到完成GDSII,一線委托案所需的時日能比二線快約50%,而能比三線快約100%。所以,在此建議當修訂原有的時程估算方法,過去僅以邏輯門數、存儲器位數、時鐘頻率等技術復雜度的方式來估算芯片開制所需的時間,必須嘗試調整成以業(yè)者一線、二線、三線等區(qū)別來推估開制時間。

不過,每家公司及其投制工程團隊均有所不同,因此項目時程的修改、調整須以逐案、逐案累積而得的基礎來評斷,此亦成為一個有趣且值得深入探討的議題,包括不同線別業(yè)者的前段設計時間,以及項目啟動, 從接受初始netlist到GDSII完成的時間。

電子發(fā)燒友App

電子發(fā)燒友App

評論