SoC已經(jīng)一躍成為芯片設(shè)計(jì)業(yè)界的主流趨勢(shì),而產(chǎn)品價(jià)值與競(jìng)爭(zhēng)力則完全取決于復(fù)雜度、設(shè)計(jì)的可再用性,以及制程的良率。##即將進(jìn)行的第5次EDA產(chǎn)業(yè)變革,也就是平臺(tái)為主(Platform-based Design )的EDA工具的世代

2014-09-15 08:52:08 2044

2044 (Cliff Hou)表示,工程師需要能因應(yīng)今日芯片設(shè)計(jì)復(fù)雜性的新工具;而他也指出,針對(duì)四個(gè)目前的主要市場(chǎng),需要采用包括機(jī)器學(xué)習(xí)在內(nèi)之新技術(shù)、新假設(shè)的個(gè)別工具。

2017-02-09 08:36:41 2916

2916

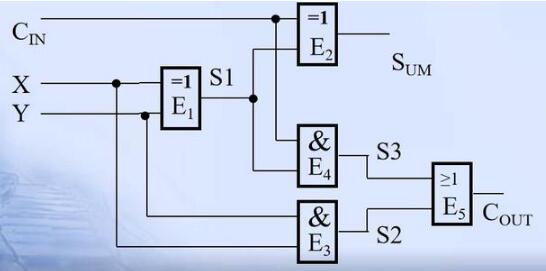

作者丨Robei君? 圖片 | Robei 沒(méi)有EDA,就沒(méi)有芯片,EDA是造芯的工具。 如果沒(méi)有EAD軟件,可能全球所有的芯片設(shè)計(jì)公司都得停擺,代工廠在進(jìn)行工藝研發(fā)與優(yōu)化時(shí)也將無(wú)工具可用。 01

2021-01-05 14:20:08 6060

6060

IC設(shè)計(jì)離不開(kāi)EDA工具的支持,模擬設(shè)計(jì)也不例外。在9月20日舉行的2019年中國(guó)模擬半導(dǎo)體大會(huì)上,Cadence中國(guó)區(qū)技術(shù)支持總監(jiān)欒志雨帶來(lái)了主題為《中國(guó)模擬IC升級(jí)更需要借力EDA工具》的演講。

2019-09-25 12:10:37 6856

6856 Robei推出最新的Robei 3.5.5 版本,采用工業(yè)級(jí)標(biāo)準(zhǔn)的設(shè)計(jì)與仿真,讓EDA設(shè)計(jì)不再繁雜。Robei一直以直觀、簡(jiǎn)單、易用為核心,為廣大客戶(hù)提供可視化、面向?qū)ο蟮膶?zhuān)業(yè)EDA工具。Robei

2022-02-10 17:37:59

越來(lái)越薄,柵極泄漏呈指數(shù)增長(zhǎng),最終動(dòng)態(tài)功耗等于亞閾值泄漏電流,也等于柵極泄漏電流。這就迫使業(yè)界必須從IC的設(shè)計(jì)端就開(kāi)始采用低功耗設(shè)計(jì)技術(shù)。為了應(yīng)對(duì)這些挑戰(zhàn),設(shè)計(jì)工程師們開(kāi)始提倡采用復(fù)雜的時(shí)鐘門(mén)電路開(kāi)關(guān)

2019-06-27 08:05:18

EDA工具使用教程Altium Designer Multisim見(jiàn)附件

2014-08-15 22:20:43

EDA工具手冊(cè),寫(xiě)的很實(shí)用,有興趣的可以看一下

2018-06-03 15:55:01

EDA技術(shù)是什么?EDA常用軟件有哪些?電子電路設(shè)計(jì)與仿真工具包括哪些呢?

2022-01-24 06:34:54

EDA鼠標(biāo)增強(qiáng)工具EDAHelper,布線(xiàn)輔助、鼠標(biāo)快捷工具,很好用的。通用工具,PROTEL,cadence都能用。 本軟件是多種EDA軟件的鼠標(biāo)增強(qiáng)工具,綠色單文件,支持Win9x/NT

2019-04-08 14:41:33

本篇文章主要針對(duì)應(yīng)對(duì)EMC/EMI設(shè)計(jì)挑戰(zhàn)的5個(gè)EDA仿真工具進(jìn)行詳細(xì)介紹,通過(guò)本篇文章讓各位工程師選出最適合自己的那款EDA仿真工具。

2020-11-02 08:39:47

FPGA和3D IC技術(shù)的發(fā)展,F(xiàn)PGA不斷在加速取代ASSP和ASIC,但這還需要更多的突破,其中最大的障礙就是互聯(lián)問(wèn)題,需在縱向架構(gòu)上“守正出奇”。此外,隨著FPGA系統(tǒng)復(fù)雜度的提升,競(jìng)爭(zhēng)已不僅僅是產(chǎn)品

2019-08-30 07:56:58

,這樣前256個(gè)周期的就會(huì)遍歷地非常快速,最后的周期的狀態(tài)空間就會(huì)爆炸。這種呈指數(shù)增長(zhǎng)的狀態(tài)空間是FPV復(fù)雜度問(wèn)題的主要來(lái)源,這也是阻礙我們使用FPV進(jìn)行完全收斂sign off的罪魁禍?zhǔn)住O啾菷PV,一般FEV所需要處理的復(fù)雜度相對(duì)比較小,但是依然是一個(gè)非常大的計(jì)算量和內(nèi)存空間。原作者:驗(yàn)證哥布林

2022-09-14 14:11:30

0185. 進(jìn)入系統(tǒng)后就可以正常的使用 Synopsys2018 版的工具了;6. 希望你可以把這個(gè)分享給想學(xué)數(shù)字 IC 的同學(xué);關(guān)于《Synopsys2018EDA 工具》就介紹到這里!!!你唯一需要保障的只是

2020-11-30 18:56:05

對(duì)許多論壇用戶(hù)有用。1.軟件:ISE WEBPack是否足以設(shè)計(jì)一個(gè)中等復(fù)雜度的圖像處理器(中等復(fù)雜度聽(tīng)起來(lái)很模糊,所以請(qǐng)根據(jù)您的經(jīng)驗(yàn)評(píng)估它,我評(píng)價(jià)為邊緣檢測(cè),圓檢測(cè)),或者我需要與Vivado一起

2019-03-21 15:04:42

這篇文檔展示了幾個(gè)機(jī)構(gòu)關(guān)于JEM軟件復(fù)雜度的增加情況的看法,特別提出來(lái)創(chuàng)立一個(gè)新的Ad-hoc組,研究降低軟件一般性復(fù)雜度的可能方法。

2019-07-19 08:25:10

工作的復(fù)雜度和工作量,即使他已經(jīng)經(jīng)過(guò)移植。作為我的數(shù)據(jù)集的一部分,我收集了kicad項(xiàng)目。我希望收集社會(huì)人士的意見(jiàn),以支持我的評(píng)估。我很感謝你的幫助和回應(yīng)!基于掃描工具,移植的復(fù)雜性被確定為困難,項(xiàng)目

2023-09-11 17:06:03

的評(píng)估。我很感謝你的幫助和回應(yīng)!基于掃描工具,移植的復(fù)雜性被確定為苦難,項(xiàng)目中的CPU架構(gòu)相關(guān)的代碼量較多。這將需要一個(gè)專(zhuān)業(yè)的開(kāi)發(fā)者或團(tuán)隊(duì),來(lái)處理這個(gè)任務(wù)(指的是從使項(xiàng)目適應(yīng)特定架構(gòu)到在該架構(gòu)上實(shí)現(xiàn)全部功能的總體工作量)。這樣的評(píng)價(jià)準(zhǔn)確嗎?我期待著你的幫助和回應(yīng)。

2023-09-11 17:03:23

摘 要 針對(duì)跳頻信號(hào)分選提出了采用“復(fù)合信息熵”定量評(píng)估電磁環(huán)境復(fù)雜度的方法。“復(fù)合信息熵”分三個(gè)部分:類(lèi)型熵、密度熵、分布熵,綜合考慮了電磁環(huán)境中包含的信號(hào)類(lèi)型數(shù)、跳頻跳速、跳頻電臺(tái)數(shù)目和信道

2011-07-11 22:35:06

微波系統(tǒng)的設(shè)計(jì)越來(lái)越復(fù)雜,對(duì)電路的指標(biāo)要求越來(lái)越高,電路的功能越來(lái)越多,電路的尺寸要求越做越小,而設(shè)計(jì)周期卻越來(lái)越短。傳統(tǒng)的設(shè)計(jì)方法已經(jīng)不能滿(mǎn)足系統(tǒng)設(shè)計(jì)的需要,使用微波EDA軟件工具進(jìn)行微波元器件

2019-07-30 07:27:53

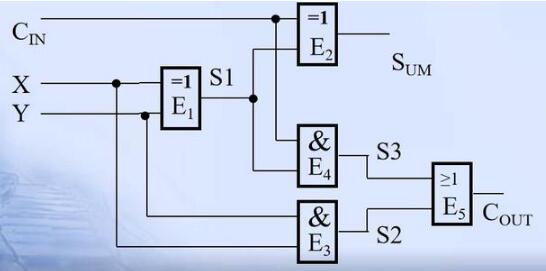

1)EDA的選擇做了張腦圖,大家先看下芯片的大致流程:當(dāng)然實(shí)際設(shè)計(jì)中會(huì)更為復(fù)雜,并隨著制程的變小,會(huì)進(jìn)一步加劇流程各環(huán)節(jié)的復(fù)雜度以及增加環(huán)節(jié)內(nèi)部的新的驗(yàn)證項(xiàng)目,但大體還是以下步驟:前端設(shè)計(jì)和仿真

2020-06-14 08:01:07

微波系統(tǒng)的設(shè)計(jì)約來(lái)越復(fù)雜,對(duì)電路的指標(biāo)要求越來(lái)越高,電路的功能越來(lái)越多,電路的尺寸要求越做越小,而設(shè)計(jì)周期卻越來(lái)越短。傳統(tǒng)的設(shè)計(jì)方法已經(jīng)不能滿(mǎn)足微波電路設(shè)計(jì)的需要,使用微波EDA 軟件工具進(jìn)行微波

2019-06-26 07:17:10

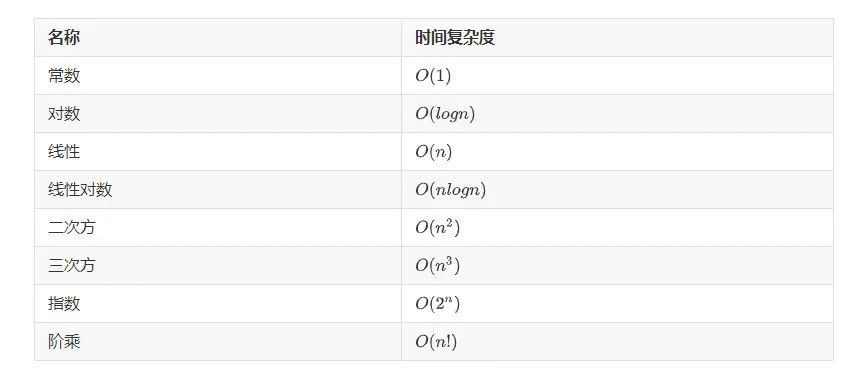

為數(shù)據(jù)個(gè)數(shù),M為數(shù)據(jù)位數(shù)。三、 輔助記憶1、時(shí)間復(fù)雜度記憶冒泡、選擇、直接 排序需要兩個(gè)for循環(huán),每次只關(guān)注一個(gè)元素,平均時(shí)間復(fù)雜度為O(n * n)O(n * n...

2021-12-21 07:48:25

【正文快照】:0引言幀內(nèi)編碼利用相鄰像素塊之間的相關(guān)[1]來(lái)減少視頻圖像的空間冗余度,提高了編碼效率。但是在H.264/AVC的幀內(nèi)預(yù)測(cè)采用全搜索算法中,為了確定一個(gè)宏塊的最優(yōu)預(yù)測(cè)模式,要遍歷色度塊和亮度塊的17種預(yù)測(cè)模式,計(jì)算率失真代價(jià)值的并比較大小,是造成H.264運(yùn)算復(fù)雜度大的主要原因,全文下載

2010-05-06 09:01:59

多種EDA工具的FPGA設(shè)計(jì)方案

2012-08-17 10:36:17

本軟件是多種EDA軟件的鼠標(biāo)增強(qiáng)工具,綠色單文件,支持Win9x/NT/2000/XP/WIN7,其中WIN7需要以管理員模式運(yùn)行,另外,Win9x需要編譯成非UNICODE版本,支持

2018-03-27 19:28:26

基于線(xiàn)性預(yù)測(cè)的FIR自適應(yīng)語(yǔ)音濾波器的系統(tǒng)結(jié)構(gòu)由那幾部分組成?如何降低LMS算法的計(jì)算復(fù)雜度,加快程序在DSP上運(yùn)行的速度,實(shí)現(xiàn)DSP?

2021-04-12 06:27:49

影響; 7.3讓布線(xiàn)工具對(duì)那些默認(rèn)的網(wǎng)絡(luò)根據(jù)需要進(jìn)行處理; 7.4信號(hào)越不重要,自動(dòng)布線(xiàn)工具對(duì)其布線(xiàn)的自由度就越大。 8、布線(xiàn)的整理 如果你所使用的EDA工具軟件能夠列出信號(hào)的布線(xiàn)長(zhǎng)度,檢查這些數(shù)據(jù),你

2017-04-21 14:29:54

現(xiàn)如今,隨著移動(dòng)互聯(lián)網(wǎng)科技的飛速發(fā)展,目前嵌入式開(kāi)發(fā)的復(fù)雜度越來(lái)越大,對(duì)于設(shè)計(jì)工程師在定義和分析系統(tǒng)初始要求時(shí)必須認(rèn)真考慮軟硬件的協(xié)同關(guān)系,所有傳統(tǒng)設(shè)計(jì)考慮的復(fù)雜度也被推上了一個(gè)更高的層次。本文

2017-06-27 09:30:28

現(xiàn)如今,隨著移動(dòng)互聯(lián)網(wǎng)科技的飛速發(fā)展,目前嵌入式開(kāi)發(fā)的復(fù)雜度越來(lái)越大,對(duì)于設(shè)計(jì)工程師在定義和分析系統(tǒng)初始要求時(shí)必須認(rèn)真考慮軟硬件的協(xié)同關(guān)系,所有傳統(tǒng)設(shè)計(jì)考慮的復(fù)雜度也被推上了一個(gè)更高的層次。本文

2017-06-29 16:03:52

現(xiàn)如今,隨著移動(dòng)互聯(lián)網(wǎng)科技的飛速發(fā)展,目前嵌入式開(kāi)發(fā)的復(fù)雜度越來(lái)越大,對(duì)于設(shè)計(jì)工程師在定義和分析系統(tǒng)初始要求時(shí)必須認(rèn)真考慮軟硬件的協(xié)同關(guān)系,所有傳統(tǒng)設(shè)計(jì)考慮的復(fù)雜度也被推上了一個(gè)更高的層次。本文

2017-07-05 09:59:28

常用EDA工具軟件有哪些?探討數(shù)字電子技術(shù)與EDA技術(shù)是如何相結(jié)合的?有什么益處?

2021-04-07 06:26:04

1.引言微波系統(tǒng)的設(shè)計(jì)越來(lái)越復(fù)雜,對(duì)電路的指標(biāo)要求越來(lái)越高,電路的功能越來(lái)越多,電路的尺寸要求越做越小,而設(shè)計(jì)周期卻越來(lái)越短。傳統(tǒng)的設(shè)計(jì)方法已經(jīng)不能滿(mǎn)足系統(tǒng)設(shè)計(jì)的需要,使用微波EDA軟件工具進(jìn)行微波

2019-06-27 07:06:05

微波系統(tǒng)的設(shè)計(jì)越來(lái)越復(fù)雜,對(duì)電路的指標(biāo)要求越來(lái)越高,電路的功能越來(lái)越多,電路的尺寸要求越做越小,而設(shè)計(jì)周期卻越來(lái)越短。傳統(tǒng)的設(shè)計(jì)方法已經(jīng)不能滿(mǎn)足系統(tǒng)設(shè)計(jì)的需要,使用微波EDA軟件工具進(jìn)行微波元器件

2019-06-19 07:13:37

及時(shí)糾錯(cuò)。”呂茂田說(shuō),“不過(guò),隨著芯片復(fù)雜度的提高,糾錯(cuò)的難度在加大。而且糾錯(cuò)只是令設(shè)計(jì)意圖實(shí)現(xiàn),并不能令芯片變得更強(qiáng)大,因此如何盡量減少糾錯(cuò)時(shí)間就變得越來(lái)越重要,而這就需要糾錯(cuò)工具的有力支持

2020-07-07 09:02:05

設(shè)計(jì)相融合的設(shè)計(jì)工具,同時(shí)具備Verilog編譯仿真和波形分析。同時(shí)可以實(shí)現(xiàn)各種系統(tǒng)的設(shè)計(jì),仿真和測(cè)試。軟件生成標(biāo)準(zhǔn)的Verilog代碼,可以直接與各種EDA工具相融合。

2012-11-21 15:24:06

原理->微機(jī)原理->軟件工程,編譯原理,數(shù)據(jù)庫(kù)數(shù)據(jù)結(jié)構(gòu)1.時(shí)間復(fù)雜度時(shí)間復(fù)雜度是指執(zhí)行算法所需要的計(jì)算工作量,因?yàn)檎麄€(gè)算法的執(zhí)行時(shí)間與基本操作重復(fù)執(zhí)行的...

2021-07-22 10:01:13

小弟從未畫(huà)過(guò)4層及以上的板,不知哪位大神能傳份復(fù)雜度一般的工程給小弟參考參考。感激不盡!我的郵箱87906234@qq.com。在此謝過(guò)

2019-07-09 00:36:27

本文參考IEEE 802.16d物理層幀結(jié)構(gòu),提出了一種低復(fù)雜度的幀同步和定時(shí)同步聯(lián)合算法,該算法可在FPGA上利用較少資源來(lái)實(shí)現(xiàn)。

2021-05-06 06:23:10

版的

EDA工具介紹。 FPGA設(shè)計(jì) 基本設(shè)計(jì)

工具,QUARTUS, ISE, Synplify pro, Modelsim. 主流FPGA器件主要是兩家,Altera和Xilinx。所以?xún)杉?/div>

2012-12-28 17:00:22

與特定微控制器硬件的完整映射。要應(yīng)對(duì)與日俱增的設(shè)計(jì)復(fù)雜度,僅有功能強(qiáng)大的編譯器、調(diào)試器以及IP庫(kù)和自動(dòng)代碼生成器是不夠的,還需要適當(dāng)?shù)膮⒖荚O(shè)計(jì),例如,英飛凌面向電機(jī)控制的應(yīng)用套件,或面向連接的IO鏈路

2018-12-03 14:00:22

設(shè)計(jì)原理圖的效率,加速完善國(guó)產(chǎn)EDA布局,面向電子系統(tǒng)/產(chǎn)品研發(fā)全流程,提供更高效、更智能的EDA軟件及數(shù)據(jù)服務(wù)。

2022-04-11 13:47:20

基于可靠性更新的低復(fù)雜度B譯碼算法:基于部分符號(hào)更新策略的BP (Belief Propagation)譯碼算法減少了LDPC (Low-Density Parity-Check)碼的譯碼運(yùn)算量,提高了譯碼效率。然而在其譯碼過(guò)程中,由

2009-10-29 13:09:21 16

16 該文提出一種適用于NLOS 環(huán)境UWB 多徑信道下低復(fù)雜度的選擇性RAKE 接收機(jī)(RC-SRAKE),通過(guò)本地參考波形與接收信號(hào)的卷積抽樣來(lái)確定SRAKE 的Finger 參數(shù),不需要已知信道信息或信道估計(jì)

2009-11-19 16:51:28 9

9 MIMO 系統(tǒng)中,球形譯碼可以在保證接近ML 檢測(cè)性能的前提下大大降低檢測(cè)復(fù)雜度。但當(dāng)信道矩陣條件數(shù)很高時(shí),球形譯碼的復(fù)雜度仍然會(huì)很高。在分析了這一現(xiàn)象的原因后,本文提出

2009-11-21 13:52:07 8

8 該文通過(guò)降低采樣大小和信號(hào)檢測(cè)搜索空間給出了兩種低復(fù)雜度的多輸入多輸出(MIMO)系統(tǒng)粒子濾波(PF)檢測(cè)方法:球形約束PF 和多層映射PF。在球形約束PF 中,首先基于迫零原則求得

2009-11-25 15:19:22 15

15 線(xiàn)性復(fù)雜度是衡量密鑰流序列安全性的重要參數(shù)。該文考察了有限域上n 級(jí)本原σ - LFSR序列的線(xiàn)性復(fù)雜度性質(zhì)。首先得到了它的上下界并證明了界是緊致的,然后利用序列的根表示給

2010-02-10 11:02:53 8

8 本文分析了現(xiàn)有的基于導(dǎo)頻的MIMO-OFDM信道估計(jì)技術(shù),提出了一種低復(fù)雜度的信道估計(jì)閾值算法,這種算法與采用維納濾波器的估計(jì)技術(shù)相比較,具有計(jì)算復(fù)雜度低,適應(yīng)性好的特點(diǎn)

2010-02-21 11:51:48 21

21 EDA工具手冊(cè).

Cadence 軟件是我們公司統(tǒng)一使用的原理圖設(shè)計(jì)、PCB 設(shè)計(jì)、高速仿真、自動(dòng)布線(xiàn)的EDA 工具。本篇Cadence 使用手冊(cè)是一本基于Allegro SPB V15.2 版本的Cadence 軟件的基

2010-03-11 15:11:46 0

0 基于多種EDA工具的FPGA設(shè)計(jì)

介紹了利用多種EDA工具進(jìn)行FPGA設(shè)計(jì)的實(shí)現(xiàn)原理及方法,其中包括設(shè)計(jì)輸入、綜合、功能仿真、實(shí)現(xiàn)、時(shí)序仿真、配置下載等具體內(nèi)容。并以實(shí)

2009-05-14 18:38:38 854

854

摘 要:在FPGA開(kāi)發(fā)的各個(gè)階段,市場(chǎng)為我們提供了很多優(yōu)秀的EDA工具。面對(duì)眼花繚亂的EDA工具,如何充分利用各種工具的特點(diǎn),并規(guī)劃好各種工具的協(xié)同使用,對(duì)FPGA

2009-06-20 10:51:14 692

692 多種EDA工具的FPGA設(shè)計(jì)方案

概述:介紹了利用多種EDA工具進(jìn)行FPGA設(shè)計(jì)的實(shí)現(xiàn)原理及方法,其中包括設(shè)計(jì)輸入、綜合、功能仿真、實(shí)現(xiàn)、時(shí)序仿真、配

2010-05-25 17:56:59 670

670

在描述置信傳播(BP)譯碼算法基礎(chǔ)上, 研究和分析了兩種降低復(fù)雜度的譯碼算法。Min.Sum 算法主要討論了簡(jiǎn)化校驗(yàn)節(jié)點(diǎn)的消息更新運(yùn)算,并應(yīng)用密度進(jìn)化方法對(duì)此算法進(jìn)行極限性能分析

2012-03-31 15:22:03 7

7 EDA設(shè)計(jì)流程及其工具

2016-12-11 23:38:39 0

0 基于RNS的低復(fù)雜度DDS的設(shè)計(jì)與實(shí)現(xiàn)_張鳳君

2017-01-08 10:11:41 0

0 針對(duì)信息隱藏中載體圖像的差異性,提出一種圖像復(fù)雜度評(píng)價(jià)方法,綜合考慮圖像的壓縮特性以及圖像紋理能量作為圖像復(fù)雜度指標(biāo),并基于閾值劃分準(zhǔn)則對(duì)栽體圖像進(jìn)行復(fù)雜度分類(lèi),以幾種經(jīng)典的基于直方圖的幾種無(wú)損隱藏

2017-11-14 09:57:47 5

5 足錯(cuò)線(xiàn)性復(fù)雜度是度量序列密碼安全性的重要指標(biāo)之一。基于方體理論和Games-Chan算法的逆向推導(dǎo)提出構(gòu)造方法,構(gòu)造了具有給定足錯(cuò)線(xiàn)性復(fù)雜度譜的2周期序列。首先使用標(biāo)準(zhǔn)方體分解算法對(duì)忌錯(cuò)線(xiàn)性復(fù)雜度

2017-11-23 17:17:00 0

0 本文提出了一個(gè)集成了OTN/WDM且低復(fù)雜度的交換架構(gòu)。首先將OTN與WDM集成在一個(gè)交換架構(gòu)中,通過(guò)減少其中的OTN交換器數(shù)量以降低該架構(gòu)的復(fù)雜度。為緩解因減少交換器數(shù)量導(dǎo)致的擁塞上升,需合理配置

2017-12-05 18:39:06 0

0 復(fù)雜度。結(jié)果表明該序列有較好的線(xiàn)性復(fù)雜度。 本篇文章,我們構(gòu)造了一類(lèi)廣義三元分圓序列,計(jì)算出該序列的自相關(guān)值和線(xiàn)性復(fù)雜度。結(jié)果表明這類(lèi)序列有較高的線(xiàn)性復(fù)雜度。類(lèi)似于定理5和定理10的計(jì)算過(guò)程,我們可以計(jì)算當(dāng)廠為奇數(shù)時(shí)該序

2017-12-18 16:45:41 0

0 移動(dòng)通信設(shè)備由于計(jì)算資源有限,對(duì)計(jì)算復(fù)雜度較為敏感。我國(guó)自主研發(fā)提出的移動(dòng)音頻編解碼算法標(biāo)準(zhǔn)AVS PlO中的帶寬擴(kuò)展算法有利于提高移動(dòng)音頻編解碼質(zhì)量,但其計(jì)算復(fù)雜度較高,不利于該編解碼算法在移動(dòng)

2017-12-25 11:32:20 1

1 就是設(shè)計(jì)出計(jì)算復(fù)雜度低并且檢測(cè)性能好的信號(hào)檢測(cè)算法。在MIMO系統(tǒng)中,最佳檢測(cè)方案是極大似然檢測(cè)( Maximum Likelihood Detector,MLD)方案。但是,隨著天線(xiàn)數(shù)量的增加,最大似然檢測(cè)

2018-01-29 10:46:39 0

0 針對(duì)不同的視頻內(nèi)容造成編碼前幾幀質(zhì)量低下的問(wèn)題,提出一種基于I幀復(fù)雜度的初始量化參數(shù)( QP)選擇算法。在編碼前利用解碼碼流中得到的I幀宏塊模式信息,運(yùn)用宏塊中的3種不同幀內(nèi)預(yù)測(cè)模式判斷I幀的復(fù)雜度

2018-02-07 14:06:58 0

0 本文首先介紹了EDA工具廠商,其次對(duì)八種硬件設(shè)計(jì)的EDA工具做了對(duì)比分析,最后闡述了eda的應(yīng)用。

2018-04-19 11:28:29 18879

18879 EDA公司以賣(mài)EDA工具license費(fèi)作為主要的商業(yè)模式。以某家EDA公司的PnR工具為例,一套license三年的使用費(fèi)大約為100萬(wàn)美金左右。對(duì)于芯片設(shè)計(jì)公司來(lái)說(shuō),一般需要購(gòu)買(mǎi)多套license才能滿(mǎn)足芯片設(shè)計(jì)需求。

2018-04-26 15:23:10 39016

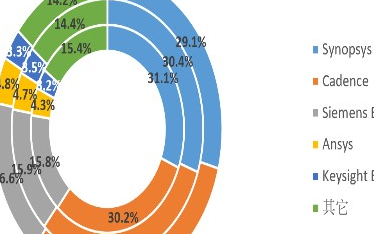

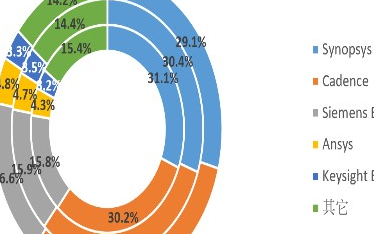

39016 EDA是IC電子行業(yè)必備的設(shè)計(jì)工具軟件,是IC產(chǎn)業(yè)鏈最上游的子行業(yè)。Cadence、Synopsys、Mentor Graphics是EDA工具軟件廠商全球三大巨頭。去年11月份,Mentor Graphics被西門(mén)子以45億美元現(xiàn)金方式的收購(gòu)。

2018-05-08 14:36:00 26673

26673 芯片設(shè)計(jì)環(huán)節(jié)繁多、精細(xì)且復(fù)雜,EDA工具在其中承載了極為重要作用。

2020-05-15 11:40:46 767

767 通常專(zhuān)業(yè)的EDA工具供應(yīng)商或各可編程邏輯器件廠商都提供EDA開(kāi)發(fā)工具,在這些EDA開(kāi)發(fā)工具中都含有設(shè)計(jì)輸入編輯器,如Xilinx公司的Foundation、Altera公司的MAX+plusII和QuartusII等。

2020-05-15 14:45:15 8258

8258

目前國(guó)內(nèi)電子工程師使用的EDA設(shè)計(jì)工具主要還是以國(guó)外的設(shè)計(jì)工具為主,顯然,國(guó)內(nèi)EDA市場(chǎng)已被高度壟斷。其實(shí)早在2014年開(kāi)始,國(guó)內(nèi)就已經(jīng)誕生了一款專(zhuān)為國(guó)人的使用習(xí)慣研發(fā)的EDA工具——EasyEDA。

2020-07-09 15:47:36 3165

3165 采用隨機(jī)插入策略的垃圾代碼控制流混淆算法,存在混淆強(qiáng)度和額外開(kāi)銷(xiāo)的不確定性。針對(duì)該問(wèn)題,提出一種基于嵌套復(fù)雜度的控制流混淆算法OB_NC,對(duì)混淆所引入的開(kāi)銷(xiāo)進(jìn)行定量計(jì)算,采用嵌套復(fù)雜度對(duì)控制流復(fù)雜度

2020-11-20 17:14:34 13

13 交叉口的復(fù)雜程度嚴(yán)重影響著交叉口功能區(qū)的交通安全和通行效率,空間布局和運(yùn)行組織過(guò)于簡(jiǎn)單則缺乏功能穩(wěn)定性,過(guò)于復(fù)雜則導(dǎo)致交叉口功能穩(wěn)定性降低;故深入研究交叉口復(fù)雜度對(duì)于改善交又口運(yùn)行狀態(tài),提升

2021-04-30 14:36:46 1

1 經(jīng)過(guò)30余年的行業(yè)整合發(fā)展,全球EDA工具市場(chǎng)體現(xiàn)出較明顯的寡頭壟斷特征,新思科技(Synopsys)、楷登電子(Cadence)與西門(mén)子EDA(原Mentor Graphics)作為目前僅有的擁有

2021-06-12 10:32:00 3859

3859

面向大容量毫米波通信的低復(fù)雜度幀同步

2021-07-01 14:39:00 8

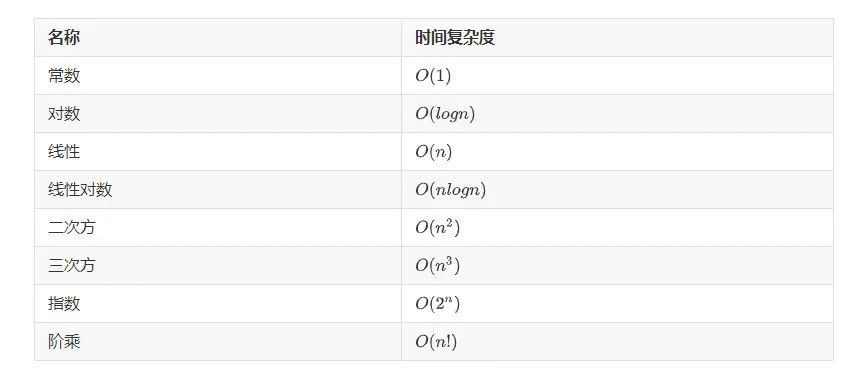

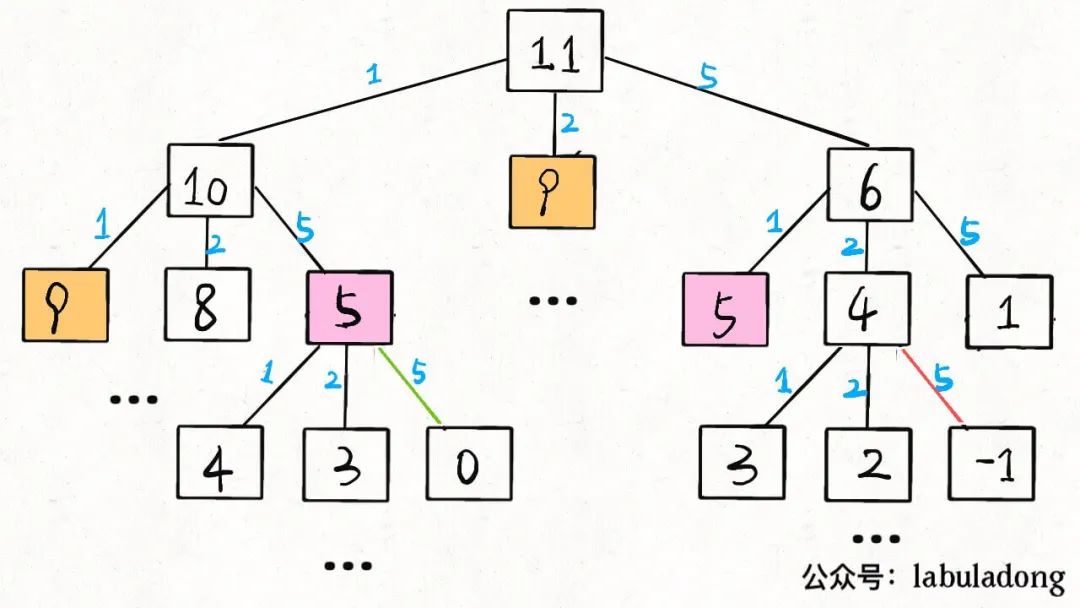

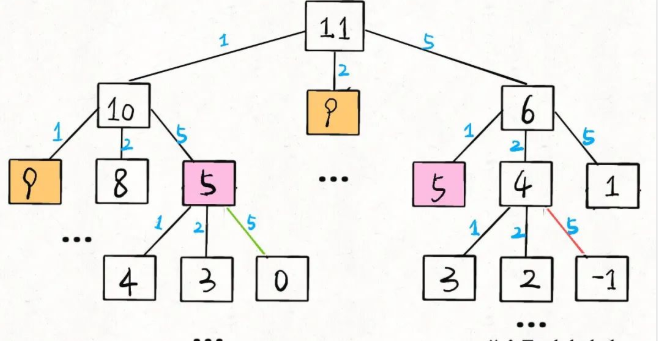

8 相信每一位錄友都接觸過(guò)時(shí)間復(fù)雜度,但又對(duì)時(shí)間復(fù)雜度的認(rèn)識(shí)處于一種朦朧的狀態(tài),所以是時(shí)候?qū)r(shí)間復(fù)雜度來(lái)一個(gè)深度的剖析了。

2022-03-18 10:18:51 1532

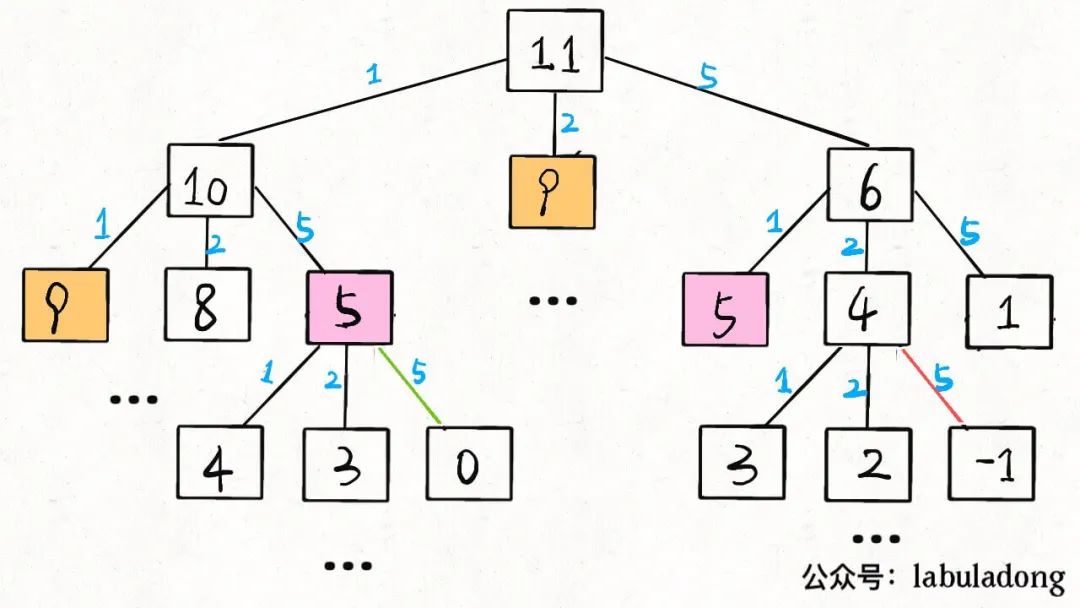

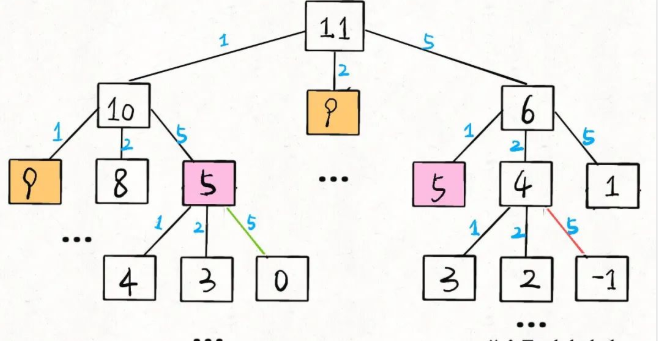

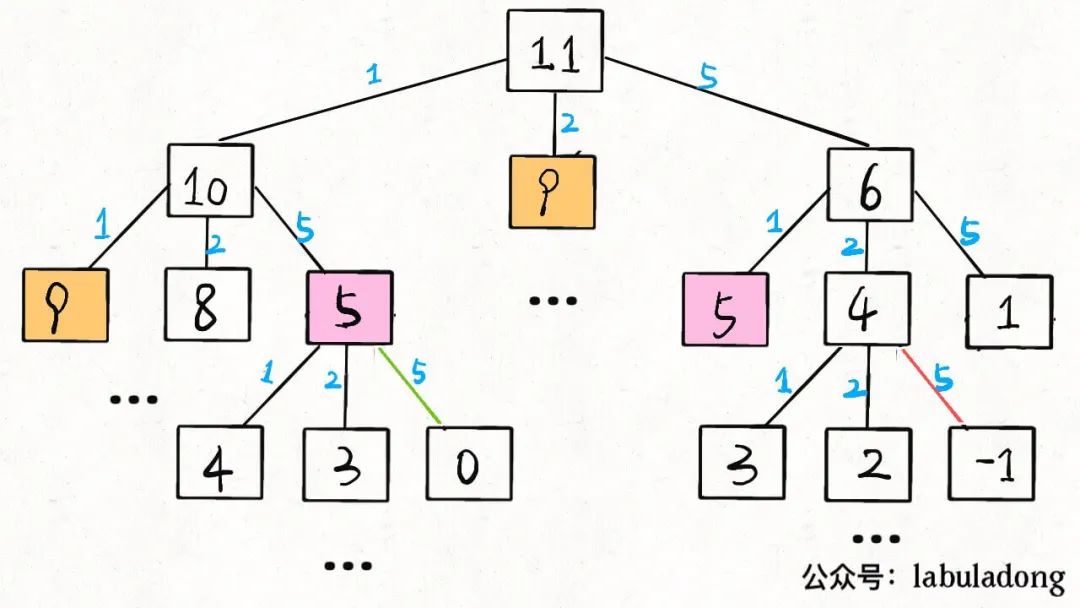

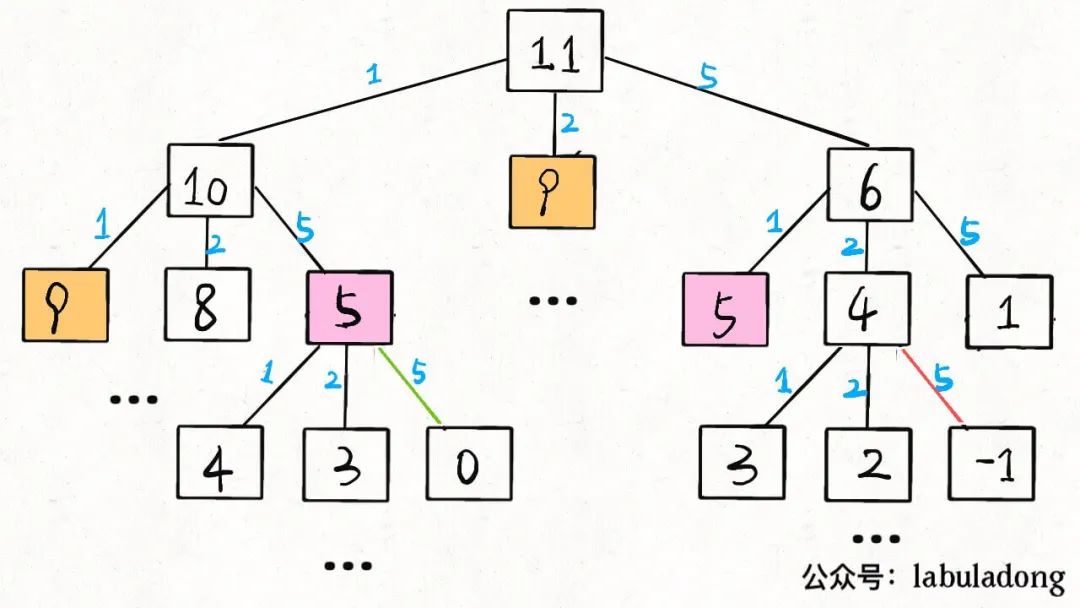

1532 那么我通過(guò)一道簡(jiǎn)單的面試題,模擬面試的場(chǎng)景,來(lái)帶大家逐步分析遞歸算法的時(shí)間復(fù)雜度,最后找出最優(yōu)解,來(lái)看看同樣是遞歸,怎么就寫(xiě)成了O(n)的代碼。

2022-07-13 11:30:49 1928

1928 相信很多同學(xué)對(duì)遞歸算法的時(shí)間復(fù)雜度都很模糊,那么這篇Carl來(lái)給大家通透的講一講。

2022-07-13 11:33:02 1309

1309 算法之空間復(fù)雜度:衡量一個(gè)算法運(yùn)行需要開(kāi)辟的額外空間

2022-08-31 10:29:40 1258

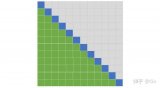

1258 時(shí)間復(fù)雜度不是測(cè)量一個(gè)算法或一段代碼在某個(gè)機(jī)器或者條件下運(yùn)行所花費(fèi)的時(shí)間。時(shí)間復(fù)雜度一般指時(shí)間復(fù)雜性,時(shí)間復(fù)雜度是一個(gè)函數(shù),它定性描述該算法的運(yùn)行時(shí)間,允許我們?cè)诓贿\(yùn)行它們的情況下比較不同的算法。

2022-10-02 12:45:00 635

635 及特色,演示產(chǎn)品的使用。 英諾達(dá)首款EDA工具發(fā)布時(shí)間:2022年11月2日 10:30?? 發(fā)布會(huì)簡(jiǎn)介? 隨著人工智能、5G、大數(shù)據(jù)中心、汽車(chē)等應(yīng)用帶來(lái)的IC功能和復(fù)雜度爆炸性增長(zhǎng),功耗帶來(lái)的問(wèn)題日益突顯。多電壓、多電源、動(dòng)態(tài)電源電壓控制等低功耗設(shè)計(jì)已是IC設(shè)計(jì)中采用的主流技術(shù)。低功耗設(shè)

2022-10-31 10:50:16 452

452 我以前的文章主要都是講解算法的原理和解題的思維,對(duì)時(shí)間復(fù)雜度和空間復(fù)雜度的分析經(jīng)常一筆帶過(guò),主要是基于以下兩個(gè)原因:

2023-04-12 14:37:29 323

323

類(lèi)似的,想想之前說(shuō)的數(shù)據(jù)結(jié)構(gòu)擴(kuò)容的場(chǎng)景,也許`N`次操作中的某一次操作恰好觸發(fā)了擴(kuò)容,導(dǎo)致時(shí)間復(fù)雜度提高,但總的時(shí)間復(fù)雜度依然保持在`O(N)`,所以均攤到每一次操作上,其平均時(shí)間復(fù)雜度依然是`O(1)`。

2023-04-12 14:38:04 328

328

本文會(huì)篇幅較長(zhǎng),會(huì)涵蓋如下幾點(diǎn):

1、Big O 表示法的幾個(gè)基本特點(diǎn)。

2、非遞歸算法中的時(shí)間復(fù)雜度分析。

3、數(shù)據(jù)結(jié)構(gòu) API 的效率衡量方法(攤還分析)。

4、遞歸算法的時(shí)間/空間復(fù)雜度的分析方法,這部分是重點(diǎn),我會(huì)用動(dòng)態(tài)規(guī)劃和回溯算法舉例。

2023-04-19 10:34:55 495

495

Big O 表示法的幾個(gè)基本特點(diǎn)。

2、非遞歸算法中的時(shí)間復(fù)雜度分析。

3、數(shù)據(jù)結(jié)構(gòu) API 的效率衡量方法(攤還分析)。

4、遞歸算法的時(shí)間/空間復(fù)雜度的分析方法,這部分是重點(diǎn),我會(huì)用動(dòng)態(tài)規(guī)劃和回溯算法舉例。

2023-04-19 10:35:38 406

406

EDA工具的技術(shù)來(lái)源主要包括描述統(tǒng)計(jì)學(xué)、可視化技術(shù)、探索性數(shù)據(jù)分析方法、數(shù)據(jù)挖掘技術(shù),以及可交互性與用戶(hù)界面設(shè)計(jì)。這些技術(shù)和方法的應(yīng)用使得EDA工具成為數(shù)據(jù)分析和發(fā)現(xiàn)中不可或缺的工具之一。

2023-07-21 15:09:44 535

535 1 算法與時(shí)間復(fù)雜度 算法(Algorithm)是求解一個(gè)問(wèn)題需要遵循的,被清楚指定的簡(jiǎn)單指令的集合。 算法一旦確定,那么下一步就要確定該算法將需要多少時(shí)間和空間等資源,如果一個(gè)算法需要一兩年的時(shí)間

2023-10-13 11:19:32 901

901

中興EDA工具手冊(cè)

2022-12-30 09:21:00 8

8 電子發(fā)燒友網(wǎng)站提供《如何降低SigmaDSP音頻系統(tǒng)復(fù)雜度的情形.pdf》資料免費(fèi)下載

2023-11-29 11:13:29 0

0 首先來(lái)詳細(xì)說(shuō)明為什么Transformer的計(jì)算復(fù)雜度是 。將Transformer中標(biāo)準(zhǔn)的Attention稱(chēng)為Softmax Attention。令 為長(zhǎng)度為 的序列, 其維度為 , 。 可看作Softmax Attention的輸入。

2023-12-04 15:31:22 343

343

機(jī)遇總是與挑戰(zhàn)并存,目前國(guó)內(nèi)在高端EDA工具研發(fā)方面,面臨著如Synopsys、Cadence和Mentor等國(guó)際EDA供應(yīng)商的巨大挑戰(zhàn),即使是作為本土最大的EDA公司,華大九天目前也只能夠提供產(chǎn)業(yè)所需EDA解決方案的1/3左右。

2024-01-18 15:19:13 311

311

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論