度、精度和易用性都是設計者使用仿真時的關鍵需求,他們要用仿真將自己的模擬、RF和混合信號設備推向市場。廣受尊重的Spice仿真器仍是模擬仿真工具的選擇,而EDA供應商正在通過創新技術改進自己工具的速度與精度,如使它們適合于多核處理器或多CPU系統的運行。其它公

模擬與RF仿真工具提供各種仿真速度的選擇,并支持分層的設計策略。

要點

??在將設計交付硬件實現以前,應采用能夠使用矩量法和有限元分析技術的EM(電磁)域工具,解決鄰近效應和轉換效應問題。

??快速Spice工具偏向于用精度換取速度,但制造商經常聲稱這些工具有“Spice級精度”。

??傳統的Spice仿真器在十萬個元件時就無能為力了,哪怕采用并行處理也不能提高容量。

??隨著消費產品的制造商們努力以更低成本提供更高的功能密度,他們要在小體積內塞進數字、模擬和RF功能,這就產生了芯片、封裝和電路板的協同設計與仿真需求。

速度、精度和易用性都是設計者使用仿真時的關鍵需求,他們要用仿真將自己的模擬、RF和混合信號設備推向市場。廣受尊重的Spice仿真器仍是模擬仿真工具的選擇,而EDA供應商正在通過創新技術改進自己工具的速度與精度,如使它們適合于多核處理器或多CPU系統的運行。其它公司則正在重新編寫Spice算法,以加快仿真速度。當然也有一些公司關注自頂向下的設計。

但當設計者為越來越多的產品增加RF/無線通信功能時,Spice只是仿真場景中的一部分。隨著工藝尺度的縮小、數字電路速度的增加以及高速串行I/O端口的增多,不提供RF/無線功能的產品也正在具備RF性能。此外,在很多情況下,隨著頻率的上升以及設計者在越來越小的空間中塞入更多功能,芯片與電路板的設計也不能獨善其身;必須對芯片、芯片封裝和電路板采取協同設計和仿真。

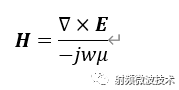

How-Siang Yap是Agilent技術公司EEsof部EDA產品營銷組成員,他概述了可以成為一種有效的協同仿真方案的跨域仿真技術(cross-domain-simulation)。首先他表示,需要數值域工具,如The MathWorks公司的Matlab,或Agilent公司的Ptolomy,以及C++、System-C和標準的HDL(硬件描述語言)。另外還需要頻域的交流仿真工具,它可以用S參數并實現諧波平衡技術。Yap補充說,對于時域,需要Spice工具。他的建議是,在設計轉為硬件以前,應采用EM(電磁)域工具,它可以使用矩量法(method-of-moment)和有限元分析技術,查找鄰近效應和轉換效應的錯誤。

?

Spice提速

對于Spice,關注的焦點是在提高速度的同時不喪失精度。為解決這個問題,Cadence設計系統公司近期宣布推出了Cadence Virtuoso APS(加速的并行仿真器),這是它的下一代電路仿真器,是Cadence MMSIM(多模式仿真)7.1版的組成部分。Cadence高級架構師John Pierce稱,新仿真器將混合信號仿真的周轉時間從數天或數周減少到只有數小時。Cadence的一名高級產品經理Nebabie Kebebew表示,新仿真器大大提升了單線程和可縮放多線程的性能,并且保持了與Cadence Virtuoso Spectre電路仿真器相當的精度。Kebebew說有20多個測試客戶已在200多個設計上對新仿真器作了測試,其中涉及的器件包括PLL(鎖相環)、DAC、ADC、存儲器、電源管理電路和高速I/O電路。她說,一個客戶在一個八核系統上作65 nm PLL設計仿真時,性能提高至原來的60倍。她補充說,另一個客戶在做一個DC/DC轉換器的版圖后仿真時,性能提高至58倍,運行時間從20小時16分減少到21分鐘。

?

Mentor Graphics公司也一直致力于提高仿真速度。該公司在2008年10月推出了新版的Eldo與Eldo RF晶體管級模擬仿真器,在不影響精度的情況下,提高了原始的速度性能。新版采用一種經修改的矩陣解算策略以及一種可縮放的多線程技術,使用戶能夠充分利用廉價的多CPU硬件。

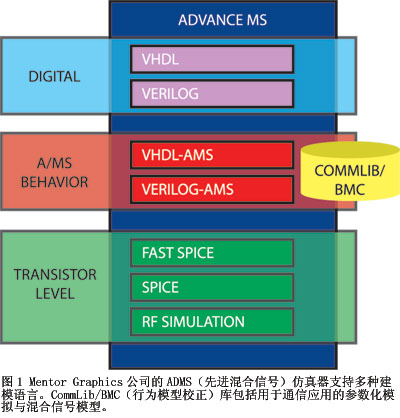

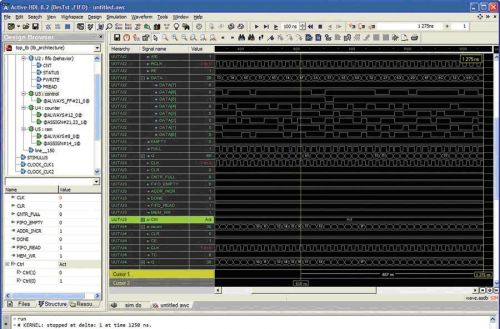

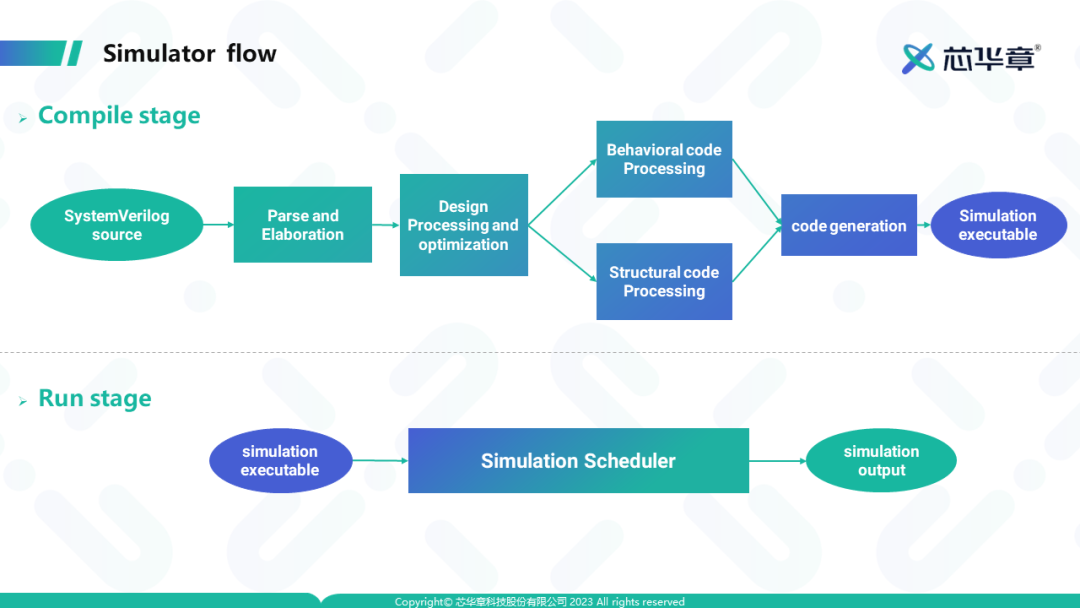

Mentor公司深亞微米業務發展經理Tony Liao指出,多線程的Eldo運行速度為單核版的3倍~10倍以上,具體取決于電路中的有源器件數和寄生成分數量。他說,要得到更快的仿真,客戶可以使用ADiT快速Spice仿真器,不過要付出一些精度的成本。一個ADiT與Eldo接口可以使電路同時運行兩種仿真器;需要高精度的部分在Eldo上運行,另一部分則在ADiT上運行。Liao指出,這些仿真器可與Mentor的ModelSim數字仿真器鏈接,支持協同仿真。仿真器與Mentor ICAnalyst的鏈接能幫助支持設計驗證。另外,兩種仿真器都可以協同工作在Mentor公司的ADMS(先進混合信號)仿真環境中(圖1)。

?

Synopsys也致力于加快Spice速度,并在2008年3月推出HSpice仿真器時,宣布了對其HSpice核心引擎技術的增強以及新的多線程能力。Synopsys混合信號仿真產品營銷總監Geoffrey Ying表示,該公司正使全部工具都能配合多核處理器的優勢,HSpice是第一個遷移的產品。他說,有了多線程版,電路設計者現在運行HSpice版圖后仿真的速度比單核處理器快兩倍,在四核處理器上更可以快達五倍。單核版的提速方式是改進符號的直流工作點收斂算法、瞬態時間步長控制、網表分析,以及模型性能。對于多核處理器,該軟件版能夠仿真包括100萬個以上阻性和容性寄生效應的版圖后設計。

Synopsys已經與TSMC(臺積電制造公司)在TMI(TSMC建模接口)方法上展開合作,包括一個將客戶器件模型與Synopsys HSpice、HSim與NanoSim電路仿真器相整合的協議。TMI方法為TSMC的40 nm及以下尺度工藝技術提供了一個創新而有效的器件建模方案。Ying稱TMI方法平均能將仿真時間和內存使用減至五分之一,并且同時考慮了機械應力對硅片的作用和版圖相關性,后者會根據與其它器件的接近程度,改變器件的特性。

Magma設計自動化公司采用多CPU,而不是多核心和多線程。Magma的定制設計業務部業務發展高級總監KT Moore稱,該公司的FineSim Spice充分利用了Magma的NPT(原生并行技術)將計算負載分配給多臺計算機,增加了速度與容量,并保持了精度。他說,通過該方案“客戶能夠用實際可行數量的計算機做成千上萬個器件的仿真,只用8臺計算機而不是用100臺計算機。”

雖然Spice的多線程和多計算機實現方法都提高了性能,但仍會繼續有對快速Spice實現的需求。Moore說:“在一個設計過程的不同階段,對精度的要求也有變化。在早期,你可以更關注于功能。當你將設計集中于實際工作點和特性時,就希望收緊對精度的要求。很多大型設計都有數百萬只晶體管;你可能會在多只CPU上用我們的Spice引擎作仿真,對一個簽核(sign-off)仿真這種方法可能很好。”但他表示對于回歸仿真或功能仿真,NPT才是你可能希望使用的工具。

傳統的EDA公司都在Spice領域受到了來自相對較新成員的競爭,有時這模糊了真正Spice與快速Spice之間的界限。Berkeley設計自動化公司的首席運營官Paul Estrada說,快速Spice工具傾向于用精度換取速度。不過,制造商經常在“Spice-accurate”(Spice級精度)的幌子下推出這些快速Spice工具。他表示,Berkeley設計自動化公司的Analog Fast Spice是真正能提供快速Spice能力,并有等同于真正Spice精度的性能。Estrada稱,該工具不做近似。反之,它運行的是原始器件方程,解算原始的全電路矩陣,產生的波形相當于甚至優于任何其它Spice引擎。

Analog Fast Spice提高了它在單核處理器上運行的性能,Estrada將其性能水平歸結于其開發人員不需要嘗試優化原有代碼。他說:“深入觀察今天的任何Spice引擎,你會發現,它們的基本結構像一個老鼠窩。每個東西都與其它東西互相交織,如果你試圖改進仿真器的一個方面,那就總會把其它方面搞糟。”Analog Fast Spice采用一種模塊化架構,可以對每個模塊作優化,而不會干擾其它模塊。展望未來,該公司認為多線程有更好的結果,但尚未推出多線程版本。

Gemini公司也采用多線程來提高性能。該公司銷售與營銷副總裁Kent Jaeger稱,公司的目標是95%的Spice精確工具和快速MOS Spice市場。他表示,Gemini的整體多線程Spice可提供兩至十倍的性能提升,而不會累及精度。“我們禁止自己的設計者使用任何有可能犧牲Spice精度的技術。”Gemini仿真器在90%的基準測試中超過了快速MOS Spice仿真器的性能,運行在采用64位 Linux操作系統的低價英特爾多核處理器上。

Infinisim公司從快速Spice借用了一些技術,而仍保持Spice的精度,這是該公司首席技術官Zakir Syed的表述。該公司的RASer(實時自適應仿真)仿真器可用于設計驗證的全部階段,從單個塊到全芯片,以及從版圖前到版圖后。據該公司高級營銷總監Anand Lyer表示,RASer針對做全系統仿真的關鍵需求,避免了硅片的重制(re-spin)要求。他說:“傳統的Spice仿真器在數十萬個元件時就無能為力了,即使采用并行處理,容量也不會增加。”

此時早晚得用類似快速Spice的方案。Syed說:“我們就像快速Spice那樣將一個電路拆成小部分,然后為不同部分使用不同的解算器。在快速Spice中,你會失去精度,但是,我們使用的是Spice采用的精確器件模型。”

雖然Infinisim支持多線程,但該公司主要關注提升每個線程的速度。Syed說:“很多公司正在開發在Spice上的多核算法,并且,這些公司已放棄了對Spice的改進。”他認為,某些情況(如蒙特卡羅仿真)適用于多線程與分布式計算。此時,任何仿真都獨立于其它仿真。

Tanner EDA的產品管理總監Nicolas Williams稱:“在模擬設計中,我們見到的迭代一般要運行五次角落模型和溫度掃描。如果要做蒙特卡羅分析,就必須對一個電路運行數千次仿真,很容易從一個指令臺處理這些仿真運行。”他補充說,這是在仿真工作級,而不是電路級,此時并行可以提供最大的好處。

Tanner的T-Spice仿真器面向大模擬、小數字芯片的設計。該公司集成了Verilog-A,同時支持行為模型和器件級Spice模型的仿真。Verilog-A支持自頂向下的設計,遠優于模擬設計者過去經常采用的自下至上方案。Williams稱自頂向下設計可以消除昂貴而耗時的設計反復,而對自下至上方案,當設計周期后期出現系統集成問題時,這種反復是必不可少的。

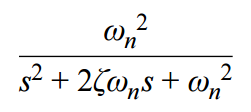

他指出,模擬設計者在使用依賴性資源時會使用行為建模技術,他們可能使用The MathWorks的Matlab來計算系數,但迄今為止,他們在Spice編程環境中還缺乏一種行為語言。Spice與行為模型的組合使設計者能夠專注于塊的設計,并且無需漫長的運行時間而完成仿真。表1給出了仿真一個PLL的相對CPU時間,其元件表示為Spice與Verilog-A模型的各種組合。

超越Spice

即便一個芯片設計經過了徹底的仿真與驗證,也不能保證在真正硅片誕生以后,該器件能正常地工作。硅片性能屈從于芯片封裝的EM效應、封裝所安裝的電路板,或包含電路板的大尺度結構(見附文《EM仿真:從PCB到直升機》)。Ansoft業務開發總監Larry Williams詳述了一個半導體制造商的故事,它的器件裝在一塊評估板上,評估板有良好隔離的走線,并用大量的電源層和地層來隔離信號。然而,當該制造商的客戶將器件裝在一個微型消費產品中時,走線靠得非常近,造成了更多的耦合,它的性能表現不正常。突然間,芯片的射頻開始出現異常,產生不可接受的帶外偽響應。Williams說:“我們對芯片、芯片封裝和電路板作了完整的系統級仿真,以揭示如何解決這個問題。”Ansoft使用了該制造商對IC的Spice級模型,作了三維提取,為IC的BGA封裝和PCB(印刷電路板)建立了模型。他說:“我們在自己的環境中將三者全部結合起來,可以預測到這些毛刺。”

?

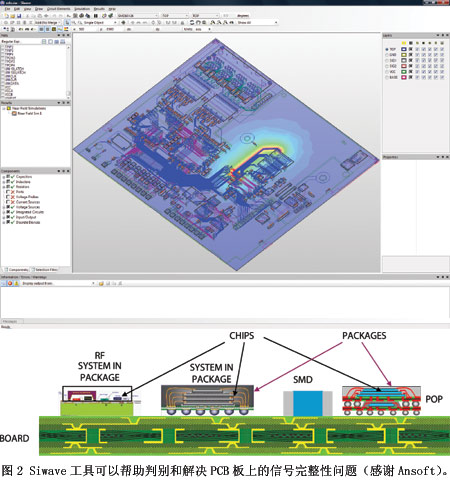

Ansoft的產品包括HFSS(高頻仿真器系統),它可以對高頻高速元件作三維電磁場仿真,還有SIwave(信號完整性波),它使工程師能夠直接從器件版圖數據庫(即物理CAD)中提取出電源分配與信號網表與頻率有關的電路模型,協助判斷信號完整性和電源分配問題(圖2)。Williams說:“我們解決了很多嚴重問題。”他補充說,滿足SI很重要,“各個公司都在設置SI部門,以確保可靠的電性能。看一下現在任何一臺手持電子設備,它可能有多個射頻,很多數字內容能提供豐富的用戶體驗。它會工作在節能的低電壓下,而數字信號也因此對耦合更為敏感。我們讓一個工程設計團隊讀入一個PCB模型,與IC封裝模型的提取相耦合,將所有東西級聯起來,完成一次整體的系統級仿真。”

EEsof的工具包括ADS(先進設計系統),其起源是惠普一個開發RF與微波儀器的小組。ADS 1.0于2000年面世,它使設計者能夠仿真有數字電路(包括DSP)的RF電路。該工具最初大量應用于WLAN(無線局域網)設計,并繼續得到發展。隨著消費產品的制造商努力以更低價格提供更高的功能密度,他們正在小體積中塞入數字、模擬與射頻功能,從而創造出用ADS作芯片、封裝和電路板協同設計與仿真的需求。EEsof的Yap列舉了協同設計過程的兩個方面的實例:前端,它包括針對性能和成本的系統分區優化;后端,涉及如球樣式規劃與布線以及I/O優化等因素。

他表示,最新的發展是支持非線性X參數。上個月,Agilent宣布設計者可以從ADS的仿真或Agilent的測試測量儀器中生成X參數,以加快通信產品的開發。Yap稱,X參數可節省大量時間。有了X參數,設計者就可以獲得一個仿真中使用的模型。否則要做數月的特性描述,生成大量難以解析的圖表。

對于未來,Yap認為會繼續努力將電磁仿真集成到設計流程中,從而從電路到天線的一切都作仿真。更多產品正在無線化,并且在緊湊型產品中,天線一般在PCB板上。他說,在交付實際硬件制造以前發現潛在問題的能力非常關鍵。

附文:EM仿真:從PCB到直升機

隨著產品日益復雜,工作頻率越來越高,研究信號與功率完整性問題,以仿真EMC(電磁兼容)與EMI(電磁干擾)效應也日益重要。CST(Computer Simulation Technology)的PCB(印刷電路板) Studio可以提供幫助,它支持二維與三維仿真,可以在時域與頻域中確定趨膚效應。它可以輸入IBIS(I/O緩沖信息規范)模型,與Spice等效工具接口。CST的Cable Studio支持PCB與連接電纜的協同仿真。

?

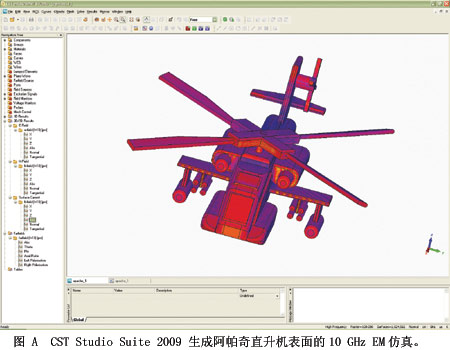

該公司將PCB Studio和Cable Studio整合到Studio Suite 2009 EM仿真軟件中,通過自動優化和對某個問題采用最適當的解算技術,提升了設計的吞吐能力(圖A)。Studio Suite 2009支持瞬態EM和電路協同仿真,它提供一個64位的前端和基于MPI(消息傳遞接口)的并行,加快了大型與復雜結構的仿真速度。它帶有一個瞬時熱解算器,可仿真加熱過程,并用一個生物熱方程作生理冷卻效應的逼真建模。

電子發燒友App

電子發燒友App

評論