隨著電子工程與計(jì)算機(jī)科學(xué)(EECS)的迅猛發(fā)展,數(shù)字電路系統(tǒng)的發(fā)展也十分迅速。電子器件在最近幾十年經(jīng)歷了從小規(guī)模集成電路(SSI)、中規(guī)模集成電路(MSI)到大規(guī)模集成電路(LSI)以至超大規(guī)模集成電路(VLSI)的發(fā)展歷程。從簡(jiǎn)單可編程器件到高密度可編程器件,設(shè)計(jì)方法也在從根本上發(fā)生轉(zhuǎn)變,由原來的手工設(shè)計(jì)到現(xiàn)在的電子設(shè)計(jì)自動(dòng)化(EDA)設(shè)計(jì)。為了提高系統(tǒng)的可靠性與通用性,微處理器和專用集成電路(ASIC)逐漸取代了通用全硬件LSI電路,可編程邏輯器件(PLD)尤其是現(xiàn)場(chǎng)可編程邏輯器件(FPLD)被大量地應(yīng)用在ASIC的制作中,在可編程集成電路的開發(fā)過程中,EDA技術(shù)的出現(xiàn)帶來了電子系統(tǒng)設(shè)計(jì)的革命性變化。

1 EDA技術(shù)的發(fā)展

EDA技術(shù)是伴隨著計(jì)算機(jī)、集成電路、電子系統(tǒng)設(shè)計(jì)的發(fā)展,經(jīng)歷了計(jì)算機(jī)輔助設(shè)計(jì)(CAD)、計(jì)算機(jī)輔助工程設(shè)計(jì)(CAE)和電子系統(tǒng)設(shè)計(jì)自動(dòng)化(ESDA)三個(gè)發(fā)展階段。

20世紀(jì)70年代為CAD階段,這一階段人們開始用計(jì)算機(jī)輔助進(jìn)行IC版圖編輯和PCB布局布線,取代了手工操作。80年代為CAE階段,與CAD相比,除了純粹的圖形繪制功能外,又增加了電路功能設(shè)計(jì)和結(jié)構(gòu)設(shè)計(jì),并通過電氣連接網(wǎng)表將兩者結(jié)合在一起,以實(shí)現(xiàn)工程設(shè)計(jì)。90年代為ESDA階段, ESDA的基本特征是設(shè)計(jì)人員按“自頂向下”的設(shè)計(jì)方法,對(duì)整個(gè)系統(tǒng)進(jìn)行方案設(shè)計(jì)和功能劃分,系統(tǒng)的關(guān)鍵部分用一片或幾片專用集成電路實(shí)現(xiàn),然后采用硬件描述語(yǔ)言(HDL)完成系統(tǒng)行為級(jí)設(shè)計(jì),最后通過綜合器和適配器生成最終的目標(biāo)器件。ESDA的出現(xiàn),使設(shè)計(jì)師開始實(shí)現(xiàn)“概念驅(qū)動(dòng)工程”的夢(mèng)想,從而擺脫了大量的輔助設(shè)計(jì)工作,把精力集中在創(chuàng)造性的方案與概念構(gòu)思上,極大地提高了系統(tǒng)的效率,縮短了產(chǎn)品的研制周期。

2 EDA技術(shù)的基本特征

EDA技術(shù)是在電子CAD技術(shù)基礎(chǔ)上發(fā)展起來的計(jì)算機(jī)軟件系統(tǒng),是指以計(jì)算機(jī)為工作平臺(tái),融合了應(yīng)用電子技術(shù)、計(jì)算機(jī)技術(shù)、信息處理及智能化技術(shù)的最新成果,進(jìn)行電子產(chǎn)品的自動(dòng)設(shè)計(jì)。電子設(shè)計(jì)自動(dòng)化工程是近幾年迅速發(fā)展起來的計(jì)算機(jī)軟件、硬件、微電子交叉的現(xiàn)代電子設(shè)計(jì)學(xué)科,它是以EDA軟件工具為開發(fā)環(huán)境,以硬件描述語(yǔ)言為設(shè)計(jì)語(yǔ)言,以可編程器件為實(shí)驗(yàn)載體,以專用集成電路(ASIC)、片上系統(tǒng)(SOC)芯片為器件目標(biāo),以電子系統(tǒng)設(shè)計(jì)為應(yīng)用方向的電子產(chǎn)品自動(dòng)化設(shè)計(jì)過程[1]。利用EDA工具,電子設(shè)計(jì)師可以從概念、算法、協(xié)議等開始設(shè)計(jì)電子系統(tǒng),大量工作可以通過計(jì)算機(jī)完成,并可以將電子產(chǎn)品從電路設(shè)計(jì)、性能分析到設(shè)計(jì)出IC版圖或PCB版圖的整個(gè)過程在計(jì)算機(jī)上自動(dòng)處理完成。

現(xiàn)代EDA技術(shù)是采用高級(jí)語(yǔ)言描述,具有系統(tǒng)級(jí)仿真和綜合能力,它主要采用并行工程(Concurrent Engineering)設(shè)計(jì)和自頂向下(Top-down)設(shè)計(jì)方法,其基本思想是從系統(tǒng)總體要求出發(fā),分為行為描述、寄存器傳輸級(jí)描述、邏輯綜合三個(gè)層次,將設(shè)計(jì)內(nèi)容逐步細(xì)化,最后完成整體設(shè)計(jì),這是一種全新的設(shè)計(jì)思想與設(shè)計(jì)理念。

3 EDA技術(shù)的發(fā)展趨勢(shì)

????? 進(jìn)入21世紀(jì),全定制和定制專用集成電路正成為新的發(fā)展熱點(diǎn),專用集成電路的設(shè)計(jì)與應(yīng)用必須依靠專門的EDA工具,因此EDA技術(shù)在功能仿真、時(shí)序分析、集成電路自動(dòng)測(cè)試、高速印刷電路板設(shè)計(jì)及操作平臺(tái)的擴(kuò)展等方面都面臨著新的巨大的挑戰(zhàn)。EDA技

????? 術(shù)目前正處于高速發(fā)展階段,每年都有新的EDA工具問世,我國(guó)EDA技術(shù)的應(yīng)用水平長(zhǎng)期落后于發(fā)達(dá)國(guó)家,因此,廣大電子工程人員應(yīng)該盡早掌握這一先進(jìn)技術(shù),這不僅是提高設(shè)計(jì)效率的需要,更是我國(guó)電子工業(yè)在世界市場(chǎng)上生存、競(jìng)爭(zhēng)與發(fā)展的需要。

4 EDA技術(shù)的設(shè)計(jì)流程

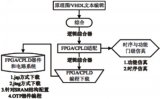

????? EDA技術(shù)是將傳統(tǒng)的“電路設(shè)計(jì)——硬件搭試——調(diào)試焊接”模式變?yōu)椤肮δ茉O(shè)計(jì)——軟件模擬——編程下載”方式,設(shè)計(jì)人員只需一臺(tái)微機(jī)和相應(yīng)的開發(fā)工具即可研制出各種功能電路。EDA技術(shù)將電子產(chǎn)品設(shè)計(jì)從軟件編譯、 邏輯化簡(jiǎn)、 邏輯綜合、 仿真優(yōu)化、 布局布線、 邏輯適配、 邏輯影射、 編程下載 、生成目標(biāo)系統(tǒng)的全過程在計(jì)算機(jī)及其開發(fā)平臺(tái)上自動(dòng)處理完成。具體流程如圖1所示:

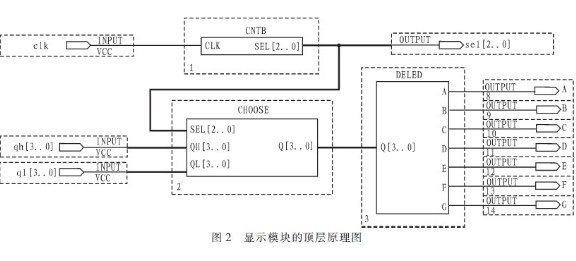

????? 下面以Alter公司的可編程器件的開發(fā)工具M(jìn)AX+plusII為平臺(tái),采用層次化設(shè)計(jì)方法,設(shè)計(jì)一個(gè)十字路口的交通信號(hào)燈的控制電路。

5 EDA技術(shù)的應(yīng)用

????? 設(shè)計(jì)一個(gè)十字路口的交通控制電路,通過紅(R)、黃(Y)、綠(G)燈控制東西和南北兩道交叉路口的交通,要求兩道的通行時(shí)間T1、T2,紅綠燈交替時(shí)間為T3。

????? 實(shí)現(xiàn)路口交通燈系統(tǒng)的控制方法很多,可以用標(biāo)準(zhǔn)邏輯器件、可編程序控制器和單片機(jī)等方案來實(shí)現(xiàn),但這些控制方法的功能修改及調(diào)試需要硬件電路的支持,在一定程度上增加了功能修改及系統(tǒng)調(diào)試的困難。因此在設(shè)計(jì)中采用EDA技術(shù)中的VHDL硬件描述語(yǔ)言,以MAX+plusII開發(fā)環(huán)境進(jìn)行綜合仿真,并下載到CPLD可編程邏輯器件中,完成系統(tǒng)的控制作用。

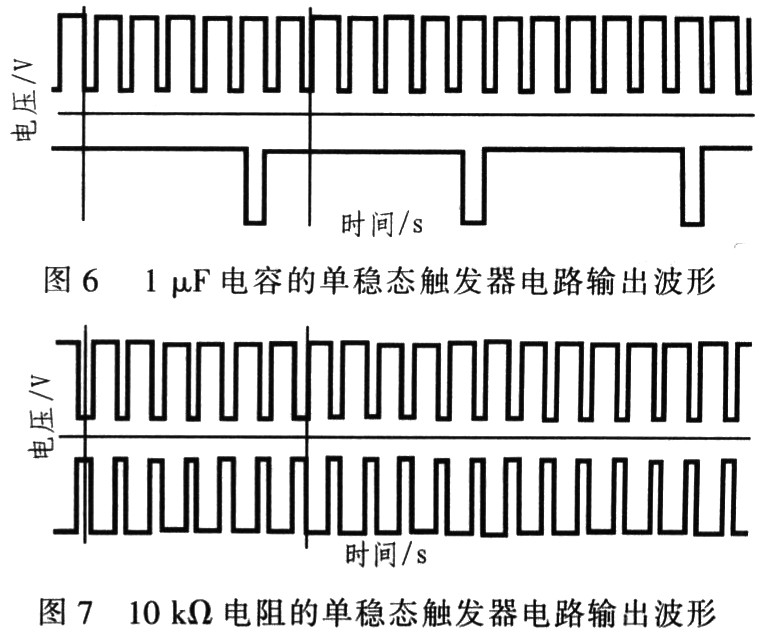

C1、C2、C3為各定時(shí)器的使能控制信號(hào),W1、W2、W3為為各定時(shí)器的狀態(tài)信號(hào),定時(shí)時(shí)間到輸出為1,定時(shí)時(shí)間未到輸出為0。該系統(tǒng)中的定時(shí)器可采用帶預(yù)置功能的減法計(jì)數(shù)器實(shí)現(xiàn),控制器可采用CPLD器件EPM7128系列芯片,秒脈沖信號(hào)CLK可由晶體振蕩器輸出經(jīng)過分頻后產(chǎn)生,當(dāng)精度和穩(wěn)定性要求不高時(shí),可采用RC環(huán)形振蕩器,555定時(shí)器或其它電路產(chǎn)生。根據(jù)該系統(tǒng)的要求。

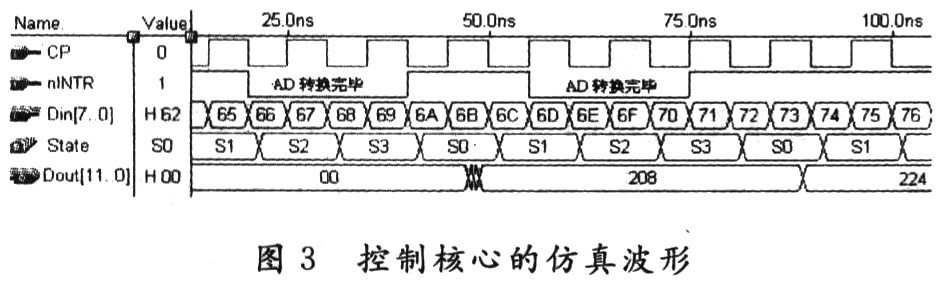

????? 控制器(control)和三個(gè)定時(shí)器(timer)均為VHDL描述,該源程序中三個(gè)定時(shí)器的功能完全一樣,只是工作的預(yù)置數(shù)不同,所以只定義一個(gè)實(shí)體[2]。控制器和定時(shí)器的源程序如下:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY control IS????? —— 控制器實(shí)體說明

?PORT(clk,reset,w1,w2,w3:IN STD_LOGIC);

END control;

ARCHITECTURE beh_control OF control IS?? ——控制體結(jié)構(gòu)體

?TYPE state_type IS (S0,S1,S2,S3);

?SIGNAL state:state_type;

BEGIN

?PROCESS(clk,reset)

?BEGIN

? IF reset=’1’THEN

State<=S0;

?ELSIF(clk’EVENT AND clk=’1’)THEN

CASE state IS

? WHEN S0=>IF w1=’1’THEN

state<=S1;

END IF;

?WHEN S1=>IF w3=’1’THEN

?END IF;

?WHEN S2=>IF w2=’1’THEN

?state<=S3;

END IF;

WHEN S3=>IF w3=’1’THEN

state<=S0;

END IF;

END CASE;

END IF;

END PROCESS;

c1<=’1’WHEN state=S0 ELSE’0’;

c2<=’1’ WHEN state=S2 ELSE’0’;

c3<=’1’ WHEN(state=S1 OR state=S3)ELSE’0’;

r1<=’1’ WHEN(state=S2OR state=S3)ELSE’0’;

g1<=’1’ WHEN state=S0 ELSE’0’;

y1<=’1’ WHEN state=S1 ELSE’0’;

r2<=’1’ WHEN(state=S0 OR state=S1)ELSE’0’;

g2<=’1’ WHEN state=S2 ELSE’0’;

y2<=’1’ WHEN state=S3 ELSE’0’;

END beh_control;

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY timer IS?????????????? ——定時(shí)器實(shí)體說明

PORT(clk,c:IN STD_LOGIC;

d:IN INTEGER RANGE 1TO 31;

w:OUT STD_LOGIC);

END timer;

ARCHITECTURE beh_timer OF timer IS?? ——定時(shí)器結(jié)構(gòu)體

BEGIN

PROCESS(clk)

VARIABLE cnt: INTEGER RANGE 0 TO 31;

BEGIN

IF(clk=’1’)THEN

IF(c=’1’AND cnt>0)THEN

cnt:=cnt-1;

ELSE

cnt:=d;

END IF;

END IF;

IF cnt=0 THEN

w<=’1’;

?ELSE

w<=’0’;

END IF;

END PROCESS;

END beh_timer;

完成了上述兩個(gè)基本模塊,可以形成頂層文件,在MAX+plusII環(huán)境下進(jìn)行編譯和仿真,驗(yàn)證系統(tǒng)功能是否正確,如果出現(xiàn)錯(cuò)誤,需要進(jìn)行修改,直到完全通過為止。當(dāng)設(shè)計(jì)人員確定設(shè)計(jì)工作已基本成功時(shí),即可通過編程電纜下載數(shù)據(jù)流來進(jìn)行硬件驗(yàn)證。驗(yàn)證合格后,總體設(shè)計(jì)工作即圓滿結(jié)束。該系統(tǒng)在編寫控制器的源程序時(shí),有多種編寫方法,以下是控制器的VHDL程序的另外兩種定義方法:

(1)???????

…

ARCHITECTURE con1_arc OF con1 IS

SIGNAL current_state:state;

BEGIN

…

在進(jìn)行時(shí)序分析時(shí),卻出現(xiàn)了不按設(shè)定的計(jì)數(shù)順序工作的結(jié)果:14,13,2,1,0… 經(jīng)過反復(fù)修改調(diào)試,對(duì)程序進(jìn)行修改,如(2)所示:

(2)

ARCHITECTURE con1_arc OF con1 IS

SIGNAL current_state:state;

SIGNAL TEMP_STATE:state;

...

TEMP STATE<=current_state;

BEGIN

...

在這種設(shè)計(jì)方法中,多定義了一個(gè)信號(hào)變量,從而使得程序能按設(shè)定的狀態(tài)14,13,12,11…進(jìn)行轉(zhuǎn)換。

從上述可知:EDA技術(shù)的優(yōu)越性在于可以直接從程序中修改錯(cuò)誤及系統(tǒng)功能,而不需要硬件電路的支持, 即把后期進(jìn)行的系統(tǒng)調(diào)試轉(zhuǎn)移到設(shè)計(jì)實(shí)現(xiàn)之前在計(jì)算機(jī)上進(jìn)行的功能仿真和時(shí)序仿真。使系統(tǒng)的功能修改及調(diào)試比較方便、快捷、準(zhǔn)確,既縮短了研發(fā)周期,又大大節(jié)約了成本。

6 結(jié)語(yǔ)

電子系統(tǒng)的設(shè)計(jì)輸入可以用原理圖、波形、VHDL語(yǔ)言等方式輸入,下載配置前的整個(gè)過程幾乎不涉及到整個(gè)硬件,而硬件設(shè)計(jì)的修改也如同修改軟件程序一樣快捷方便,即通過軟件方式的設(shè)計(jì)與測(cè)試,達(dá)到對(duì)特定功能的硬件電路的設(shè)計(jì)實(shí)現(xiàn),這種現(xiàn)代電子系統(tǒng)設(shè)計(jì)技術(shù)采用自頂向下分層次、模塊化設(shè)計(jì)方法,先化整為零,再優(yōu)化綜合,靈活通用,已成為研制、開發(fā)數(shù)字系統(tǒng)最理想的選擇,是現(xiàn)代電子電路設(shè)計(jì)方法的一個(gè)趨勢(shì),體現(xiàn)了硬件設(shè)計(jì)向軟件化方向發(fā)展的新思路。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論