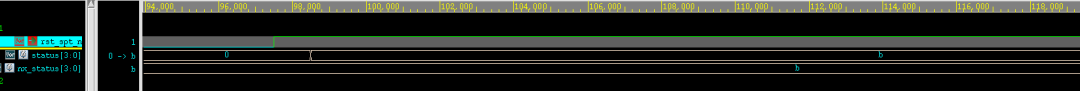

由以上的波形看到狀態機的工作過程符合設計邏輯。對單獨的器件操作也許不需要采用多狀態機的設計方法,但在多器件需要并行工作時,多狀態機的協同設計就顯得必要了。導出VHDL模型塊到ISE中進行仿真后綜合,這里就不多講了,以下是產生的代碼:

-- D:XILINXTUTORIALDUOZTJI.Vhd

LIBRARY Ieee;

USE Ieee.Std_logic_1164.All;

LIBRARY Ieee;

USE Ieee.Std_logic_unsigned.All;

ENTITY SHELL_DUOZTJI IS

PORT (CLK,RESET: IN Std_logic;

Dcounter0,Dcounter1 : OUT Std_logic);

SIGNAL BP_dcounter0,BP_dcounter1,Readcounter0,Readcounter1: Std_logic;

END;

ARCHITECTURE BEHAVIOR OF SHELL_DUOZTJI IS

SIGNAL Sreg : Std_logic_vector (1 DOWNTO 0);

SIGNAL Next_sreg : Std_logic_vector (1 DOWNTO 0);

CONSTANT M0full : Std_logic_vector (1 DOWNTO 0) :="00";

CONSTANT M0writewait : Std_logic_vector (1 DOWNTO 0) :="01";

CONSTANT STATE0 : Std_logic_vector (1 DOWNTO 0) :="10";

CONSTANT Write0 : Std_logic_vector (1 DOWNTO 0) :="11";

SIGNAL Sreg1 : Std_logic_vector (1 DOWNTO 0);

SIGNAL Next_sreg1 : Std_logic_vector (1 DOWNTO 0);

CONSTANT M0empty : Std_logic_vector (1 DOWNTO 0) :="00";

CONSTANT M0readwait : Std_logic_vector (1 DOWNTO 0) :="01";

CONSTANT Read0 : Std_logic_vector (1 DOWNTO 0) :="10";

CONSTANT STATE1 : Std_logic_vector (1 DOWNTO 0) :="11";

SIGNAL Next_BP_dcounter0,Next_BP_dcounter1,Next_readcounter0,

Next_readcounter1 : Std_logic;

SIGNAL BP_dcounter : Std_logic_vector (1 DOWNTO 0);

SIGNAL Dcounter : Std_logic_vector (1 DOWNTO 0);

SIGNAL Readcounter : Std_logic_vector (1 DOWNTO 0);

BEGIN

PROCESS (CLK, Next_sreg, Next_BP_dcounter1, Next_BP_dcounter0)

BEGIN

IF CLK=''1'' AND CLK''Event THEN

Sreg <= Next_sreg;

BP_dcounter1 <= Next_BP_dcounter1;

BP_dcounter0 <= Next_BP_dcounter0;

END IF;

END PROCESS;

PROCESS (CLK, Next_sreg1, Next_readcounter1, Next_readcounter0)

BEGIN

IF CLK=''1'' AND CLK''Event THEN

Sreg1 <= Next_sreg1;

Readcounter1 <= Next_readcounter1;

Readcounter0 <= Next_readcounter0;

END IF;

END PROCESS;

PROCESS (Sreg,Sreg1,BP_dcounter0,BP_dcounter1,Readcounter0,Readcounter1,

RESET,BP_dcounter,Readcounter)

BEGIN

Next_BP_dcounter0 <= BP_dcounter0;Next_BP_dcounter1 <= BP_dcounter1;

Next_readcounter0 <= Readcounter0;Next_readcounter1 <= Readcounter1;

BP_dcounter <= (( Std_logic_vector''(BP_dcounter1, BP_dcounter0)));

Readcounter <= (( Std_logic_vector''(Readcounter1, Readcounter0)));

Next_sreg<=M0full;

Next_sreg1<=M0empty;

IF ( RESET=''1'' ) THEN

Next_sreg<=STATE0;

BP_dcounter <= (Std_logic_vector''("00"));

ELSE

CASE Sreg IS

WHEN M0full =>

Next_sreg<=M0writewait;

BP_dcounter <= (( Std_logic_vector''(BP_dcounter1, BP_dcounter0)));

WHEN M0writewait =>

IF ( (Sreg1=M0empty)) THEN

Next_sreg<=Write0;

BP_dcounter <= (( Std_logic_vector''(BP_dcounter1, BP_dcounter0)) + Std_logic_vector''("01"));

ELSE

Next_sreg<=M0writewait;

BP_dcounter <= (( Std_logic_vector''(BP_dcounter1, BP_dcounter0)));

END IF;

WHEN STATE0 =>

Next_sreg<=Write0;

BP_dcounter <= (( Std_logic_vector''(BP_dcounter1, BP_dcounter0)) +

Std_logic_vector''("01"));

WHEN Write0 =>

IF ( BP_dcounter0=''1'' AND BP_dcounter1=''1'' ) THEN

Next_sreg<=M0full;

BP_dcounter <= (Std_logic_vector''("00"));

ELSE

Next_sreg<=Write0;

BP_dcounter <= (( Std_logic_vector''(BP_dcounter1, BP_dcounter0)) +

Std_logic_vector''("01"));

END IF;

WHEN OTHERS =>

END CASE;

END IF;

IF ( RESET=''1'' ) THEN

Next_sreg1<=STATE1;

Readcounter <= (Std_logic_vector''("00"));

ELSE

CASE Sreg1 IS

WHEN M0empty =>

Next_sreg1<=M0readwait;

Readcounter <= (( Std_logic_vector''(Readcounter1, Readcounter0)));

WHEN M0readwait =>

IF ( (Sreg=M0full)) THEN

Next_sreg1<=Read0;

Readcounter <= (( Std_logic_vector''(Readcounter1, Readcounter0)) +

Std_logic_vector''("01"));

ELSE

Next_sreg1<=M0readwait;

Readcounter <= (( Std_logic_vector''(Readcounter1, Readcounter0)));

END IF;

WHEN Read0 =>

IF ( Readcounter0=''1'' AND Readcounter1=''1'' ) THEN

Next_sreg1<=M0empty;

Readcounter <= (Std_logic_vector''("00"));

ELSE

Next_sreg1<=Read0;

Readcounter <= (( Std_logic_vector''(Readcounter1, Readcounter0)) +

Std_logic_vector''("01"));

END IF;

WHEN STATE1 =>

IF ( (Sreg=M0full)) THEN

Next_sreg1<=Read0;

Readcounter <= (( Std_logic_vector''(Readcounter1, Readcounter0)) + Std_logic_vector''("01"));

ELSE

Next_sreg1<=STATE1;

Readcounter <= (( Std_logic_vector''(Readcounter1, Readcounter0)));

END IF;

WHEN OTHERS =>

END CASE;

END IF;

Next_BP_dcounter1 <= BP_dcounter(1);

Next_BP_dcounter0 <= BP_dcounter(0);

Next_readcounter1 <= Readcounter(1);

Next_readcounter0 <= Readcounter(0);

END PROCESS;

PROCESS (BP_dcounter0,BP_dcounter1,Dcounter)

BEGIN

Dcounter <= (( Std_logic_vector''(BP_dcounter1, BP_dcounter0)));

Dcounter0 <= Dcounter(0);

Dcounter1 <= Dcounter(1);

END PROCESS;

END BEHAVIOR;

LIBRARY Ieee;

USE Ieee.Std_logic_1164.All;

LIBRARY Ieee;

USE Ieee.Std_logic_unsigned.All;

ENTITY DUOZTJI IS

PORT (Dcounter : OUT Std_logic_vector (1 DOWNTO 0);

CLK,RESET: IN Std_logic);

END;

ARCHITECTURE BEHAVIOR OF DUOZTJI IS

COMPONENT SHELL_DUOZTJI

PORT (CLK,RESET: IN Std_logic;

Dcounter0,Dcounter1 : OUT Std_logic);

END COMPONENT;

BEGIN

SHELL1_DUOZTJI : SHELL_DUOZTJI PORT MAP (CLK=>CLK,RESET=>RESET,Dcounter0=>

Dcounter(0),Dcounter1=>Dcounter(1));

END BEHAVIOR;

電子發燒友App

電子發燒友App

評論