集成電路發展趨勢

1、國內外技術現狀及發展趨勢

目前,以集成電路為核心的電子信息產業超過了以汽車、石油、鋼鐵為代表的傳統工業成為第一大產業,成為改造和拉動傳統產業邁向數字時代的強大引擎和雄厚基石。1999年全球集成電路的銷售額為1250億美元,而以集成電路為核心的電子信息產業的世界貿易總額約占世界GNP的3%,現代經濟發展的數據表明,每l~2元的集成電路產值,帶動了10元左右電子工業產值的形成,進而帶動了100元GDP的增長。目前,發達國家國民經濟總產值增長部分的65%與集成電路相關;美國國防預算中的電子含量已占據了半壁江山(2001年為43.6%)。預計未來10年內,世界集成電路銷售額將以年平均15%的速度增長,2010年將達到6000~8000億美元。作為當今世界經濟競爭的焦點,擁有自主版權的集成電路已曰益成為經濟發展的命脈、社會進步的基礎、國際競爭的籌碼和國家安全的保障。

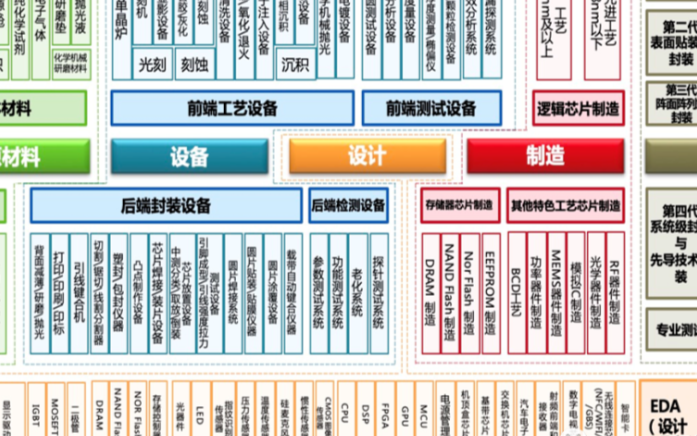

集成電路的集成度和產品性能每18個月增加一倍。據專家預測,今后20年左右,集成電路技術及其產品仍將遵循這一規律發展。 集成電路最重要的生產過程包括:開發EDA(電子設計自動化)工具,利用EDA進行集成電路設計,根據設計結果在硅圓片上加工芯片(主要流程為薄膜制造、曝光和刻蝕),對加工完畢的芯片進行測試,為芯片進行封裝,最后經應用開發將其裝備到整機系統上與最終消費者見面。 20世紀80年代中期我國集成電路的加工水平為5微米,其后,經歷了3、1、0.8、0.5、0.35微米的發展,目前達到了0.18微米的水平,而當前國際水平為0.09微米(90納米),我國與之相差約為2-3代。

(1)設計工具與設計方法。隨著集成電路復雜程度的不斷提高,單個芯片容納器件的數量急劇增加,其設計工具也由最初的手工繪制轉為計算機輔助設計(CAD),相應的設計工具根據市場需求迅速發展,出現了專門的EDA工具供應商。目前,EDA主要市場份額為美國的Cadence、Synopsys和Mentor等少數企業所壟斷。中國華大集成電路設計中心是國內唯一一家EDA開發和產品供應商。

由于整機系統不斷向輕、薄、小的方向發展,集成電路結構也由簡單功能轉向具備更多和更為復雜的功能,如彩電由5片機到3片機直到現在的單片機,手機用集成電路也經歷了由多片到單片的變化。目前,SoC作為系統級集成電路,能在單一硅芯片上實現信號采集、轉換、存儲、處理和I/O等功能,將數字電路、存儲器、MPU、MCU、DSP等集成在一塊芯片上實現一個完整系統的功能。它的制造主要涉及深亞微米技術,特殊電路的工藝兼容技術,設計方法的研究,嵌入式IP核設計技術,測試策略和可測性技術,軟硬件協同設計技術和安全保密技術。SoC以IP復用為基礎,把已有優化的子系統甚至系統級模塊納入到新的系統設計之中,實現了集成電路設計能力的第4次飛躍。

(2)制造工藝與相關設備。集成電路加工制造是一項與專用設備密切相關的技術,俗稱“一代設備,一代工藝,一代產品”。在集成電路制造技術中,最關鍵的是薄膜生成技術和光刻技術。光刻技術的主要設備是曝光機和刻蝕機,目前在130nm的節點是以193nmDUV(Deep Ultraviolet Lithography)或是以光學延展的248nmDUV為主要技術,而在l00nm的節點上則有多種選擇:157nm DIJV、光學延展的193nm DLV和NGL.在70nm的節點則使用光學延展的157nm DIJV技術或者選擇NGL技術。到了35nm的節點范圍以下,將是NGL所主宰的時代,需要在EUV和EPL之間做出選擇。此外,作為新一代的光刻技術,X射線和離子投影光刻技術也在研究之中。

(3)測試。由于系統芯片(SoC)的測試成本幾乎占芯片成本的一半,因此未來集成電路測試面臨的最大挑戰是如何降低測試成本。結構測試和內置自測試可大大縮短測試開發時間和降低測試費用。另一種降低測試成本的測試方式是采用基于故障的測試。在廣泛采用將不同的IP核集成在一起的情況下,還需解決時鐘異步測試問題。另一個要解決的問題是提高模擬電路的測試速度。

(4)封裝。電子產品向便攜式/小型化、網絡化和多媒體化方向發展的市場需求對電路組裝技術提出了苛刻需求,集成電路封裝技術正在朝以下方向發展:

①裸芯片技術。主要有COB(ChipOI1Board)技術和Flip Chip(倒裝片)技術兩種形式。

②微組裝技術。是在高密度多層互連基板上,采用微焊接和封裝工藝組裝各種微型化片式元器件和半導體集成電路芯片,形成高密度、高速度、高可靠的三維立體機構的高級微電子組件的技術,其代表產品為多芯片組件(MCM)。

③圓片級封裝。其主要特征是:器件的外引出端和包封體是在已經過前工序的硅圓片上完成,然后將這類圓片直接切割分離成單個獨立器件。

④無焊內建層(Bumpless Build-Up Layer, BBLIL)技術。該技術能使CPIJ內集成的晶體管數量達到10億個,并且在高達20GHz的主頻下運行,從而使CPU達到每秒1億次的運算速度。此外,BBUL封裝技術還能在同一封裝中支持多個處理器,因此服務器的處理器可以在一個封裝中有2個內核,從而比獨立封裝的雙處理器獲得更高的運算速度。此外,BBUL封裝技術還能降低CPIJ的電源消耗,進而可減少高頻產生的熱量。

(5)材料。集成電路的最初材料是鍺,而后為硅,一些特種集成電路(如光電器件)也采用三五族(如砷化鎵)或二六族元素(如硫化鎘、磷化銦)構成的化合物半導體。由于硅在電學、物理和經濟方面具有不可替代的優越性,故目前硅仍占據集成電路材料的主流地位。鑒于在同樣芯片面積的情況下,硅圓片直徑越大,其經濟‘性能就越優越,因此硅單晶材料的直徑經歷了1、2、3、5、6、8英寸的歷史進程,目前,國內外加工廠多采用8英寸和12英寸硅片生產,16和18英寸(450mm)的硅單晶及其設備正在開發之中,預計2016年左右18英寸硅片將投入生產。

此外,為了適應高頻、高速、高帶寬的微波集成電路的需求,SoI (Silicon-on-Insulator)材料,化合物半導體材料和鍺硅等材料的研發也有不同程度的進展。

(6)應用。應用是集成電路產業鏈中不可或缺的重要環節,是集成電路最終進入消費者手中的必經之途。除眾所周知的計算機、通信、網絡、消費類產品的應用外,集成電路正在不斷開拓新的應用領域,諸如微機電系統,微光機電系統,生物芯片(如DNA芯片),超導等。這些創新的應用領域正在形成新的產業增長點。

(7)基礎研究。基礎研究的主要內容是開發新原理器件,包括:共振隧穿器件(RTD)、單電子晶體管(SET)、量子電子器件、分子電子器件、自旋電子器件等。技術的發展使微電子在21世紀進入了納米領域,而納電子學將為集成電路帶來一場新的革命。

2 我國集成電路產業現狀

我國集成電路產業起步于20世紀60年代,2001年全國集成電路產量為64億塊,銷售額200億元人民幣。2002年6月,共有半導體企事業單位(不含材料、設備)651家,其中芯片制造廠46家,封裝、測試廠108家,設計公司367家,分立期間廠商130家,從業人員11.5萬人。設計能力0.18~0.25微米、700萬門,制造工藝為8英寸、0.18~0.25微米,主流產品為0.35~0.8微米。

與國外的主要差距:一是規模小,2000年,國內生產的芯片銷售額僅占世界市場總額的1.5%,占國內市場的20%;二是檔次低,主流產品加工技術比國外落后兩代;三是創新開發能力弱,設計、工藝、設備、材料、應用、市場的開發能力均不十分理想,其結果是今天受制于人,明天后勁乏力;四是人才欠缺。

總之,我國絕大多數電子產品仍處于流通過程中的下端,多數組裝型企業扮演著為國外集成電路廠商打工的角色,這種脆弱的規模經濟模式,因其附加值極低,致使諸多產量世界第一的產品并未給企業和國家帶來可觀的收益,反而使掌握關鍵技術的競爭者通過集成電路打入中國市場,攫取了絕大部分的利潤。

3 發展重點和關鍵技術

由于集成電路產品是所有技術的最終載體,是一切研究成果的最終體現,是檢驗技術轉化為生產力的最終標志,所以,產品是綱,技術是目,必須以兩個核心產品為龍頭,帶動兩組產品群的開發。利用CPIJ技術開發與之相關的MPU(微處理器)、MCU(微控制器)、DSP(數字信號處理器)等系列產品;利用3C芯片組的技術開發與之相關的DVD、HDTV、數碼相機、數碼音響等專用集成電路系列產品。因此,未來一段時期,我國應該開發研究以下關鍵技術。

(1)亞100納米可重構SoC創新開發平臺與設計工具研究。當前,集成電路加工已進入亞100納米階段,與其對應的設計工具尚無成熟產品推向市場,而我國EDA工具產品雖與世界先進水平存有較大差距,但也具備了20多年的技術儲備和經驗積累,開發亞100納米可重構SoC創新開發平臺與設計工具是實現我國集成電路產業跨越式發展的重要機遇。

該項目主要內容包括:基于亞100納米工藝的集成電路設計方法學研究與設計工具開發、可重構SoC創新開發平臺技術與IP測評技術研究、數模混合與射頻電路設計技術研究與設計工具開發等。

(2)SoC設計平臺與SIP重用技術。基于平臺的SoC設計技術和硅知識產權(SIP)的重用技術是SoC產品開發的核心技術,是未來世界集成電路技術的制高點。

項目主要內容包括:嵌入式CPU、DSP、存儲器、可編程器件及內部總線的SoC設計平臺;集成電路IP的標準、接口、評測、交易及管理技術;嵌入式CPII主頻達IGHz,并有相應的協處理器;在信息安全、音視頻處理上有10~12種平臺;集成電路IP數量達100種以上等。

(3)新興及熱門集成電路產品開發。項目主要內容包括:64位通用CPU以及相關產品群、3C多功能融合的移動終端芯片組開發(802.11協議)、網絡通信產品開發、數字信息產品開發、平面顯示器配套集成電路開發等。

(4)10納米1012赫茲CMOS研究。項目的研究對象為特征寬度為10nm的CMOS器件,主要內容有:Silicon on Insulator(SOI)技術、雙柵介質結構(Double Gate Structure)技術、應變硅襯底(Strained Si)技術、高介電常數柵介質技術(High-k)、金屬電極技術(Metal Gate)、超淺結形成技術(Ultra Shallow Junction)、低介電常數介質材料(low-K)的選擇、制備及集成、銅互聯技術的完善、CMP技術、清洗技術等。

(5)12英寸90/65納米微型生產線。項目主要內容有:等離子體氮化柵SiON薄膜(等效膜厚《1.5nm)的形成工藝;Hf02、Zr02等新型高介電常數(high-K)棚介質的制備方法、high-K/Si界面質量控制、high-K柵介質的穩定性和可靠性,探索金屬柵新結構的制備工藝,獲得適用于65nm CMOS制造的新型柵疊層(gate stack)結構技術;超淺結形成技術、Co-Ni系自對準金屬硅化物接觸互連技術結合Si/SiGe選擇外延技術,探索提升源漏新結構的制備方法、形成超低接觸電阻率金半接觸體系,獲得適用于納米CMOS制造的新型超淺結和自對準金屬硅化物技術;多晶SiGe電極的形成方位,獲得低耗盡多晶柵電極、低阻抗的柵電極形成技術;研究銅/低介電常數介質(Cu/low-K)制備方法、low-K的穩定性及可加工性、Cu/low-K界面可靠性和質量控制,獲得適用于納米CMOS器件的后端互連技術等。

(6)高密度集成電路封裝的工業化技術。項目主要內容包括:系統集成封裝技術、50微米以下的超薄背面減薄技術、圓片級封裝技術、無鉛化產品技術等。

(7)SoC關鍵測試技術研究。項目主要內容包括:通過5~10年,在國內建立若干個支持千萬門級、1GHz、1024Pin的SoC設計驗證平臺和生產測試平臺;SoC設計一測試自動鏈接技術研究;DFT的測試實現和相關工具開發;高頻、高精度測試適配器自主設計技術g測試程序設計方法及建庫技術;關鍵測試技術研究;SoC產業化測試關鍵技術研究等。

(8)直徑450mm硅單晶及拋光片制備技術。根據國際半導體發展指南預測,直徑450mm硅單晶及拋光片將有可能在2016年左右投入應用,成為30Omm之后大規模應用的硅片。預計屆時DRAM的線寬將達到22nm,對硅拋光片的質量將達到前所未有的高度,比如,硅片的局部平整度要≤22nm,每片大于11nm的表面顆粒≤95個,晶體缺陷(氧化層錯)密度≤0.2個/cm2.這些都將對現有硅片加工技術提出挑戰,需要研發大量的創新性技術,從而將帶動整個精細加工技術的發展和進步,而450mm硅片的開發和應用將帶動整個微電子領域的跨越式發展。以每個DRAM芯片預計面積238mm2記,每片硅片上將可以生產500個以上的芯片,這將大大提高生產效率,其應用范圍將十分廣泛。

(9)應變硅材料制備技術。應變硅的電子和空穴遷移率明顯高于普通的無應變硅材料,其中以電子遷移率提高尤為明顯。以Si0.8Ge0.2層上的應變硅為例,其電子遷移率可以提高50%以上,這大大提高了NMOS器件的性能,對高速高頻器件來說有至關重要的作用。對現有的許多集成電路生產線而言,如果采用應變硅材料,則可以在基本不增加投資的情況下使生產的IC性能明顯改善,還可以大大延長花費巨額投資建成的IC生產線的使用年限。

目前有希望在未來幾年內獲得應用的應變硅材料是采用應變Si/SiGe/Si02(SOI)結構:在無應變的SiGe層上的Si層因二者間品格參數的差異而形成應變硅,下面的Si02可以起到電學隔離作用,這是淺結(全耗盡)器件所必須的。預計到2010~2013年,SiGe層中Ge的摩爾含量可以做到10%~20%,應變硅的電子遷移率可以比無應變硅提高約30%~70%.

(10)60納米節點刻蝕設備(介質刻蝕機)。項目主要內容:要求各向異性刻蝕,刻出符合CD偏差要求的線條;刻蝕剖面(Etch Profile)接近900;大面積片子上要保持均勻他密集線條與孤立線條要求刻蝕速率的一致,即要求小的微負載效應;在柵刻蝕中避免將柵刻穿,要求不同材料的刻蝕速率要大,即選擇比較大;為了保持各向異性刻蝕的剖面,刻蝕過程中要形成側壁鈍化,并要考慮刻蝕后的清除;要提高刻蝕成品率必須設法降低缺陷密度和缺陷尺寸;要解決所謂天線效應造成的Plasma電荷積累損傷;對刻蝕殘留物要解決自清洗問題,以提高二次清洗間平均間隔時間(MTBC)和縮短清洗和恢復平均時間(MTTCR)以提高開機時間需要解決新一代光刻膠帶來的線條邊緣粗糙度問題,等一系列新問題。而對于大生產設備而言,還要解決生產率,重復性、成品率,耐久性、可靠性、安全環保和較大的工藝窗口等諸多問題。

(11)60納米節點曝光設備(F2準分子激光曝光機)。F2準分子激光步進掃描機將從70nm介入,可引伸到50nm,因此它涵蓋了60nm技術節點,與下一代曝光(NGL)比,最為重要的是可在大氣下工作,而NGL都要在真空中進行。據SEMATECH比較,157成本比EUV低,而產量比它們高,157是光學曝光技術平臺的延伸,更能為用戶接受,157的研發可借用很多193機的部件,157機的成本約$2000萬/臺。現在ASML公司和SVGL公司合并后與Carl Zeiss, AMD, Motorola, Philips,TSMC等公司宣布2003年推出生產型157nm曝光機,分辨率為70nm,預計在2004年包括抗蝕劑、掩模、工藝及設備本身將完全成熟,在2005年后可能承擔大量生產的工藝任務,若增加分辨率增強技術(RET)就能夠做到50nm工藝。157nm的設備根據SVGL設計共18個部件,其中需要6個新部件,他們是曝光光源、光束傳輸系統、照明光學系統、劑量/曝光量控制、投影光學和環境控制系統。從材料上講,用CaF2材料制作的分束器立方體的單晶和制造是十分關鍵的問題,SVGL已發展出了15寸CaF2大單晶鍵。此外窄帶寬激光器、折反射光學系統等關鍵技術問題均有待突破。

電子發燒友App

電子發燒友App

評論