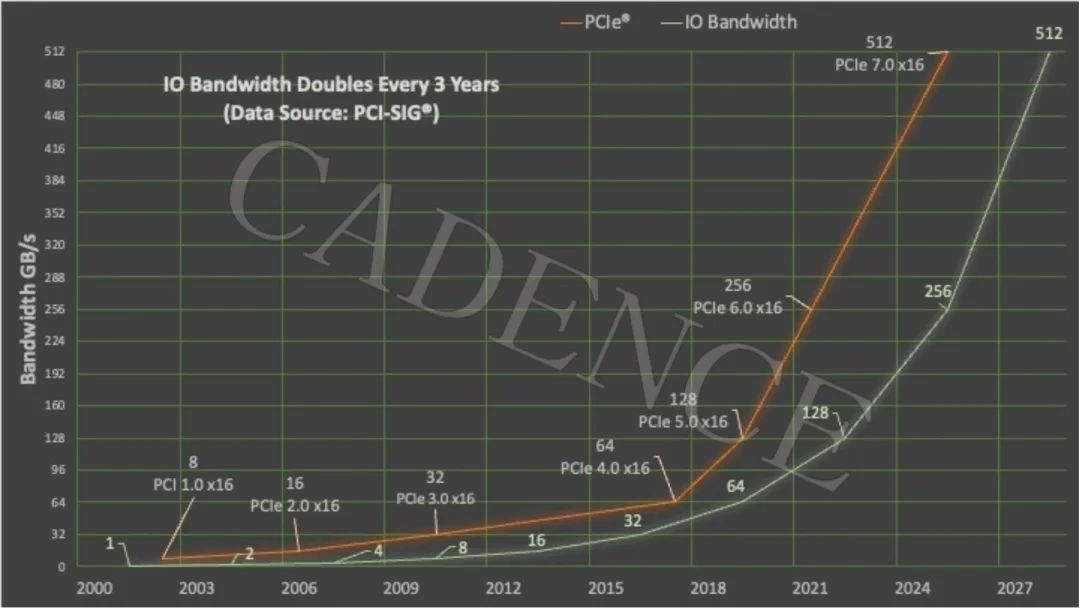

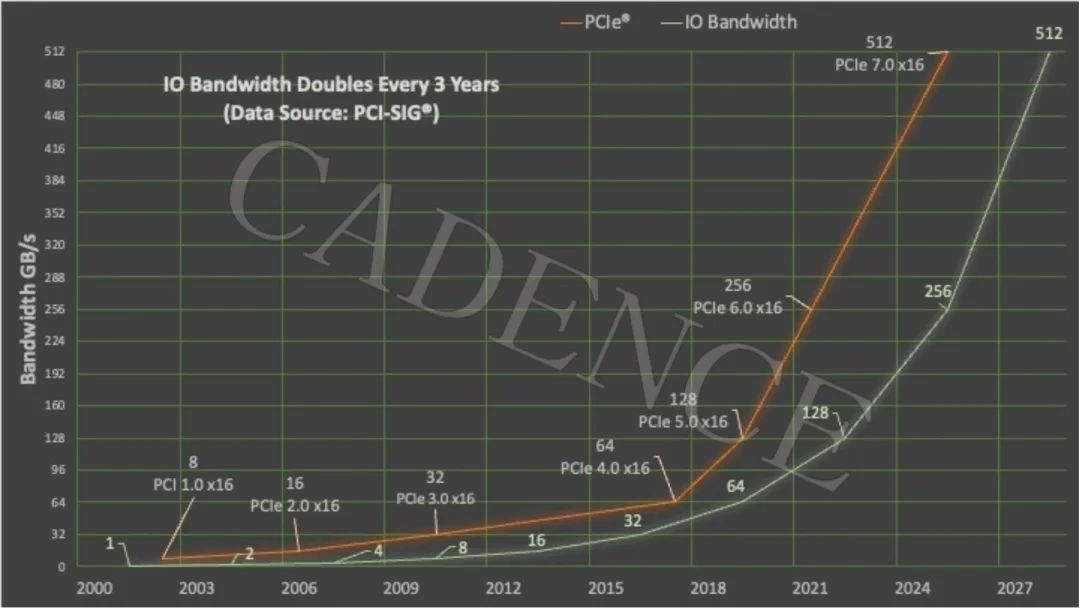

PCIe標(biāo)準(zhǔn)自從推出以來(lái),1代和2代標(biāo)準(zhǔn)已經(jīng)在PC和Server上逐漸普及,用于滿足高速顯卡、高速存儲(chǔ)設(shè)備對(duì)于高速數(shù)據(jù)傳輸?shù)囊蟆3鲇谥С指呖偩€數(shù)據(jù)吞吐率的目的,PCI-SIG組織在2010年制定了PCIe 3.0,即PCIe 3代的規(guī)范,數(shù)據(jù)速率達(dá)到8Gbps。

2023-02-13 15:01:02 3217

3217

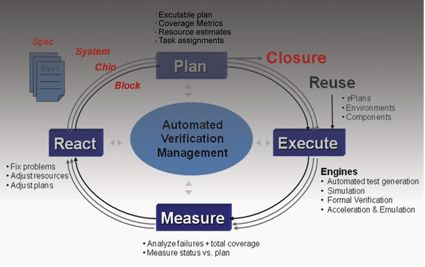

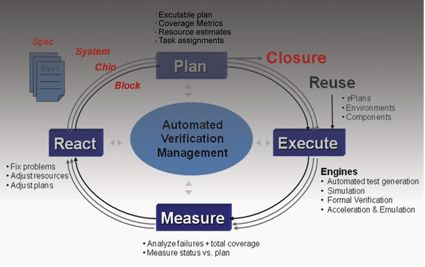

Cadence設(shè)計(jì)系統(tǒng)公司公布一個(gè)新版的尖端功能驗(yàn)證平臺(tái)與方法學(xué),擁有全套最新增強(qiáng)功能,與之前發(fā)布的版本相比,可將SoC驗(yàn)證效率提高一倍。 Incisive ?12.2提供了兩倍性能,全新Incisive調(diào)試分析器產(chǎn)品,全新低功耗建模,以及當(dāng)今復(fù)雜IP與SoC高效驗(yàn)證所需的數(shù)百種其他功能。

2013-01-27 10:44:38 1437

1437

Cadence公司日前發(fā)布用于新型USB SuperSpeed Inter-Chip規(guī)格的經(jīng)過(guò)生產(chǎn)驗(yàn)證的VIP,使用戶可以充分驗(yàn)證部署最新的USB3.0協(xié)議擴(kuò)展的設(shè)計(jì)。

2013-02-20 08:49:09 1503

1503

全球電子設(shè)計(jì)創(chuàng)新領(lǐng)先企業(yè)Cadence設(shè)計(jì)系統(tǒng)公司(NASDAQ: CDNS),近日推出新版本Incisive Enterprise Simulator,該版本將復(fù)雜SoC的低功耗驗(yàn)證效率提高了30

2013-05-14 10:31:40 1832

1832 意味著通過(guò)臺(tái)積電嚴(yán)格的EDA工具驗(yàn)證過(guò)的Cadence Tempus 時(shí)序簽收解決方案能夠確保客戶實(shí)現(xiàn)先進(jìn)制程節(jié)點(diǎn)的最高精確度標(biāo)準(zhǔn)。

2013-05-24 11:31:17 1345

1345 Jitter 、CM Jitter 等)及PeRT3 能夠實(shí)現(xiàn)的功能及連接示意圖: PCIE 3.0 接收端測(cè)試抖動(dòng)源校準(zhǔn)連接示意圖: 來(lái)自于PCIE 3.0 規(guī)范的接收機(jī)測(cè)試的抖動(dòng)源校準(zhǔn)連接圖

2018-09-26 17:33:30

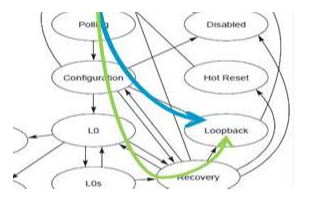

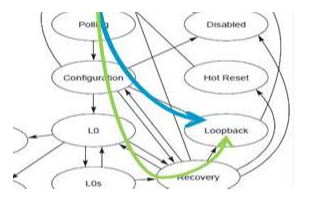

代替8b/10b編碼,使得編碼效率大幅提高;另一個(gè)是使用動(dòng)態(tài)均衡技術(shù),來(lái)代替先前代的靜態(tài)均衡技術(shù)。 這里聚焦于PCIe 3.0和4.0中的動(dòng)態(tài)均衡技術(shù),介紹其原理、實(shí)現(xiàn)及其相關(guān)的一致性測(cè)試 。這樣一種

2020-11-25 06:19:43

有沒(méi)有辦法確認(rèn) i.MX6SX PCIe RX 終端的設(shè)置。我在 i.MX6SX 上看到 PCIe 實(shí)現(xiàn)的 PCIe RX SI 結(jié)果可能表明 RX 終端設(shè)置為 OFF,我正在尋找一種方法來(lái)確認(rèn)。PCIe PHY 寄存器沒(méi)有內(nèi)存映射,我不確定控制器是否正在更改設(shè)置。

2023-05-12 06:40:33

`cadence初入門哈,求問(wèn),下面這張圖可以直接跑仿真么?我意思是,,這不是編輯后的簡(jiǎn)化模塊兒么,還能在cadence上直接驗(yàn)證邏輯功能么?`

2014-04-18 03:29:28

ALLEGRO導(dǎo)出CSV格式的坐標(biāo)文件該方案是本人使用cadence allegro 17.2版本驗(yàn)證。16.6版本待驗(yàn)證。具體操作如下1、Tools→Reports2、找到placed component report并雙擊

2019-07-04 21:21:47

UD PCIe-404全國(guó)產(chǎn)化信號(hào)處理模塊為標(biāo)準(zhǔn)PCIe全高的結(jié)構(gòu),對(duì)外支持PCIe3.0×8通信,也可以采用千兆以太網(wǎng)(RJ45連接器)、萬(wàn)兆以太網(wǎng)(或RapidIO、Aurora,QSFP+

2023-05-21 18:27:41

iTOP3A5000開發(fā)板多路PCIE、SATA、USB3.0等橋片:支持PCIE3.0、USB3.0、SATA3.0、顯示接口2路、HDMI和1路VGA、可直接連顯示器,另外內(nèi)置一個(gè)網(wǎng)絡(luò)PHY,片

2022-12-01 15:31:54

與 RS485 收發(fā)器一起使用。 過(guò)去,我已經(jīng)編寫了一個(gè)簡(jiǎn)單的代碼來(lái)使用 uart_adapter 通過(guò)帶有緩沖區(qū)機(jī)制的 UART 發(fā)送和獲取字節(jié)。然后在 MCUExpresso 上,在 SDK 組件上,我添加

2023-03-24 07:36:40

TB-RK1808M0 使用官方Mini-PCIe轉(zhuǎn)USB3.0小板 只支持USB3.0?TB-RK1808M0 使用官方Mini-PCIe轉(zhuǎn)USB3.0小板 插在USB 2.0 口上 會(huì)反復(fù)重啟。3.0口正常。

2022-07-20 16:40:53

Atlas200I A2+PCIE X4接口測(cè)試FPGA 實(shí)物圖片

全愛(ài)科技QA200A2 Altas200I A2開發(fā)套件做了驗(yàn)證。

圖 1-2 QA200A2 Atlas200I A2 開發(fā)套件實(shí)物圖

2023-09-05 14:39:57

如何對(duì)PCIe3.0接收機(jī)物理層進(jìn)行測(cè)試?

2021-05-11 06:04:51

我正在嘗試對(duì) TC365 的 UCB 扇區(qū)進(jìn)行重新編程。 我目前正在檢查來(lái)自 HF_confirmx 寄存器的確認(rèn)狀態(tài),以避免它們被鎖定時(shí)出現(xiàn)擦除故障。 但是,我注意到,即使確認(rèn)碼已寫入 “已確認(rèn)

2024-01-22 07:39:10

時(shí),則應(yīng)對(duì)引入的標(biāo)準(zhǔn)方法進(jìn)行驗(yàn)證,并正確有效地運(yùn)用。 標(biāo)準(zhǔn)方法確認(rèn)準(zhǔn)則:所用的設(shè)備、環(huán)境條件、人員技術(shù)等。以證明實(shí)驗(yàn)室能夠正確使用該新標(biāo)準(zhǔn)實(shí)施檢測(cè)過(guò)程。 標(biāo)準(zhǔn)方法的確認(rèn)或是通過(guò)核查方式,并提供客觀證據(jù)

2017-11-14 14:39:11

一塊帶有PCIE接口的FPGA,一塊PCIE轉(zhuǎn)USB3.0板卡,想通過(guò)FPGA控制PCIE轉(zhuǎn)USB3.0板卡,實(shí)現(xiàn)USB3.0讀入數(shù)據(jù),經(jīng)過(guò)FPGA高速處理,不需要經(jīng)過(guò)電腦CPU。請(qǐng)問(wèn)各位專家:1.

2014-12-25 22:54:58

/ PCIE3.0/ PCIE2.1/ SATA3.0/QSGMII引腳擴(kuò)展: 引出腳多達(dá)320個(gè),滿足用戶各類擴(kuò)展需求底板參數(shù)尺寸: 190mm*125mmPOWER: 電直流電源輸入接口SWITCH: 電源開關(guān)

2022-04-29 10:03:28

問(wèn)題描述及復(fù)現(xiàn)步驟:PCIE通常采用Common REFCLK Rx Architecture (CC):PCIE Separate Refclk Architecture:請(qǐng)問(wèn)3588Q pcie3.0 RC和EP端是否支持采用獨(dú)立的REFCLK時(shí)鐘。如果支持,有沒(méi)有特殊要注意的地方。

2023-02-07 15:13:55

我對(duì)第 3 代存儲(chǔ)進(jìn)行了測(cè)試。但是 LS1046A RDB 指示此存儲(chǔ)是 Gen2。那么,我的問(wèn)題是:LS1046ARDB 是否支持 PCIE 3.0?

2023-04-06 06:30:54

系列FPGA實(shí)現(xiàn)PCIe接口所涉及的硬件板卡參數(shù)、應(yīng)用層系統(tǒng)方案、DMA仲裁、PCIe硬核配置與讀寫時(shí)序等內(nèi)容。

2019-05-21 09:12:26

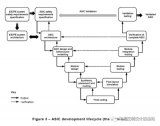

PCIe 2.0/PCIe 3.0驗(yàn)證、調(diào)試和一致性測(cè)試解決方案:Agenda• Introduction to PCI Express 3.0– Trends

2010-06-29 17:14:12 85

85 Cadence推出首個(gè)TLM驅(qū)動(dòng)式設(shè)計(jì)與驗(yàn)證解決方案

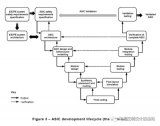

Cadence設(shè)計(jì)系統(tǒng)公司今天推出首個(gè)TLM驅(qū)動(dòng)式協(xié)同設(shè)計(jì)與驗(yàn)證解決方案和方法學(xué),使SoC設(shè)計(jì)師們可以盡享事務(wù)級(jí)建模(TLM)的好處。

2009-08-07 07:32:00 674

674 Cadence推出首個(gè)TLM驅(qū)動(dòng)式設(shè)計(jì)與驗(yàn)證解決方案提升基于RTL流程的開發(fā)效率

Cadence設(shè)計(jì)系統(tǒng)公司推出首個(gè)TLM驅(qū)動(dòng)式協(xié)同設(shè)計(jì)與驗(yàn)證解決方案和方法學(xué),使SoC設(shè)計(jì)師們可以盡

2009-08-11 09:12:18 499

499 Cadence為PCI Express 3.0推出首款驗(yàn)證解決方案

Cadence設(shè)計(jì)系統(tǒng)公司宣布其已經(jīng)開發(fā)了基于開放驗(yàn)證方法學(xué)(OVM)的驗(yàn)證IP(VIP)幫助開發(fā)者應(yīng)用最新的PCI Express Base Specification

2009-11-04 16:59:59 1142

1142 力科在DesignCon 2010上首家發(fā)布PCIe 3.0綜合測(cè)試解決方案

第一個(gè)支持PCIe 3.0的高性能通訊發(fā)生器和練習(xí)器 Summit Z3-16 Exerciser同步2臺(tái)WaveMaster 8 Zi 在4通道上同時(shí)提供30GHz帶

2010-02-08 16:13:37 612

612 PCIe 3.0新標(biāo)準(zhǔn)將于11月推出

最新消息顯示,PCI Express 3.0標(biāo)準(zhǔn)的基本規(guī)范有望在今年11月份最終完成,從而為相關(guān)產(chǎn)品明年問(wèn)世敞開大門

2010-09-20 09:02:39 1408

1408 Pericom發(fā)布全新高速PCIe 3.0信號(hào)交換、信號(hào)質(zhì)量及頻率控制解決方案

全面創(chuàng)新的產(chǎn)品線支持最新的PCI Express® 8Gb傳輸速率,可應(yīng)用在

2010-11-19 15:30:50 825

825 Pericom Semiconductor Corporation日前宣布:推出面向PCI Express (PCIe) 3.0的 ReDriver信號(hào)調(diào)節(jié)(signal conditioner)、信號(hào)交換(signal swit

2010-11-22 08:50:03 1120

1120 Cadence設(shè)計(jì)系統(tǒng)公司600多種新功能擴(kuò)展了指標(biāo)驅(qū)動(dòng)型驗(yàn)證(MDV)的范圍,幫助工程師實(shí)現(xiàn)更快、更全面的驗(yàn)證閉合與硅實(shí)現(xiàn)。

2011-01-13 11:26:17 768

768 PCIe 3.0的技術(shù)架構(gòu)上相較于PCIe 2.0有了顯著的改進(jìn),同時(shí)也在制造面、成本、功耗、設(shè)計(jì)復(fù)雜度與兼容性之間進(jìn)行適當(dāng)取舍并截取優(yōu)化的部份。

2011-02-27 22:29:21 1360

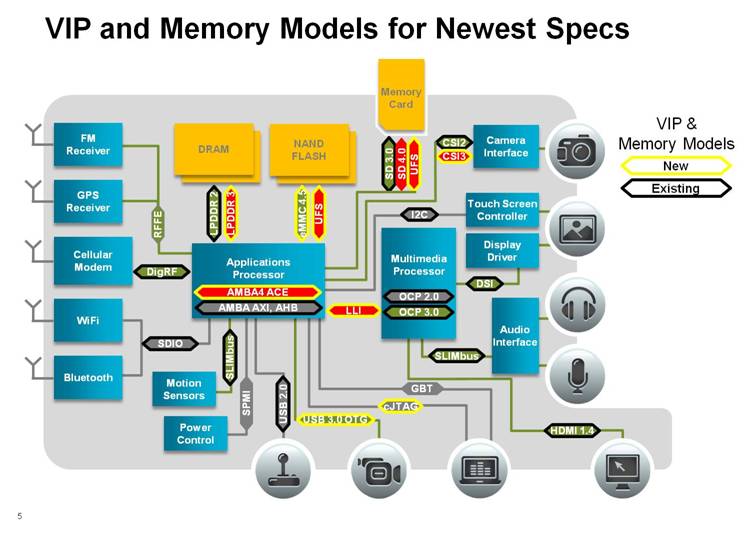

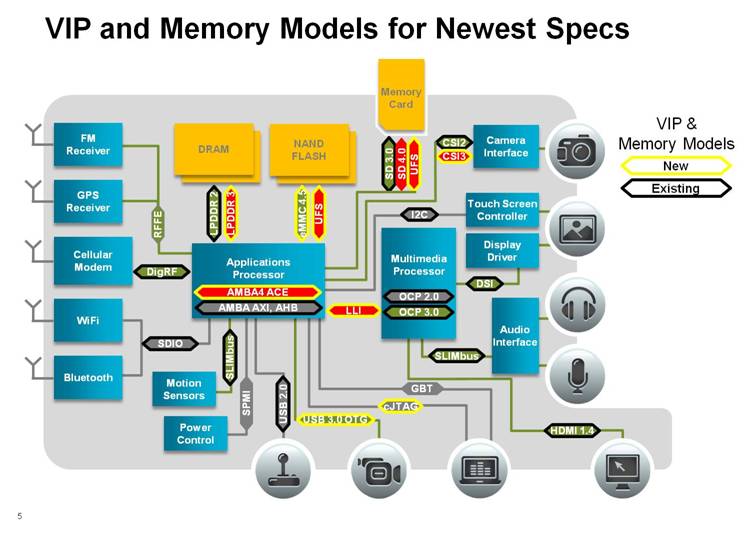

1360 電子設(shè)計(jì)創(chuàng)新企業(yè)Cadence設(shè)計(jì)系統(tǒng)公司,今天宣布使用ARM AMBA協(xié)議類型的Cadence驗(yàn)證IP(VIP)實(shí)現(xiàn)多個(gè)成功驗(yàn)證項(xiàng)目,這是業(yè)界最廣泛使用的AMBA協(xié)議系列驗(yàn)證解決方案之一。頂尖客戶,包括

2012-11-07 08:21:52 997

997 PCIE 3.0相對(duì)于它的前一代PCIE 2.0的最主要的一個(gè)區(qū)別是速率由5GT/s提升到了8GT/s。為了保證數(shù)據(jù)傳輸密度和直流平衡以及時(shí)鐘恢復(fù),PCIE 2.0中使用了8B/10B編碼,即將每8位有效數(shù)據(jù)編碼為10位

2012-12-03 11:45:13 55

55 因?yàn)?b class="flag-6" style="color: red">PCIE 3.0信號(hào)的速率可以達(dá)到8Gb/s,而且鏈路通道走線也可能會(huì)很長(zhǎng),這可能會(huì)導(dǎo)致高速信號(hào)衰減過(guò)大,在接收端無(wú)法得到張開的眼圖。因此在PCIE 3.0的Tx和Rx端均使用了均衡設(shè)置,以補(bǔ)

2012-12-10 10:51:01 41

41 通過(guò)對(duì)Evatronix公司的收購(gòu),Cadence就能順理成章地進(jìn)入移動(dòng)、連線與云端市場(chǎng)領(lǐng)域。Evatronix公司提供的獲得芯片驗(yàn)證的IP產(chǎn)品陣容,包括公認(rèn)的 USB 2.0 /3.0、顯示器

2013-05-20 09:27:46 2397

2397 9月26日——全球電子設(shè)計(jì)創(chuàng)新領(lǐng)先企業(yè)Cadence設(shè)計(jì)系統(tǒng)公司(納斯達(dá)克股票代碼:CDNS)今天宣布可提供業(yè)界首款支持全新HDMI 2.0規(guī)范的驗(yàn)證IP(VIP)。這款VIP使設(shè)計(jì)師們可以快速

2013-09-27 16:19:08 857

857 日益增長(zhǎng)的驗(yàn)證復(fù)雜性正推動(dòng)著包括形式分析的多種互補(bǔ)驗(yàn)證方法的需求,而 Jasper是快速增長(zhǎng)形式分析行業(yè)的領(lǐng)導(dǎo)者,目標(biāo)針對(duì)各種復(fù)雜驗(yàn)證的挑戰(zhàn),Cadence與Jasper的結(jié)合將擴(kuò)大產(chǎn)業(yè)最強(qiáng)與最廣泛的系統(tǒng)驗(yàn)證產(chǎn)品的差異性優(yōu)勢(shì)。

2014-04-25 18:32:48 2326

2326 2017年2月7日,中國(guó)上海 —— 楷登電子(美國(guó) Cadence 公司,NASDAQ: CDNS)今日正式發(fā)布全新Sigrity 2017技術(shù)的系列產(chǎn)品,新增多項(xiàng)核心功能,專為加速PCB電源及信號(hào)

2017-02-07 15:39:26 1266

1266 2017年3月2日,上海——楷登電子(美國(guó) Cadence 公司,NASDAQ: CDNS)今日發(fā)布全新基于FPGA的Protium? S1原型驗(yàn)證平臺(tái)。借由創(chuàng)新的實(shí)現(xiàn)算法,平臺(tái)可顯著提高工程生產(chǎn)

2017-03-02 11:13:11 2744

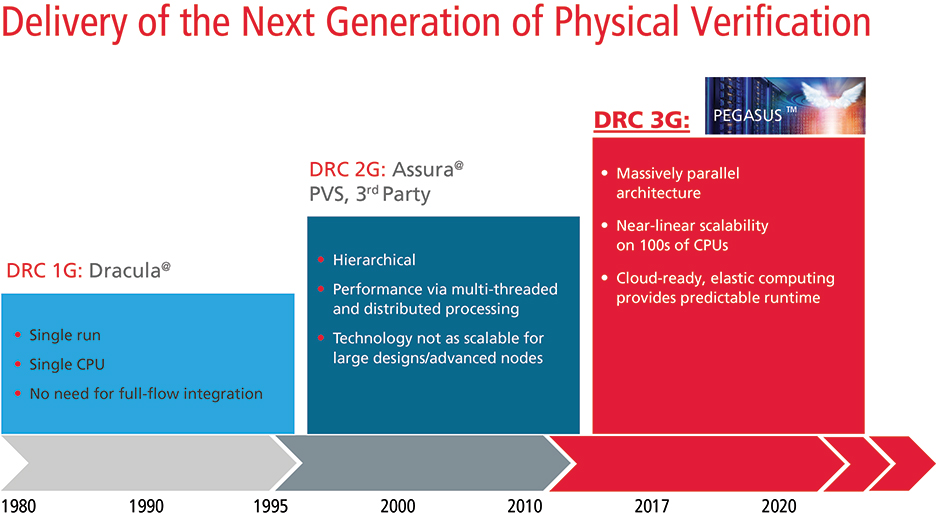

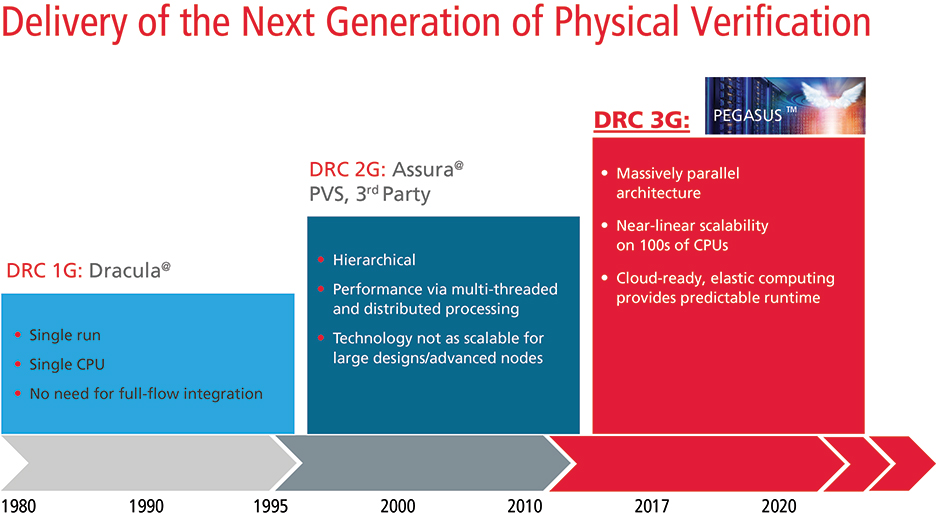

2744 2017年4月14日,中國(guó)上海 - 楷登電子(美國(guó) Cadence 公司,NASDAQ: CDNS)今日正式發(fā)布Pegasus?驗(yàn)證系統(tǒng),該云計(jì)算(cloud-ready)大規(guī)模并行物理簽核解決方案

2017-04-14 15:42:44 1294

1294

中國(guó)上海,2017年6月12日 – 楷登電子(美國(guó)Cadence公司,NASDAQ: CDNS)今日發(fā)布全新Cadence? Virtuoso? System Design Platform

2017-06-13 14:26:28 2937

2937 本文實(shí)現(xiàn)的基于FPGA的PCIe總線接口的DMA控制器是在Altera PHY IP和Synopsys Core IP的基礎(chǔ)上實(shí)現(xiàn)的,利用Synopsys VIP驗(yàn)證環(huán)境進(jìn)行了功能仿真驗(yàn)證

2018-01-11 10:57:04 11281

11281

今日晚間(5月5日),一加CEO劉作虎對(duì)外確認(rèn),一加7系列將全部采用UFS 3.0閃存。

2019-05-06 09:00:02 2779

2779 驗(yàn)證與確認(rèn)是功能安全中重要但相互獨(dú)立的兩個(gè)主題。然而,這兩個(gè)術(shù)語(yǔ)經(jīng)常被誤用和混淆,包括我最近正在閱讀的一份功能安全標(biāo)準(zhǔn)初稿。

2019-05-29 15:07:44 2758

2758

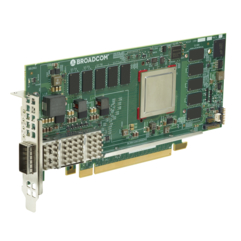

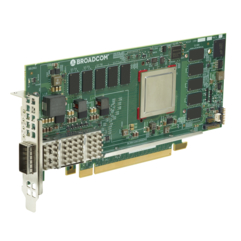

電子發(fā)燒友網(wǎng)為你提供Broadcom(ti)PS1100R - 100GBE NVMEOF PCIE STORAGE ADAPTER相關(guān)產(chǎn)品參數(shù)、數(shù)據(jù)手冊(cè),更有PS1100R - 100GBE

2019-07-04 13:17:00

電子發(fā)燒友網(wǎng)為你提供Broadcom(ti)N225P - 2 X 25/10GBE OCP 3.0 ADAPTER相關(guān)產(chǎn)品參數(shù)、數(shù)據(jù)手冊(cè),更有N225P - 2 X 25/10GBE OCP

2019-07-04 10:16:01

電子發(fā)燒友網(wǎng)為你提供Broadcom(ti)N425G - 4 X 25/10GBE OCP 3.0 ADAPTER相關(guān)產(chǎn)品參數(shù)、數(shù)據(jù)手冊(cè),更有N425G - 4 X 25/10GBE OCP

2019-07-04 10:16:01

電子發(fā)燒友網(wǎng)為你提供Broadcom(ti)N210TP - 2 X 10GBASE-T OCP 3.0 ADAPTER相關(guān)產(chǎn)品參數(shù)、數(shù)據(jù)手冊(cè),更有N210TP - 2 X 10GBASE-T

2019-07-04 10:15:01

電子發(fā)燒友網(wǎng)為你提供Broadcom(ti)N210P - 2 X 10GBE PCIE OCP 3.0 ADAPTER相關(guān)產(chǎn)品參數(shù)、數(shù)據(jù)手冊(cè),更有N210P - 2 X 10GBE PCIE

2019-07-04 10:15:01

電子發(fā)燒友網(wǎng)為你提供Broadcom(ti)N410SG - 4 X 10GBE PCIE OCP 3.0 ADAPTER相關(guān)產(chǎn)品參數(shù)、數(shù)據(jù)手冊(cè),更有N410SG - 4 X 10GBE PCIE

2019-07-04 10:15:01

電子發(fā)燒友網(wǎng)為你提供Broadcom(ti)N150G - 1 X 50GBE OCP 3.0 ADAPTER相關(guān)產(chǎn)品參數(shù)、數(shù)據(jù)手冊(cè),更有N150G - 1 X 50GBE OCP 3.0

2019-07-04 10:15:01

電子發(fā)燒友網(wǎng)為你提供Broadcom(ti)N250G - 2 X 50GBE OCP 3.0 ADAPTER相關(guān)產(chǎn)品參數(shù)、數(shù)據(jù)手冊(cè),更有N250G - 2 X 50GBE OCP 3.0

2019-07-04 10:15:01

電子發(fā)燒友網(wǎng)為你提供Broadcom(ti)N1100G - 1 X 100GBE OCP 3.0 ADAPTER相關(guān)產(chǎn)品參數(shù)、數(shù)據(jù)手冊(cè),更有N1100G - 1 X 100GBE OCP 3.0

2019-07-04 10:14:00

電子發(fā)燒友網(wǎng)為你提供Broadcom(ti)N2100G - 2 X 100GBE OCP 3.0 ADAPTER相關(guān)產(chǎn)品參數(shù)、數(shù)據(jù)手冊(cè),更有N2100G - 2 X 100GBE OCP 3.0

2019-07-04 10:13:01

SAN JOSE - Cadence設(shè)計(jì)系統(tǒng)公司的驗(yàn)證單位Quickturn已經(jīng)擴(kuò)展了其SpeedBridge產(chǎn)品系列的兩個(gè)新速率 - 支持最新PCI 64位和AGP 4X模式數(shù)據(jù)傳輸標(biāo)準(zhǔn)的適配器。

2019-08-12 14:56:43 2121

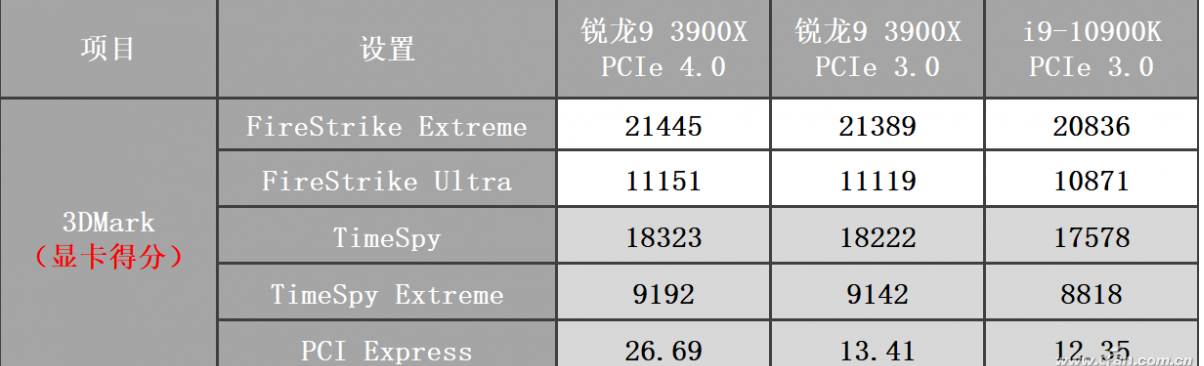

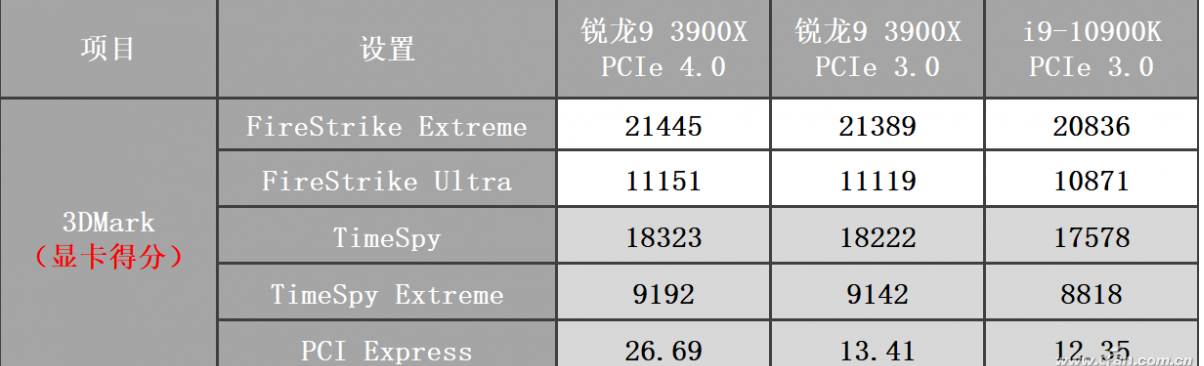

2121 在3DMark測(cè)試中,盡管PCIe 3.0(X570主板為BIOS中強(qiáng)制設(shè)置)和PCIe 4.0的實(shí)測(cè)帶寬確實(shí)差別很大,但游戲引擎的跑分差距很小。

2020-09-27 10:31:28 4767

4767

作者:Tom-M

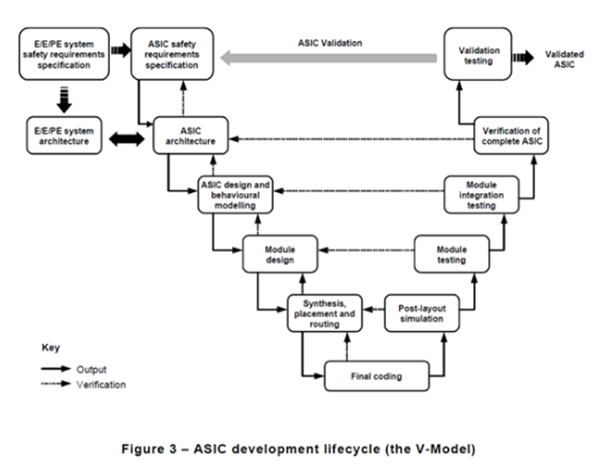

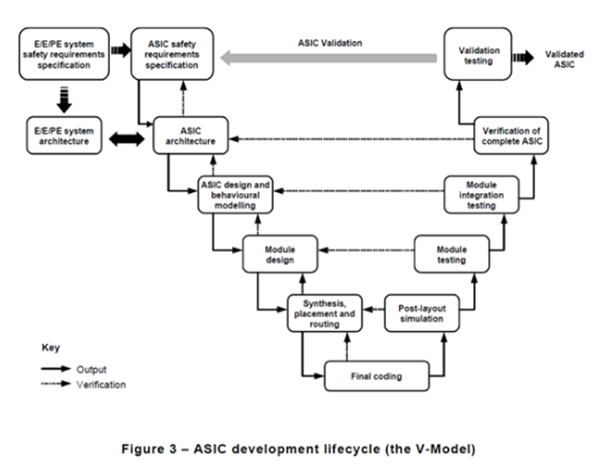

驗(yàn)證與確認(rèn)是功能安全中重要但相互獨(dú)立的兩個(gè)主題。然而,這兩個(gè)術(shù)語(yǔ)經(jīng)常被誤用和混淆,包括我最近正在閱讀的一份功能安全標(biāo)準(zhǔn)初稿。簡(jiǎn)而言之,確認(rèn)是項(xiàng)目實(shí)現(xiàn)其最終目標(biāo)的最終驗(yàn)證。

來(lái)看

2022-02-21 17:11:23 837

837

作者:Tom-M

驗(yàn)證與確認(rèn)是功能安全中重要但相互獨(dú)立的兩個(gè)主題。然而,這兩個(gè)術(shù)語(yǔ)經(jīng)常被誤用和混淆,包括我最近正在閱讀的一份功能安全標(biāo)準(zhǔn)初稿。簡(jiǎn)而言之,確認(rèn)是項(xiàng)目實(shí)現(xiàn)其最終目標(biāo)的最終驗(yàn)證。

來(lái)看

2021-01-30 06:48:51 11

11 的 PHY 和雙模(支持 RC 和 EP)控制器組成,同時(shí)我們?cè)诠栊酒?b class="flag-6" style="color: red">實(shí)現(xiàn)和驗(yàn)證了高達(dá) 8-lane 的鏈路寬度。 在過(guò)去的 PCIe 規(guī)范下,測(cè)試

2021-05-14 10:33:55 1787

1787 隨著英特爾的十一代酷睿發(fā)布,PC硬件已經(jīng)實(shí)現(xiàn)了對(duì)PCIe 4.0固態(tài)硬盤的全面支持。PCIe 4.0接口的全面普及推動(dòng)了固態(tài)硬盤提速潮,PCIe 4.0逐漸走進(jìn)了大眾的視野,成為購(gòu)買者選購(gòu)固態(tài)硬盤

2021-09-14 18:09:49 22294

22294 Cadence Safety Solution 包括新的 Midas Safety Platform,為模擬和數(shù)字流程提供基于 FMEDA 功能安全設(shè)計(jì)和驗(yàn)證的統(tǒng)一方案 該安全流程方案為汽車、工業(yè)

2021-10-26 14:24:34 4050

4050 中國(guó)上海,2021 年 10 月 22 日——楷登電子(美國(guó) Cadence 公司,NASDAQ:CDNS)宣布發(fā)布支持 TSMC N5 工藝的 PCI Express(PCIe)6.0 規(guī)范

2021-10-26 14:28:00 4024

4024 Liberate Characterization 和 Tempus 解決方案已經(jīng)通過(guò) Samsung Foundry 老化模型驗(yàn)證,使客戶能夠快速、安心地完成高可靠性的設(shè)計(jì)簽核 Tempus 解決方案的全新

2021-11-19 11:00:13 2967

2967 了。 目前來(lái)講,主流的選擇還是PCIe3.0固態(tài)硬盤,而且市面上的硬盤價(jià)格都已經(jīng)有所下降,加上對(duì)平臺(tái)的要求不高,主流電腦都能滿速運(yùn)行,所以就更討喜了。為此我們將手頭上所擁有的三款PCIe3.0固態(tài)硬盤進(jìn)行了一個(gè)橫評(píng),分別是三星970EVO 500GB、致鈦P

2021-11-22 14:48:27 4477

4477

楷登電子(美國(guó) Cadence 公司,NASDAQ:CDNS)今日宣布,SK hynix Inc. 已部署 Cadence? Spectre? FX Simulator 仿真器,用于對(duì)其面向 PC 和移動(dòng)應(yīng)用的 DDR4 和 DDR5 DRAM 進(jìn)行基于 FastSPICE 的功能驗(yàn)證。

2022-04-08 14:49:00 1565

1565 TPU建議,如果你還在使用PCIe 3.0系統(tǒng),比如Intel 10代酷睿或更早,AMD初代銳龍,就不要考慮RX 6400了,還不如上一塊RX 570 4GB,價(jià)格不貴,而且支持完整的PCIe 3.0 x16,游戲性能反而可以更好,有時(shí)候可以比RX 6400高出多達(dá)17%。

2022-05-10 14:48:14 21111

21111 楷登電子(美國(guó) Cadence 公司,NASDAQ:CDNS)今日宣布推出 15 種新的驗(yàn)證 IP(VIP)解決方案,助力工程師迅速有效地驗(yàn)證設(shè)計(jì),以滿足最新標(biāo)準(zhǔn)協(xié)議的要求。

2022-06-06 11:18:21 2665

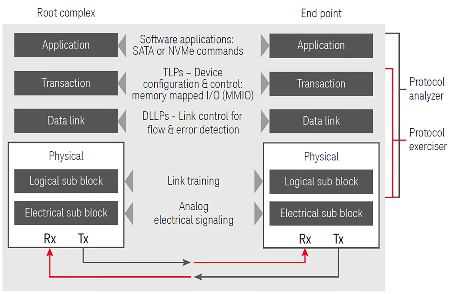

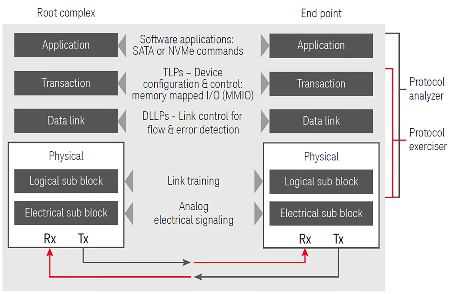

2665 在滿足所有測(cè)試以建立穩(wěn)定的通信通道后,下一步是驗(yàn)證PCIe 總線上的應(yīng)用層(例如 NVMe)。對(duì)于 NVMe 協(xié)議測(cè)試,用戶將需要一個(gè)工具來(lái)觀察不同部分的交互方式。數(shù)據(jù)鏈路層、確認(rèn)、流控制、多個(gè)隊(duì)列和多個(gè)命令需要協(xié)調(diào)。在一次 NVMe 讀取中可能需要分析數(shù)千個(gè)數(shù)據(jù)包。一個(gè)好的工具將

2022-06-19 15:44:08 1883

1883

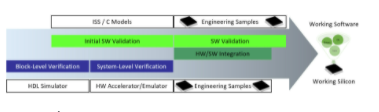

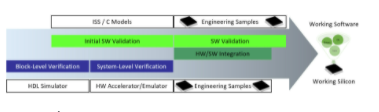

硬件仿真以前僅限于驗(yàn)證超大型設(shè)計(jì),如今已成為所有設(shè)計(jì)驗(yàn)證和確認(rèn)流程的基礎(chǔ)。這種新發(fā)現(xiàn)的流行是日益增長(zhǎng)的硅復(fù)雜性和嵌入式軟件的廣泛使用的結(jié)果。

2022-06-19 16:22:51 1824

1824

楷登電子(美國(guó) Cadence 公司,NASDAQ:CDNS)今日宣布,其面向 TSMC N7、N6 和 N5 工藝技術(shù) PCI Express?(PCIe?) 5.0 規(guī)范的 PHY 和控制器

2022-06-23 10:17:30 1464

1464 近日,Cadence Design Systems宣布,其 PHY 和控制器 IP 用于 TSMC N7、N6 和 N5 工藝中的 PCI Express? (PCIe?) 5.0 規(guī)范技術(shù)已在 4 月舉行的業(yè)界首個(gè) PCIe 5.0 規(guī)范合規(guī)性活動(dòng)中通過(guò)了 PCI-SIG? 的認(rèn)證測(cè)試。

2022-06-23 11:10:58 1405

1405 的驗(yàn)證 IP(VIP)和系統(tǒng)級(jí) VIP(系統(tǒng) VIP),以加速新技術(shù)的采用。Cadence CXL 3.0 VIP與 Cadence PCI Express(PCIe)6.0 VIP 集成,提供了從 IP 到系統(tǒng)級(jí)芯片(SoC)的完整解決方案,助力用戶成功設(shè)計(jì)高性能數(shù)據(jù)中心應(yīng)用。

2022-08-10 10:14:50 1781

1781 PCIE3.0協(xié)議分析儀U4301A,它是一塊采用了Agilent AXIe架構(gòu)的插卡,可以插在AXIe的機(jī)箱里,通過(guò)探頭來(lái)捕獲高速的PCIE 3.0信號(hào),并通過(guò)外部PC控制顯示協(xié)議分析的結(jié)果。

2022-10-12 17:33:56 1191

1191 PCIe標(biāo)準(zhǔn)自從推出以來(lái),1代和2代標(biāo)準(zhǔn)已經(jīng)在PC和Server上逐漸普及,用于滿足高速顯卡、高速存儲(chǔ)設(shè)備對(duì)于高速數(shù)據(jù)傳輸?shù)囊蟆3鲇谥С指呖偩€數(shù)據(jù)吞吐率的目的,PCI-SIG組織在2010年制定了PCIe 3.0,即PCIe 3代的規(guī)范,數(shù)據(jù)速率達(dá)到8Gbps。

2022-10-20 09:59:21 4792

4792 公告寫道,QQ Linux 3.0 版本基于 QQNT 技術(shù)架構(gòu)驅(qū)動(dòng)實(shí)現(xiàn)了全新架構(gòu),并可支持 x64 系統(tǒng)以及 arm64 系統(tǒng)。主要針對(duì)系統(tǒng)外觀、效率提升、生活?yuàn)蕵?lè)等方面功能進(jìn)行提升和拓展。

2023-01-03 11:33:18 679

679 楷登電子(美國(guó) Cadence 公司,NASDAQ:CDNS)今日宣布,瑞薩電子(Renesas Electronics)已采用全新的人工智能(AI)驅(qū)動(dòng)的 Cadence Verisium 驗(yàn)證

2023-03-15 09:07:00 539

539 Cadence LPDDR5X IP 現(xiàn)已支持客戶使用,該 IP 采用全新高性能、可擴(kuò)展的自適應(yīng)架構(gòu),并依托于 Cadence 久經(jīng)驗(yàn)證且大獲成功的 LPDDR5 和 GDDR6 產(chǎn)品線。

2023-04-21 12:46:31 1100

1100 楷登電子(美國(guó) Cadence 公司,NASDAQ:CDNS)近日宣布擴(kuò)大與臺(tái)積電和微軟的合作,致力于加快千兆級(jí)規(guī)模數(shù)字設(shè)計(jì)的物理驗(yàn)證。通過(guò)此次最新合作,客戶可以在帶有 Cadence

2023-04-26 18:05:45 710

710 了 Cadence 在面對(duì) SoC 設(shè)計(jì)驗(yàn)證挑戰(zhàn)下的應(yīng)對(duì)之法。 隨著 SoC 設(shè)計(jì)的發(fā)展,如何在有限的時(shí)間內(nèi)盡可能發(fā)現(xiàn)更多的 bug 和實(shí)現(xiàn)更多的溯源分析,讓項(xiàng)目各方面的投資都做到物盡其用,這是驗(yàn)證工作所面臨

2023-06-07 00:20:03 466

466

? 兩個(gè)在質(zhì)量管理和驗(yàn)證過(guò)程中經(jīng)常使用的術(shù)語(yǔ)。以下是它們的區(qū)別和關(guān)系,包括維基百科的定義、應(yīng)用和范圍: 驗(yàn)證(Verification):根據(jù)維基百科的定義,驗(yàn)證是一種評(píng)估活動(dòng),旨在確認(rèn)產(chǎn)品、系統(tǒng)

2023-06-19 10:59:28 3116

3116 本文翻譯轉(zhuǎn)載于:Cadence blog 作者:Arif Khan PCIe 7.0 規(guī)范起草階段持續(xù)推進(jìn),IP 支持開始 2023 年 6 月 13 日在圣克拉拉舉辦的年度開發(fā)者大會(huì)

2023-06-28 12:20:01 378

378

支持 PCIe Gen5 x 4 與 CXL(EP)的連接,以及 PCIe Gen5 x 8 與 CCIX(RC/EP)的連接。這使得它能夠以高速率 PCIe 進(jìn)行數(shù)據(jù)傳輸,滿足 PCIe 相關(guān)的驗(yàn)證或是對(duì)帶寬要求高的應(yīng)用。

2023-07-04 10:56:47 295

295 要充分發(fā)揮PCIe 4.0的優(yōu)勢(shì),需要具備兼容PCIe 4.0的主板和設(shè)備。如果你的設(shè)備只支持PCIe 3.0,那么你將無(wú)法享受到PCIe 4.0的速度和帶寬優(yōu)勢(shì)。

2023-07-18 15:10:30 18161

18161 各代 PCIe 標(biāo)準(zhǔn)之間的主要差異。 PCIe 3.0 PCIe2.0的傳輸速率為5 GT/s,但由于8b/10b編碼方案的開銷占比為20%,因此單lane的傳輸帶寬為4Gb/s。PCIe 3.0及以后

2023-07-26 08:05:01 867

867

、博士生導(dǎo)師李明發(fā)表了《數(shù)據(jù)資源的確認(rèn)、計(jì)量與披露》主旨演講,從會(huì)計(jì)角度解讀了數(shù)據(jù)資產(chǎn)入表必需重視的制度基礎(chǔ)背景,數(shù)據(jù)資源的會(huì)計(jì)確認(rèn)、計(jì)量與披露中的政策要求和實(shí)踐難點(diǎn)。 以下為演講實(shí)錄 0 1 必需重視的制度基礎(chǔ)背景 會(huì)計(jì)反映的基

2023-09-14 16:10:02 1508

1508 電子設(shè)計(jì)自動(dòng)化領(lǐng)域領(lǐng)先的供應(yīng)商 Cadence,誠(chéng)邀您參加 “ 2023 Cadence 中國(guó)技術(shù)巡回研討會(huì)”。會(huì)議將集聚 Cadence 的開發(fā)者與資深技術(shù)專家,與您分享系統(tǒng)驗(yàn)證及 IC 驗(yàn)證

2023-09-21 17:20:02 339

339

電子設(shè)計(jì)自動(dòng)化領(lǐng)域領(lǐng)先的供應(yīng)商 Cadence,誠(chéng)邀您參加“2023 Cadence 中國(guó)技術(shù)巡回研討會(huì)”。會(huì)議將集聚 Cadence 的開發(fā)者與資深技術(shù)專家,與您分享系統(tǒng)驗(yàn)證及 IC 驗(yàn)證解決方案

2023-10-23 11:55:02 287

287

電子設(shè)計(jì)自動(dòng)化領(lǐng)域領(lǐng)先的供應(yīng)商 Cadence,誠(chéng)邀您參加“2023 Cadence 中國(guó)技術(shù)巡回研討會(huì)”。會(huì)議將集聚 Cadence 的開發(fā)者與資深技術(shù)專家,與您分享系統(tǒng)驗(yàn)證及 IC 驗(yàn)證解決方案

2023-10-25 10:40:02 190

190

多路PCIe3.0的單CPU通用工作站

2023-11-23 09:38:33 157

157

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論